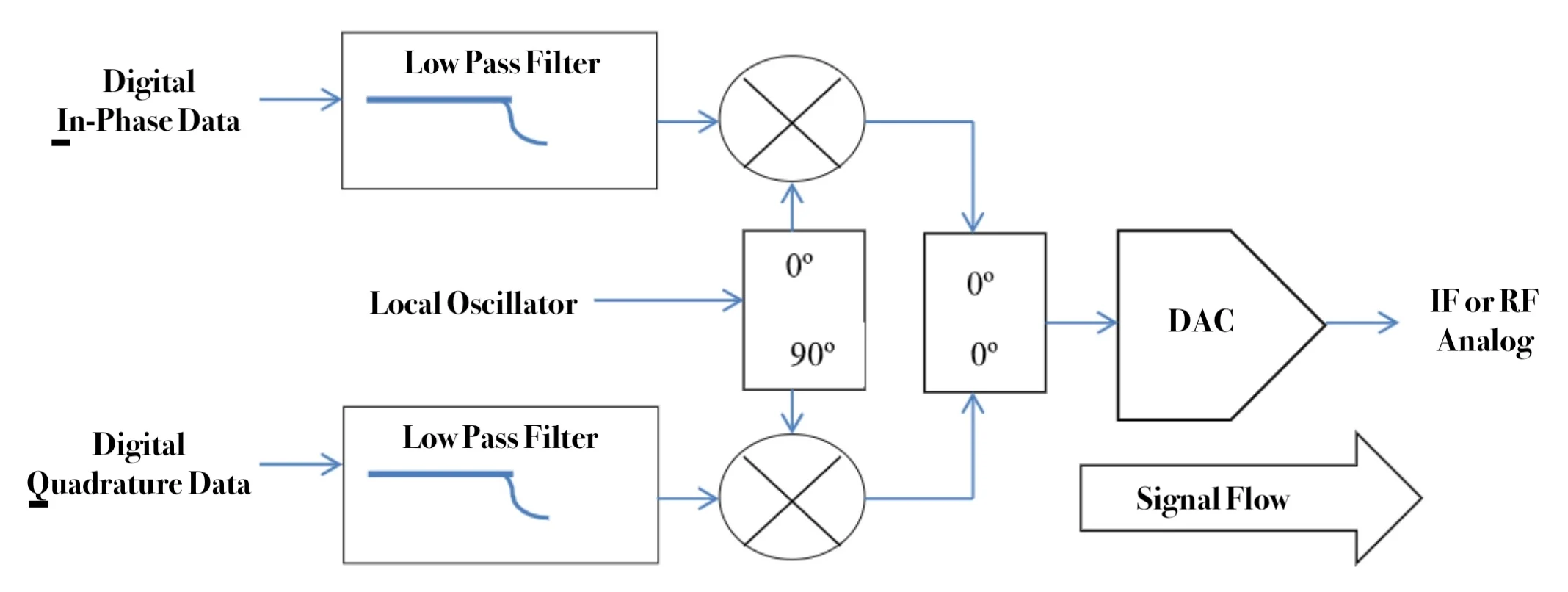

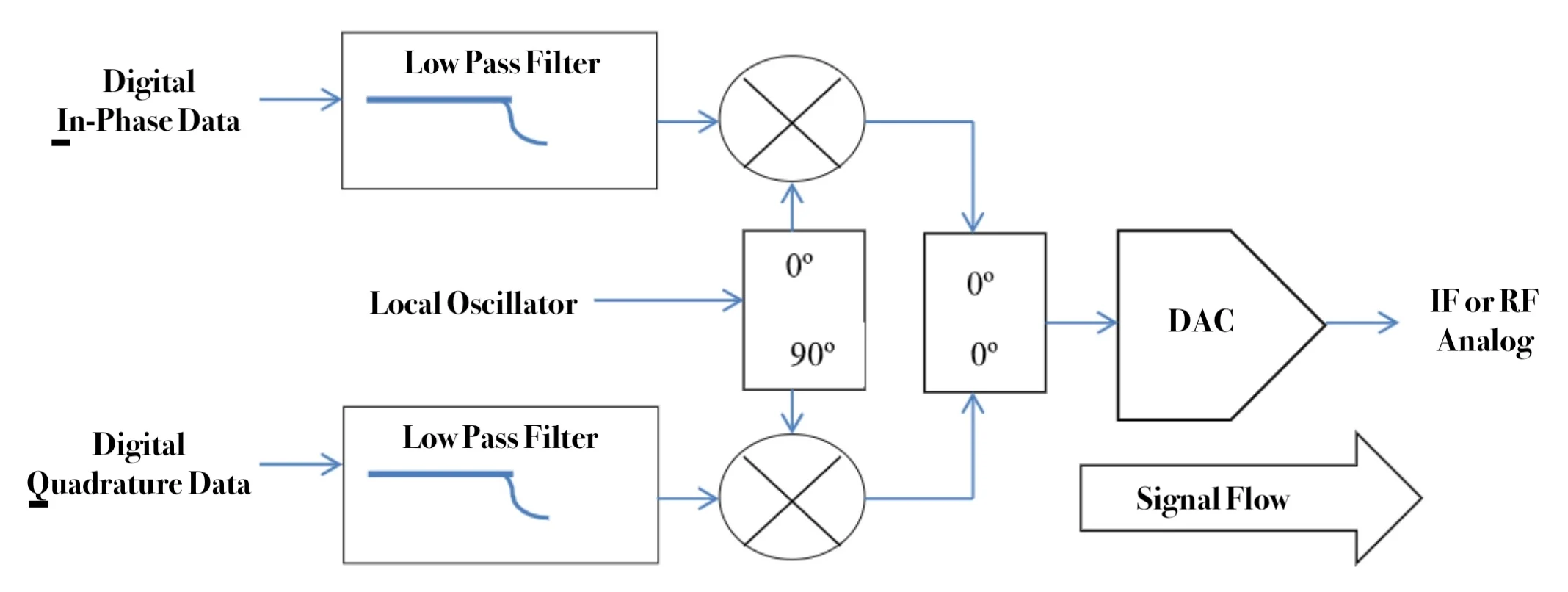

篇文章中的图 1 显示了直接射频数模转换和直接射频模数转换选项。(请注意,数模转换器 {DAC} 和模数转换器 {ADC} 统称为“数据转换器”。)

图1(a)。 调制器

图 1(b)。

解调器 在那篇文章中,您的作者想知道的一件事是:为了获得良好的通信链路性能,图 1 中的 DAC 和 ADC 的质量要求是什么?关于这个问题似乎没有太多发表。

这让他想知道,如果他要模拟通信链路中的数据转换器,应该如何建模?

对于误码率 (BER) 模拟,将发现的误码数除以总位数来计算 BER。对于统计上显着的结果,应该计算数百到一千个错误。即使 BER 相当高(10-4);计算 500 个错误需要 500 万位。为了使仿真在合理的短时间内运行,必须找到一个相当简单的模型,该模型能够充分捕获所有相关的数据转换器特性。

这篇文章描述了他找到的信息。将讨论分为有关 ADC 和 DAC 的讨论很有用。.02 版添加注释;本文不考虑 Sigma-Delta 型数据转换器。

模数转换器 (ADC) 模型

下面的参考文献 [4] 至 [18] 讨论了 ADC 的分析、模型、仿真、测试和规范。特别是[13]、[14]、[16]和[17]提出了对 ADC 性能某些方面进行建模的模型。作为一名工程师,作者想知道是否可以建立一个更简单、更容易理解的模型。

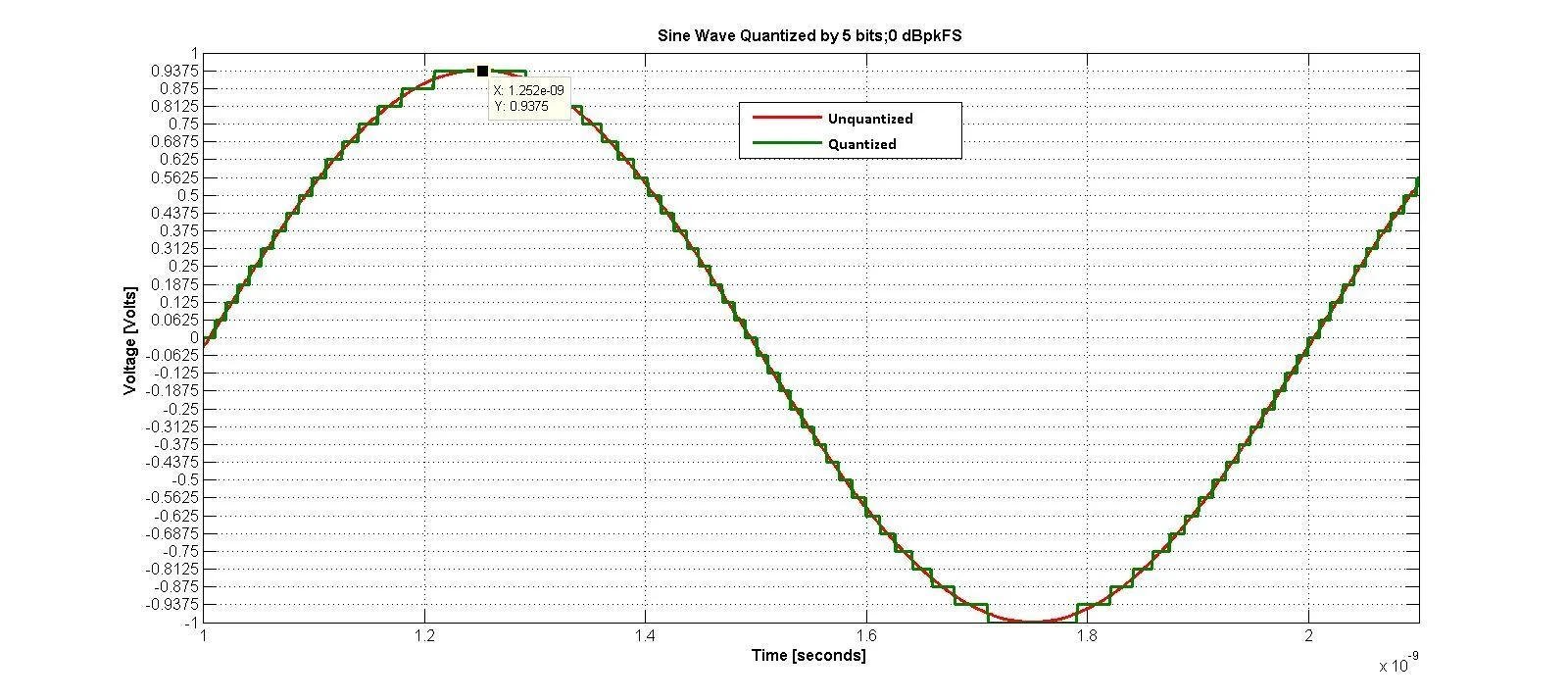

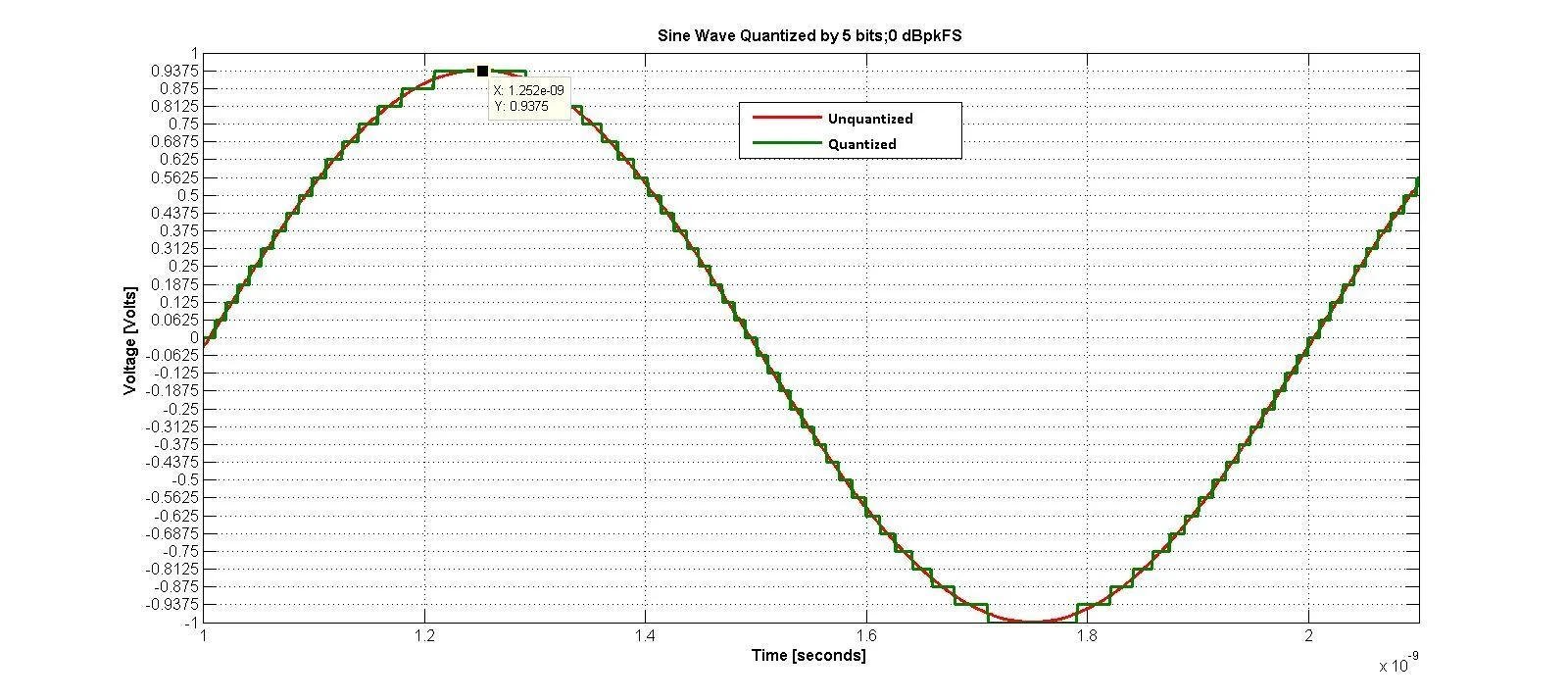

图 2 显示了 5 位 ADC 的量化。有 2 5 = 32 级。由于输入可以是正的,也可以是负的,所以这被称为双极性输入ADC。您的作者想知道的一个方面是峰值信号和平均信号之间相对于满量程 (FS) 的 dB 之间的差异。

图 2.

图 2 中信号的峰值电压介于 +0.9375 伏 (FS+) 和 -1 伏 (FS-) 之间;这是±1伏的一个很好的近似值。

射频工程师习惯于处理信号的有效值。正弦波的均方根值为 0.707 伏,相对于 FS 为 - 3 dB。由于这在过去让您的作者感到困惑,因此他选择定义单位 dBpeakFS(信号相对于满量程的电压峰值的 dB)和 dBrmsFS(信号相对于满量程的 rms 值的 dB)。

另一个问题涉及有人关心的 ADC 输出带宽。对于 ADC 的早期音频应用,人们通常关心完整的奈奎斯特带宽。

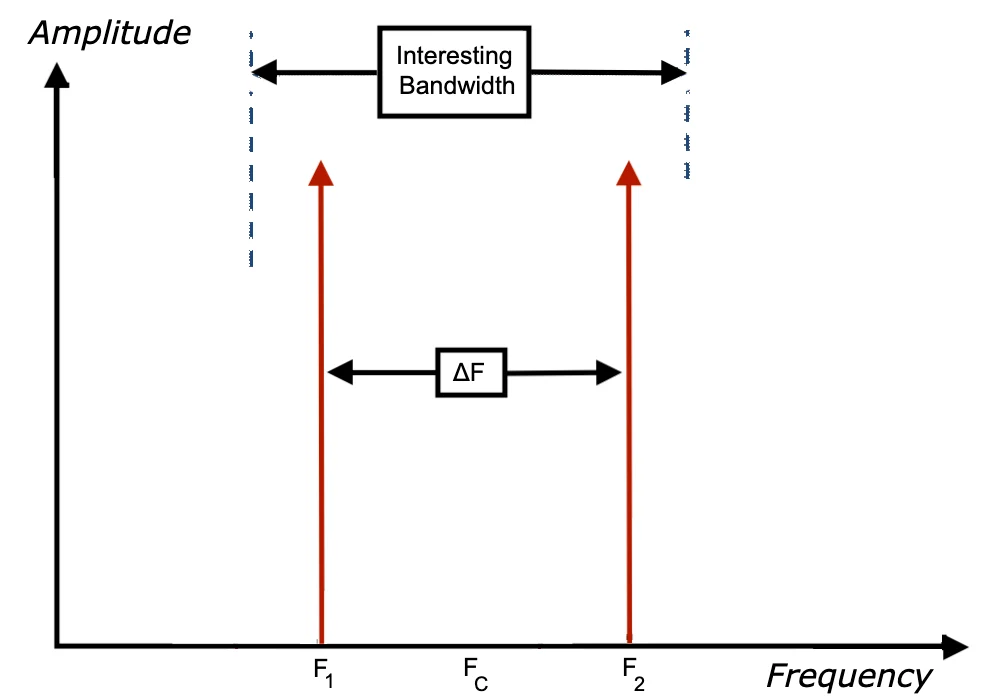

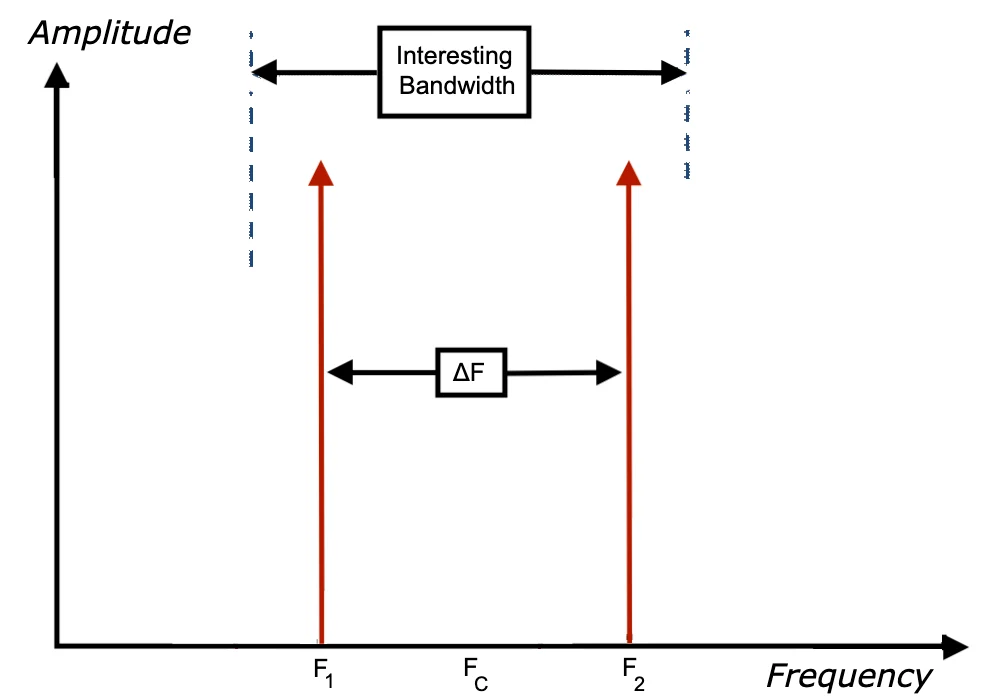

然而,对于如图 1(b) 所示的直接 RF 采样,仅需要关注信号占用的奈奎斯特频带部分以及少量保护频带。这导致作者定义了“有趣的带宽”,如图 3 所示。

“感兴趣的带宽”是由数字信号处理(DSP)处理的带宽。它通常是所需的信号带宽或更宽一些。

图 3.

请注意,在图 3 中,虽然信号和“感兴趣”的带宽显示相同,但??两者的中心频率却不同。这可能是由于我们篇文章中描述的带通采样所致,其中 ADC 时钟充当混频器的本地

振荡器。ADC 时钟的频率用 fS 表示。奈奎斯特频率 = F奈奎斯特= f S / 2。

选择用于实现模型的输入信号

为了表征 ADC 以创建良好的模型,有必要定义有用的输入信号。大多数 ADC 规格都是使用单个正弦波输入创建的。然而,由于其带宽为 0 Hz 并且没有包络变化,因此它看起来并不是一个非常好的信号。如图 4 所示,2 音输入具有超过 0 Hz 的带宽并且具有幅度变化。使用两个高质量信号源和正确的功率组合可以在测试台上轻松生成。此外,大多数数据表都包含一些有关 2 音输入设备性能的信息。

图 4.

[4]和[12]中还提出了双音测试信号。已提出的其他测试信号包括具有任意频谱形状的高斯输入 [17] 以及 AM 或 FM 信号 [5]。通常,这些需要不太常见的

信号发生器,并且通常不会在数据表中显示为测试输入。