将 SAR ADC 与电容式 DAC 耦合是一种流行的方法,可实现 5G 无线接收器所需的中等分辨率和速度的高能效转换。结合流水线、交错和数字校准等技术,已经展示了精度高达 12 位 ENOB(有效位数)和数百 MHz 速度的混合 ADC。凭借这些特性,这些 ADC 可以提供 5G 应用所需的吞吐量。

虽然 ADC 本身非常节能,但它也对其周围的电路提出了严格的限制,尤其是在涉及参考电压时。事实上,DAC 从参考中汲取与信号相关的电荷——这是所有实现电容式 DAC 的逐次逼近寄存器 (SAR) ADC 的共同特征。如果不采取措施来稳定该参考电压,就会产生参考电压的信号相关调制,这会在 ADC 输出端表现为谐波失真。

传统的解决方案包括以面积和/或功率为代价添加更多的片上去耦电容或高速参考

缓冲器。

从参考中汲取的与信号相关的电荷完全由特定的 DAC 拓扑决定。因此,它是可预测的,并且可以通过用另一个消除参考电压纹波的信号相关电荷来消除信号相关电荷来稳定参考。基于在其交错流水线 SAR ADC 中使用辅助 DAC,Imec 现在已经成功地实施了这种参考稳定技术。

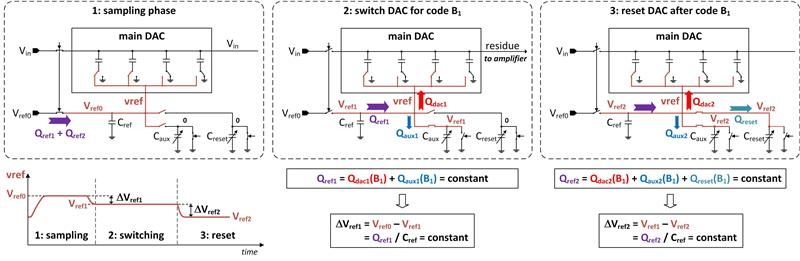

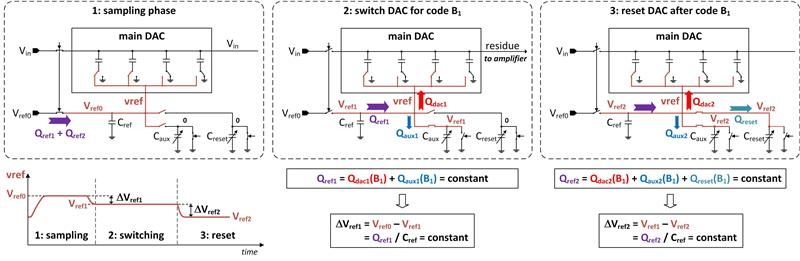

图 1电容参考稳定的基本原理图 1显示了这种稳定技术的基本概念。当输入信号被采样到主 DAC 时,参考电压也被采样到参考

电容器 Cref,同时辅助 DAC Caux 被放电(步骤 1)。当主 DAC 然后根据代码 B1 切换以生成残差时,辅助 DAC 的代码相关数量的单元也连接到参考节点(步骤 2)。通过为每个代码 B1 选择合适的 Caux 大小,可以使主 DAC 和辅助 DAC 汲取的电荷总和保持恒定。参考电压下降,但下降现在与信号无关。

,主 DAC 重置为原始状态。此操作还从参考中提取与信号相关的电荷。通过对第二个辅助 DAC Creset 使用相同的稳定技术,第二个参考电压降也变得与信号无关(步骤 3)。参考缓冲器现在只需为 Cref 充电恒定数量的电荷,这大大放宽了其带宽要求。

图 2描绘了实现上述稳定技术的 2× 交错流水线 SAR ADC 的示意图。在这个架构中,关键的残差是阶段生成的一个残差。因此,仅当主 DAC 生成此残差时才应用稳定技术。该 DAC 使用 2 个子 DAC 用于正输入和负输入范围,这减少了

开关能量,但也导致代码 B1 非常非线性映射到辅助 DAC Caux 的正确设置,以消除电荷的信号依赖性由主 DAC 绘制。

6 位编码 B1 由小型粗 SAR 量化器确定,它只需要 6 位线性度,因此对其参考没有严格的条件。查找表 (LUT) 将代码 B1 映射到辅助 DAC 的正确设置。然后,主 DAC 与辅助 DAC Caux 一起切换到参考节点。残差放大后,主 DAC 复位,辅助 DAC Creset 连接到参考节点,如上文所述。放大后的残差由第二级进一步量化,以达到整体 14 位量化级别。

交错流水线 SAR ADC图 2 2×交错流水线 SAR ADC 示意图LUT 与粗略 SAR 量化器同时处理,以大大减少关键时序路径。为了填充 LUT,具有内置偏移的比较器将终参考电压与标称值 Vref0 进行比较,校准引擎根据代码 B1 调整 Caux 设置。Creset 的设置很接近分段线性解码器。

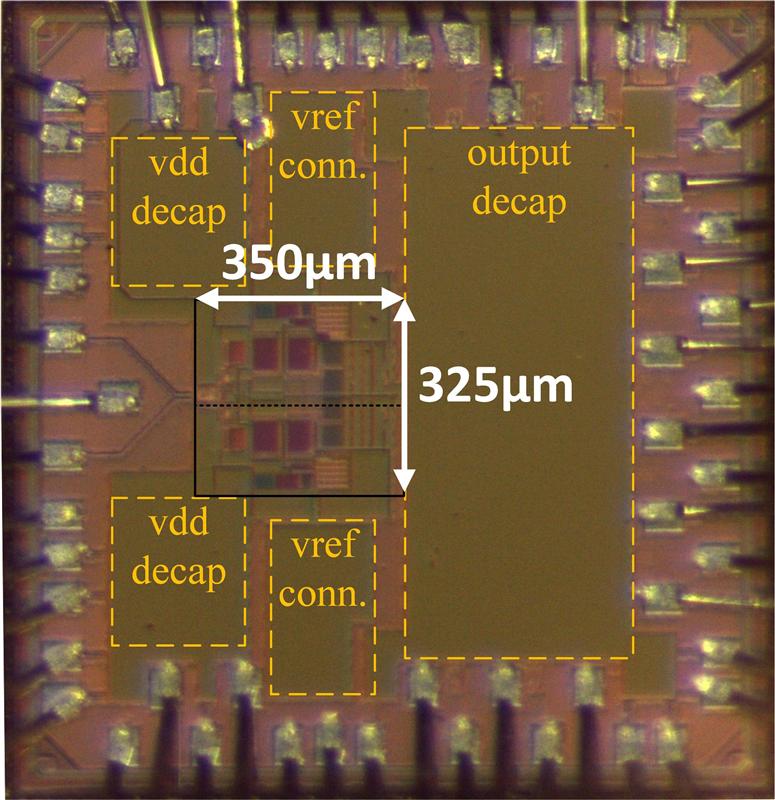

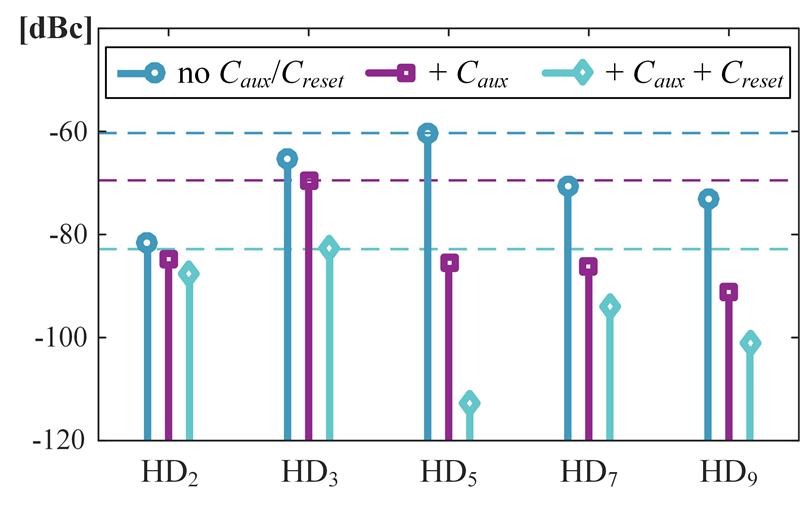

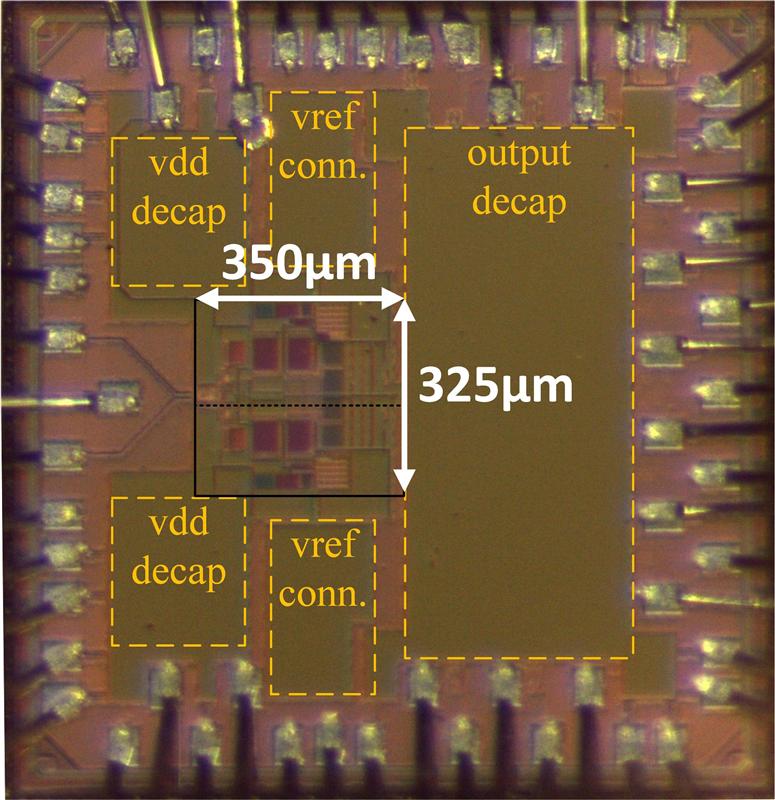

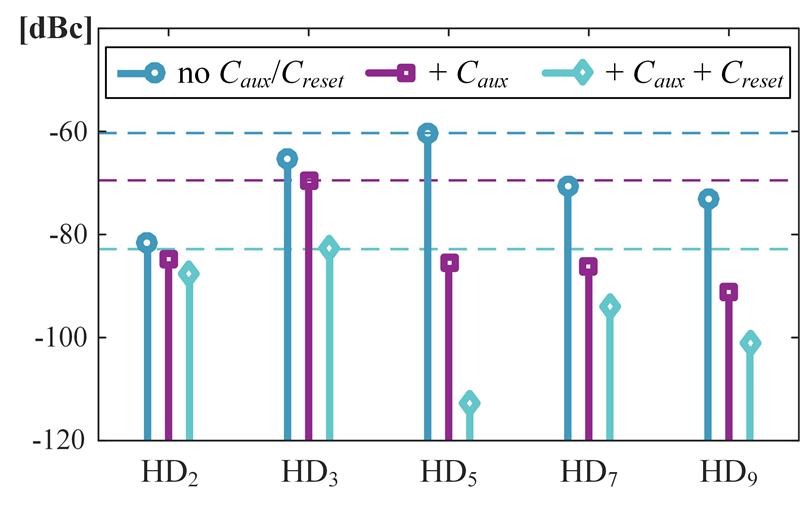

芯片显微照片测试芯片已采用 16 纳米 FinFET 技术制造。区域为 350×325 μm 2,其中 16% 用于参考稳定方案,包括 50pF 的 Cref。图 4显示了使用电容稳定技术测得的谐波减少量。对于高速运行,Caux 和 Creset 都显着提高了 SFDR(无杂散动态范围),并且杂散被抑制到 80 dBFS 以下。在 303 MS/s 时,SNDR(信噪比加失真率)在低频和奈奎斯特输入下分别为 64.0 dB 和 69.3 dB。功率仅为 3.6 mW,导致的 Walden 和 Schreier FoM 分别为 9.2 fJ/conv.-step 和 170.2 dB,如图 5所示。

图 4使用辅助 DAC 减少杂散ADC 与不同的架构图 5 ADC 与不同架构的比较这些结果表明,可以通过使用辅助 DAC 来稳定参考电压,这些 DAC 可以消除由于 SAR ADC 中的 DAC 切换而导致的参考电压的信号相关压降。当 DAC 重置时也应用时,参考节点上的负载与信号无关,这显着降低了对参考缓冲器和/或片上去耦电容的要求。