随着对要求的不同提高,全差分信号链组件因出色的性能脱颖而出,这类组件的一个主要优点是可通过信号路由拾取噪声抑制。由于输出会拾取这种噪声,输出经常会出现误差并因而在信号链中进一步衰减。此外,差分信号可以实现两倍于同一电源上的单端信号的信号范围。因此,全差分信号的信噪比(SNR)更高。经典的三运放仪表

放大器具有许多优点,包括共模信号抑制、高输入阻抗和(可调)增益;但是,在需要全差分输出信号时,它就无能为力了。人们已经使用一些方法,用标准组件实现全差分仪表放大器。但是,它们有着各自的缺点。

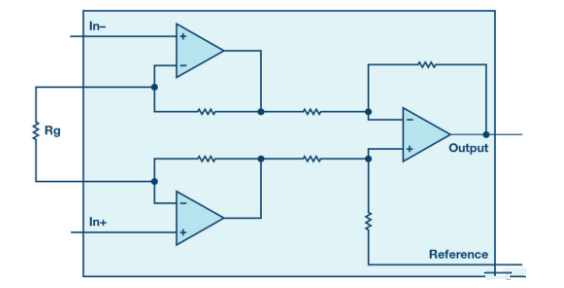

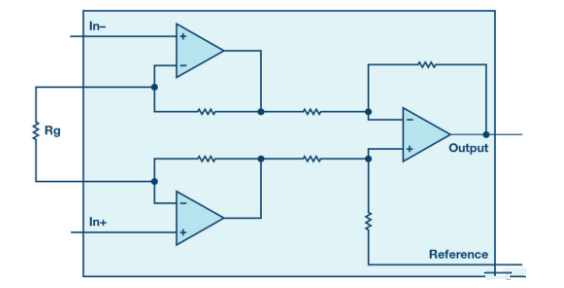

图1.经典仪表放大器。

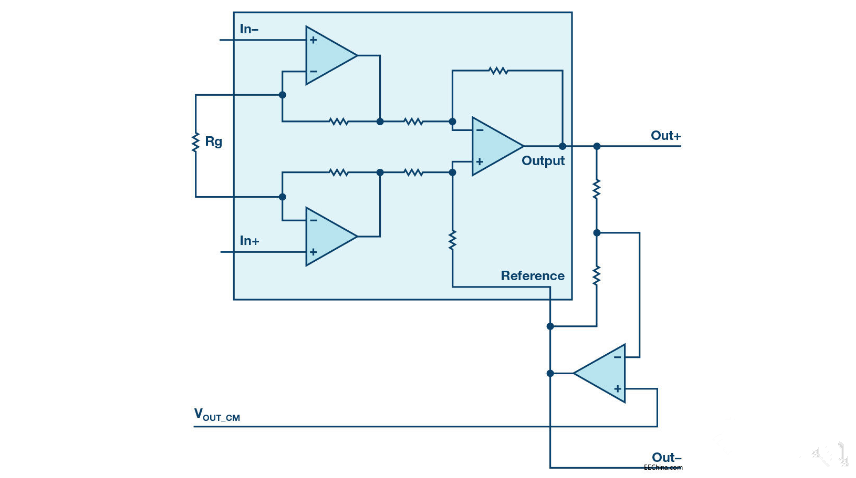

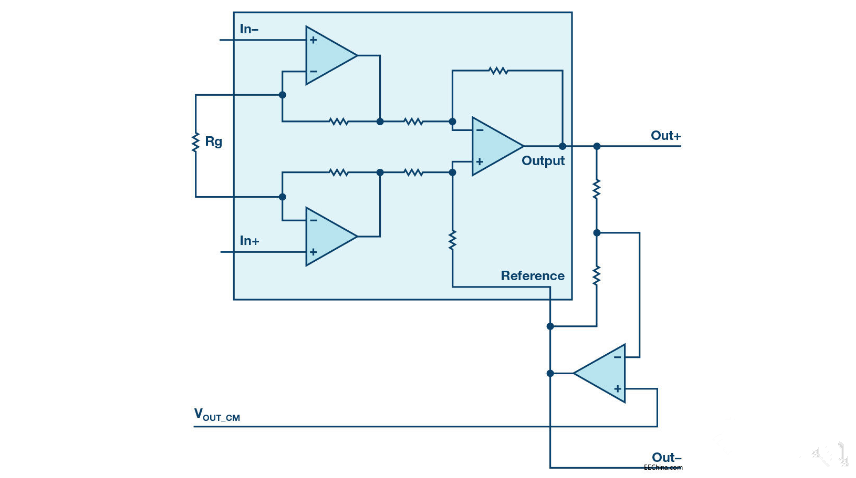

一种技术是使用

运算放大器驱动参考引脚,正输入为共模,负输入为将输出连接在一起的两个匹配电阻的中心。该配置使用仪表放大器输出作为正输出,运算放大器输出作为负输出。由于两个输出是不同的放大器,因此这些放大器之间动态性能的失配会极大地影响电路的整体性能。此外,两个电阻的匹配导致输出共模随输出信号运动,结果可能导致失真。在设计该电路时,在选择放大器时必须考虑稳定性,并且可能需要在运算放大器上设置一个反馈电容,用于限制电路的总带宽。,该电路的增益范围取决于仪表放大器。因此,不可能实现小于1的增益。

图2.使用外部运算放大器生成反相输出。

另一种技术是将两个仪表放大器与输入

开关并联。与前一电路相比,这种配置具有更好的匹配驱动电路和频率响应。但它不能实现小于2的增益。该电路还需要精密匹配增益电阻,以实现纯差分信号。这些电阻的失配会导致输出共模电平的变化,其影响与先前的架构相同。通过交叉连接两个仪表放大器,这种新电路使用单个增益电阻提供具有精密增益或衰减的全差分输出。通过将两个参考引脚连接在一起,用户可以根据需要调整输出共模。

In_A的增益由以下等式推出。由于输入电压出现在仪表放大器2的输入缓冲器的正

端子上,而电阻R2和R3另一端的电压为0 V,因此这些缓冲器的增益遵循适用于同相运算放大器配置的等式。同样,对于仪表放大器1的输入缓冲器,增益遵循反相运算放大器配置。由于

差分放大器中的所有电阻都匹配,因此缓冲器输出的增益为1。