将DDC功能集成至RF ADC中便不需要额外的模拟下变频级, 并允许RF频率域中的频谱直接向下变频至基带进行处理。RF ADC处理GHz频率域中频谱的能力放宽了模拟域中进行多次下变频的要求。DDC的这种功能使频谱得以保留,同时允许通过抽取滤波进行过滤,这样还能提供改善带内动态范围 (增加SNR)的优势。有关该话题的更详细讨论可参见:"祖父时代的ADC已成往事," 以及"千兆采样ADC确保直接RF变频." 这些文章进一步讨论了 AD9680和 AD9625,以及它们的DDC功能。

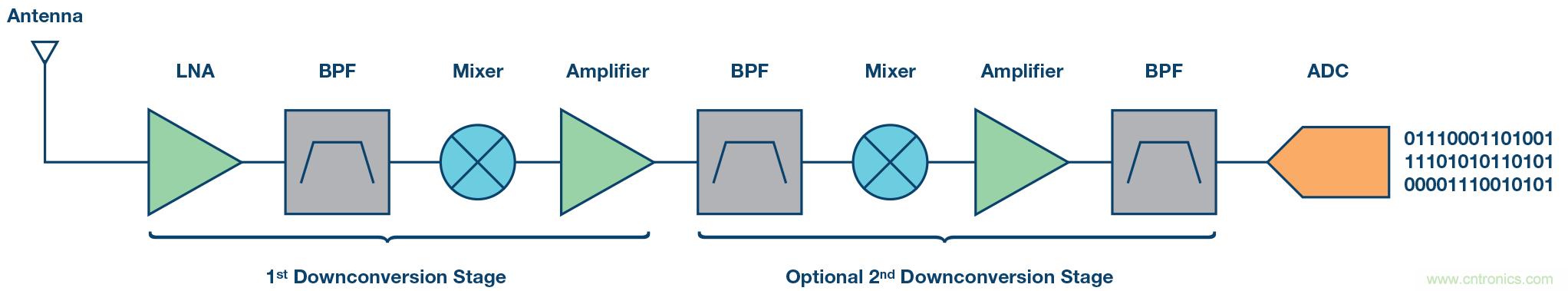

图2. 使用RF ADC(集成DDC)的接收器信号链

本文主要关注AD9680(以及 AD9690, AD9691 和 AD9684)中的DDC功能。为了理解DDC功能,并了解当ADC中集成了DDC时如何分析输出频谱,我们将以AD9680-500为例。ADI 网站上的折折频工具将作为辅助工具使用。这款使用简单但功能强大的工具可用来帮助理解ADC的混叠效应,这是分析集成了DDC的RF ADC(比如AD9680)中输出频谱的步。

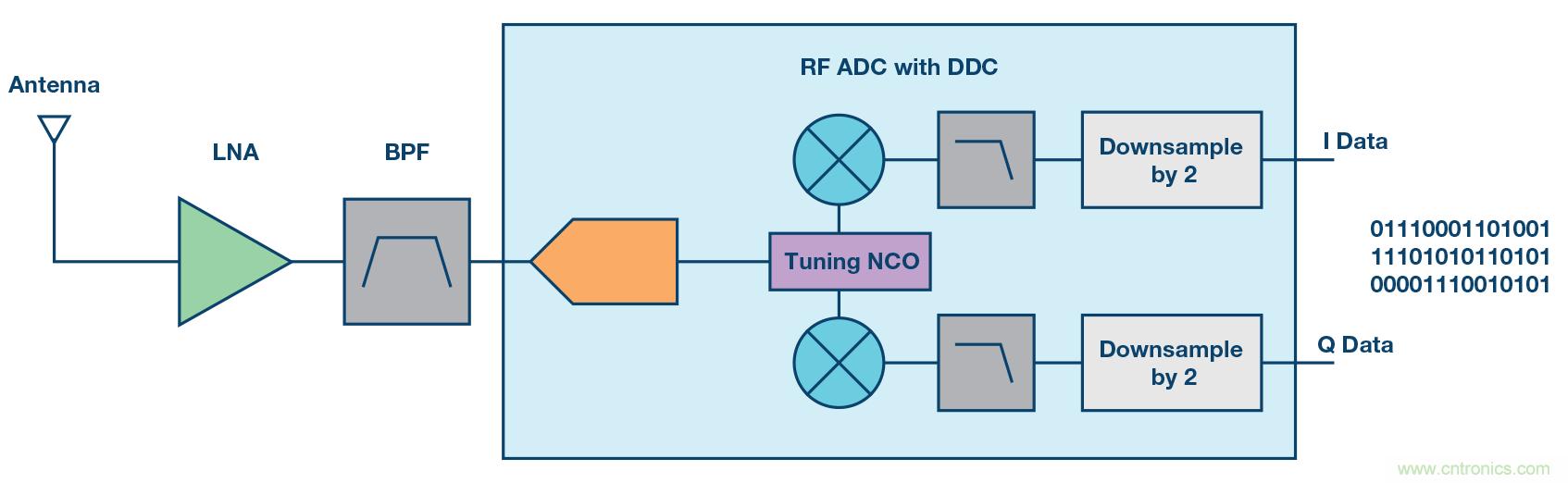

本例中,AD9680-500工作时的输入时钟为368.64 MHz,模拟输入频率为270 MHz。首先,理解AD9680中数字处理模块的设置很重要。AD9680将设为使用数字下变频器(DDC),其输入为实数,输出为复数,数控振荡器(NCO)调谐频率设为98 MHz,半带滤波器1 (HB1)使能,6dB增益使能。由于输出是复数,因此复数转实数模块禁用。DDC的基本原理图如下所示。以下内容对于了解如何处理输入信号音很重要:信号首先通过NCO,使输入信号音的频率偏移,然后通过抽取模块,并可选择性通过增益模块,之后再选择性通过复数转实数模块。

图3. AD9680中的DDC信号处理模块

从宏观上把握信号流过AD9680也很重要。信号进入模拟输入,通过ADC内核,进入DDC,通过JESD204B串行器,然后通过JESD204B串行输出通道输出。可以参见图4中的AD9680功能框图。

图4. AD9680功能框图

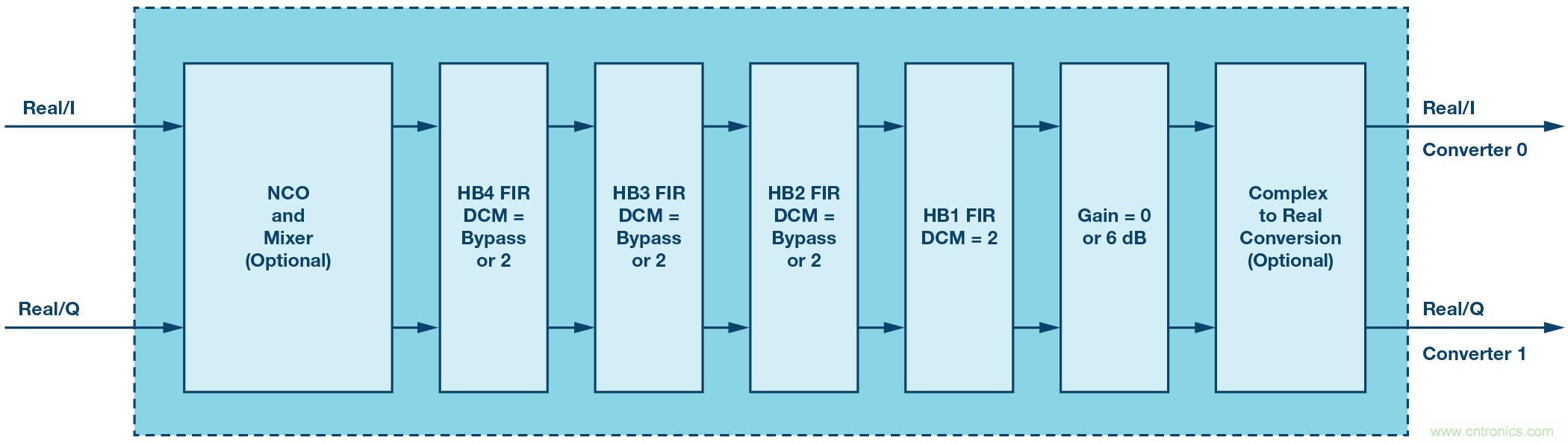

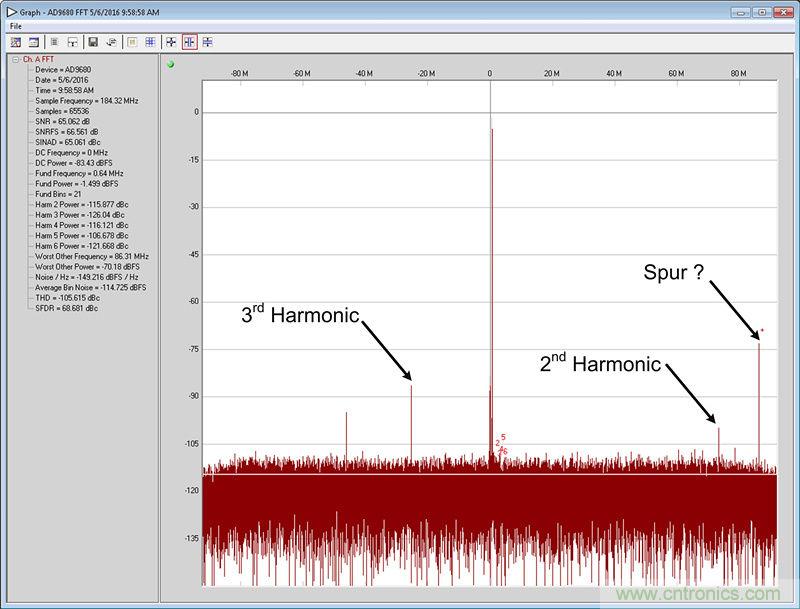

输入采样时钟为368.64 MHz,模拟输入频率为270 MHz,因此输入信号将混叠进入位于98.64 MHz处的奈奎斯特区。输入频率的二次谐波将混叠进入171.36 MHz处的奈奎斯特区,而三次谐波混叠至72.72 MHz。这可以从图5中折频工具曲线看出。

图5. 折频工具中的ADC输出频谱

图5中显示的折频工具曲线给出了信号通过AD9680中的DDC 之前,位于ADC内核输出端的信号状态。信号通过AD9680中的个处理模块是NCO,它会将频谱在频域中向左偏移98 MHz(记住调谐频率是98 MHz)。这会将模拟输入从98.64 MHz下移至0.64 MHz,二次谐波将下移至73.36 MHz,而三次谐波将下移至–25.28 MHz(记住我们观察的是复数输出)。这可以从Visual Analog的FFT曲线中看出,如下文图6所示。

图6. 经过DDC后的FFT复数输出(NCO = 98 MHz,2倍抽取)

从图6中的FFT曲线中可以清楚地看到NCO如何偏移我们在折频工具中观察到的频率。有意思的是,我们可以在FFT中看到一个未经表达的信号音。然而,这个信号音真的没有经过表达吗?NCO并不偏移所有频率。本例中,它将98 MHz的基频输入信号音混叠向下偏移至0.64 MHz,并将二次谐波偏移至73.36 MHz,将三次谐波偏移至–25.28 MHz。此外,还有另一个信号音也发生了偏移,并出现在86.32 MHz。这个信号音的来源是哪里?它是否由于DDC或ADC的信号处理而产生的?答案是:对,也不对。

让我们更加细致地看一下这个场景。折频工具不包含ADC的直流失调。该直流失调导致直流(或0 Hz)处存在信号音。折频工具假设ADC是理想器件,无直流失调。在AD9680的实际输出中,0Hz处的直流失调信号音向下偏移至–98 MHz。由于复数混频和抽取,直流失调信号音折回实数频域中的奈奎斯特区。对于信号音偏移进入第二奈奎斯特区的复数输入信号而言,它将会绕回至实数频域中的奈奎斯特区。由于使能了抽取,并且抽取率等于2,我们的抽取奈奎斯特区宽度为92.16 MHz(回忆一下:fs = 368.64 MHz,抽取采样速率为184.32 MHz,奈奎斯特区为92.16 MHz)。直流失调信号音偏移至–98 MHz,为92.16 MHz奈奎斯特区边界以外5.84 MHz。当该信号音绕回至奈奎斯特区时,它的失调和实数频域中的奈奎斯特区边界相同,即92.16 MHz – 5.84 MHz = 86.32 MHz。这正是我们在上文FFT曲线中看到的信号音!因此,技术上而言,ADC产生信号(因为它是直流失调),而DDC略微移动它。这时候就需要进行良好的频率规划。适当的频率规划有助于避免此类情形。

现在,我们讨论了一个使用NCO和HB1滤波器的示例,其抽取率等于2;让我们在这个示例中再加入一点东西。现在,我们将增加DDC抽取率,以便观察频率折叠效应以及采用较高抽取率和NCO频率调谐时的转换情况。

本例中,我们观察采用491.52 MHz输入时钟和150.1 MHz模拟输入频率的AD9680-500工作情况。AD9680将设为使用数字下变频器(DDC),并采用实数输入、复数输出、NCO调谐频率为155 MHz、半带滤波器1(HB1)和半带滤波器2(HB2)使能(总抽取率等于4)、6 dB增益使能。由于输出是复数,因此复数转实数模块禁用。回顾图3中的DDC基本原理图,该图表示信号流过DDC。同样,信号首先通过NCO,偏移输入信号音的频率,然后通过抽取、增益模块,以及在本例中旁路复数转实数模块。

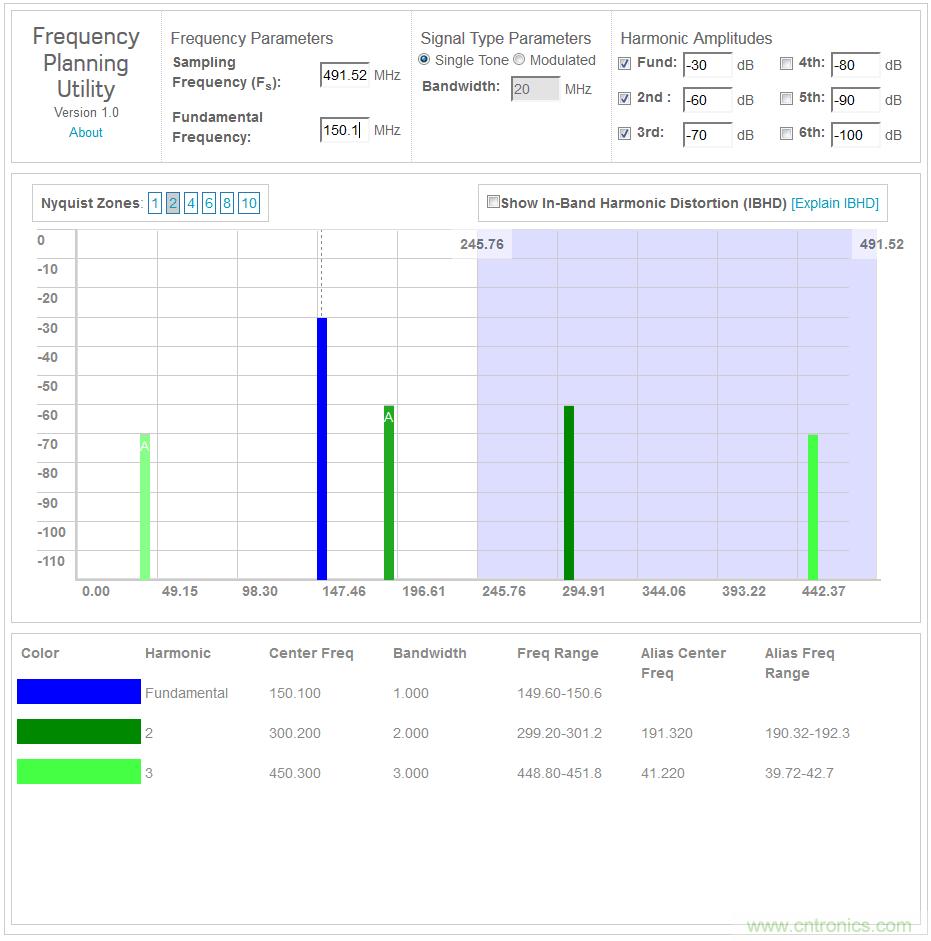

我们将再次使用折频工具 来帮助理解ADC的混叠效应,以便评估模拟输入频率和谐波在频域中的位置。本例中,我们有个实数信号,采样速率为491.52 MSPS,抽取率设为4,输出复数。在ADC的输出端,采用折频工具显示的信号如图7所示。

图7. 折频工具中的ADC输出频谱

输入采样时钟为491.52 MHz,模拟输入频率为150.1 MHz,因此输入信号将残留在奈奎斯特区。位于300.2 MHz的输入频率二次谐波将混叠进入191.32 MHz处的奈奎斯特区, 而450.3 MHz处的三次谐波混叠进入41.22 MHz处的奈奎斯特区。这是信号通过DDC之前ADC输出端上的信号状态。

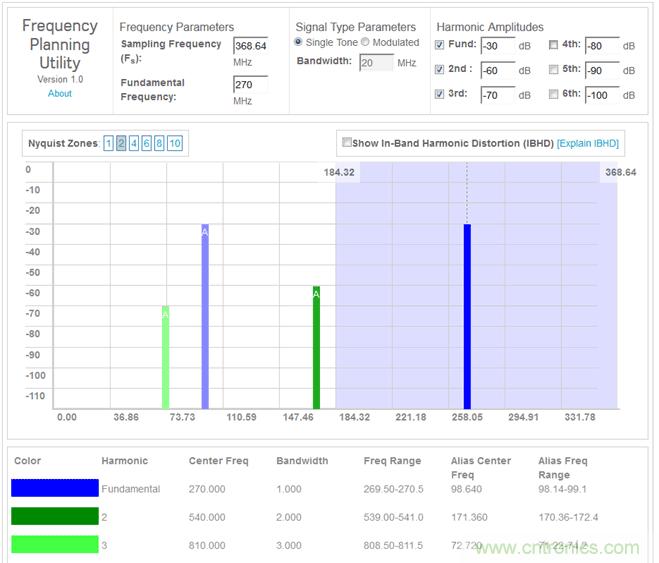

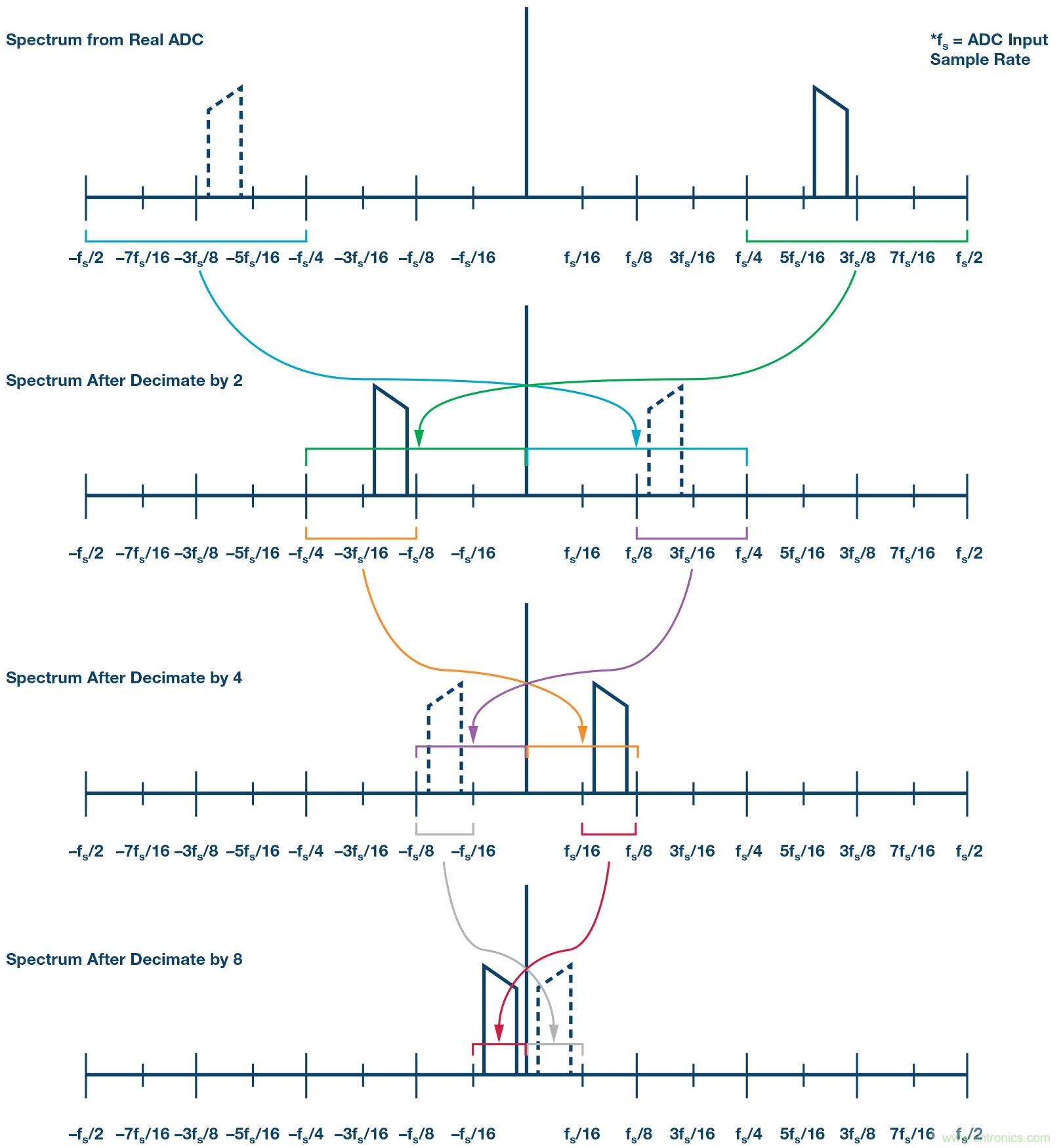

现在,让我们看一下信号如何通过DDC内部的数字处理模块。我们将查看进入每的信号,并观察NCO如何偏移信号,而抽取过程随后又是如何折叠信号的。我们将保持曲线的输入采样速率(491.52 MSPS),fs项与此采样速率有关。让我们观察一般过程,如图8所示。NCO将向左偏移输入信号。一旦复数(负频率)域中的信号偏移超过–fs/2,就会折回奈奎斯特区。接下来,信号通过抽取滤波器HB1,抽取率为2。在图中显示了抽取过程,但没有显示滤波器响应,虽然这两个操作是同时发生的。这是为了简单起见。完成第 2倍抽取之后,fs/4至fs/2的频谱转换为–fs/4至DC的频率。类似地,–fs/2至–fs/4的频谱转换为DC至fs/4的频率。信号现在通过第二抽取滤波器HB2,它也是2倍抽取(总抽取现在等于 4)。fs/8至fs/4的频谱将转换为–fs/8至DC的频率。类似地,– fs/4至–fs/8的频谱将转换为DC至fs/8的频率。虽然图中显示了抽取,但没有显示抽取滤波操作。

图8. 抽取滤波器对ADC输出频谱的影响—一般示例

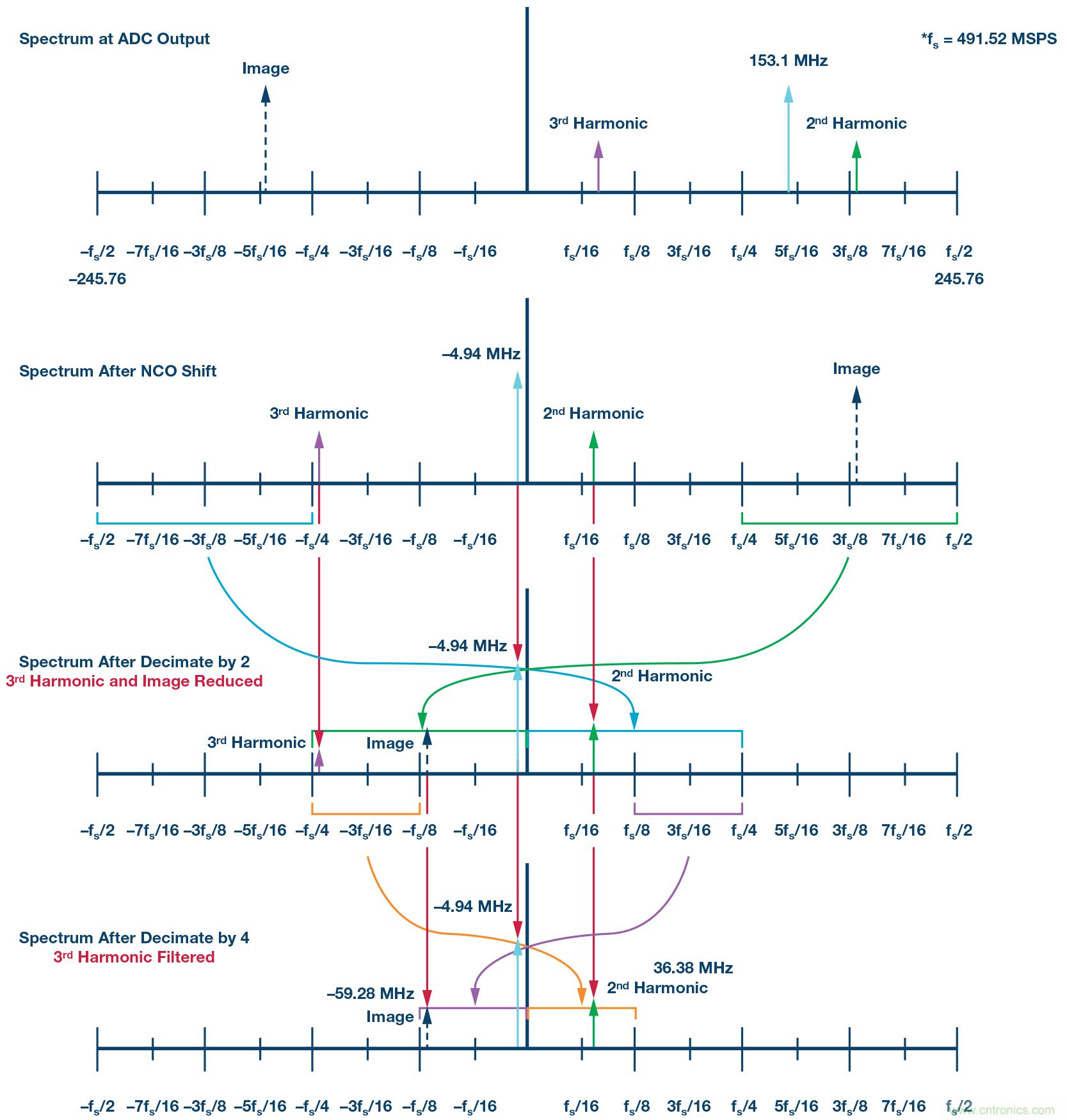

记得上一个示例中,我们讨论了491.52 MSPS输入采样速率以及150.1 MHz输入频率。NCO频率为155 MHz,抽取率等于4(由于NCO分辨率,实际NCO频率为154.94 MHz)。因此,输出采样速率为122.88 MSPS。由于AD9680配置为复数混频,我们需要在分析中包含复数频率域。图9显示了频率转换非常繁忙,但如果仔细研究的话可以看到信号流。

图9. 抽取滤波器对ADC输出频谱的影响—实际示例

NCO偏移后的频谱:

1.基频从+150.1 MHz下移至–4.94 MHz。

2.基频镜像从–150.1 MHz开始偏移,并绕回至186.48 MHz。

3.二次谐波从191.32 MHz下移至36.38 MHz。

4.三次谐波从+41.22 MHz下移至–113.72 MHz。

2倍抽取后的频谱:

1.基频停留在–4.94 MHz。

2.基频镜像向下转换至–59.28 MHz,并由HB1抽取滤波器衰减。

3.二次谐波停留在36.38 MHz。

4.三次谐波由HB1抽取滤波器大幅衰减。

4倍抽取后的频谱:

1.基频停留在–4.94 MHz。

2.基频镜像停留在–59.28 MHz。

3.二次谐波停留在-36.38 MHz。

4.过滤三次谐波,并由HB2抽取滤波器几乎完全消除。图9.

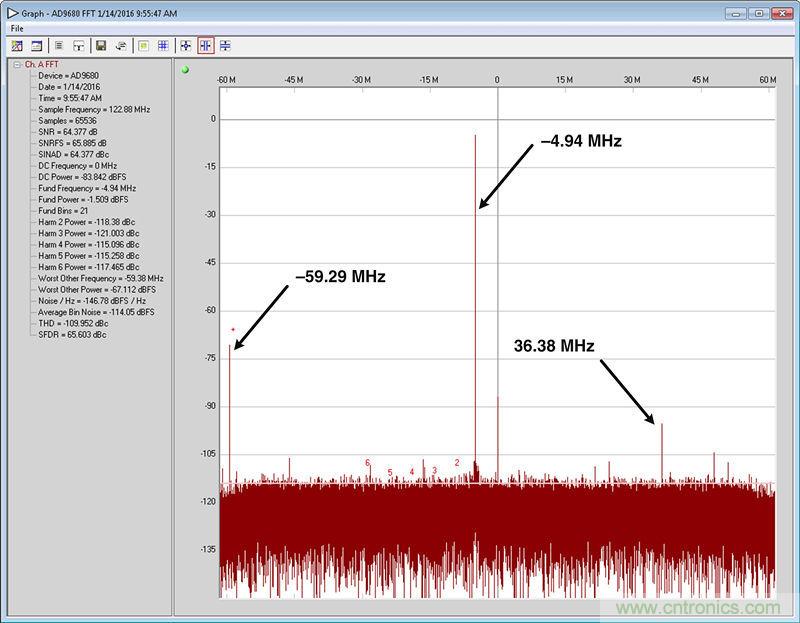

现在,来看看AD9680-500的实际测量。可以看到基频位于–4.94 MHz 。基频镜像位于–59.28 MHz ,幅度为–67.112 dBFS,意味着镜像衰减了大约66 dB。二次谐波位于36.38 MHz。注意,VisualAnalog无法正确找到谐波频率,因为它不解析NCO频率和抽取率。

图10. 信号经过DDC后的FFT复数输出曲线(NCO = 155 MHz,4倍抽取)

如果DDC设为实数输入和复数输出,并且NCO频率为155 MHz(实际是154.94 MHz),那么从FFT中可以看出AD9680- 500的输出频谱,而抽取率为4。我鼓励大家了解信号流程图,理解频谱是如何偏移和转换的。我还鼓励大家详细了解本文中的示例,以便理解DDC对于ADC输出频谱的影响。我建议打印图8 并随时参考,供分析AD9680 、AD9690 、 AD9691和AD9684的输出频谱时使用。支持这些产品时,我遇到了很多人们认为无法解释的ADC输出频谱相关的频率问题。然而一旦完成了分析,并通过NCO和抽取滤波器分析了信号流,之前认为无法解释的频谱杂散便可以证明它们实际上是确实应当存在的信号。我希望,通过阅读和学习本文,下次碰到集成DDC的ADC时,您可以更有准备地处理问题。敬请关注第二部分—我们将从其它方面继续讨论DDC,以及如何仿真它的行为。我们将讨论ADC混叠导致的抽取滤波器响应,将会提供更多示例,并使用Virtual Eval来观察AD9680中的DDC工作情况及其对ADC输出频谱的影响。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。