发射机是无线通信的重要设备之一,广泛应用于广播电视、移动通信、海洋运输及国防等领域。自动控制技术在无线通信发射领域正发挥着越来越重要的作用,发射设备的数字化逐渐趋于成熟。但是,大功率短波发射机比起中波、调频、电视发射机来说,具有变换工作频率频繁,倒频时间短;不能实现整机固态化,可靠性降低,故障率较高;工作频段范围宽,很难保证在全频段内任意频率稳定工作等特点;加之目前尚无接口标准对大功率短波发射台微机实时控制进行规范,给大功率短波发射台自动化带来困难。短波发射机的自动调谐技术正是在这种环境下产生的。

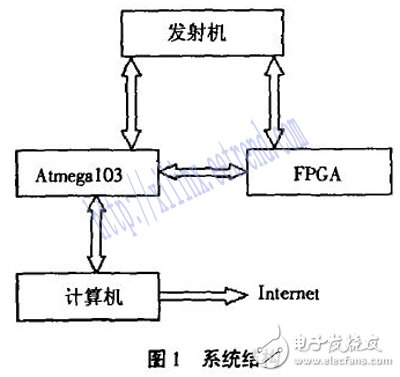

本设计的自动调谐系统是基于FPGA和AVR单片机的,其调谐对象是功率为150kW,发射频率范围为3.9 26.1MHz的短波发射机。系统结构如图1所示:

FPGA是现场可编程门阵列(Field Program一able Gate Array)的简称,是新一代的自动调谐控制单元,它采用VHDL语言进行现场编程,其特点是:I/O资源丰富,运算速度快(ns级),集成度高,稳定性好,包含的LUT和触发器数量丰富等等。

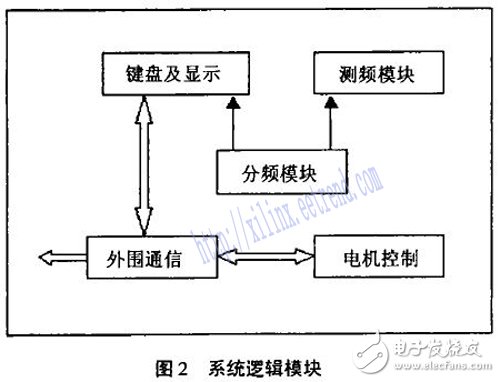

鉴于这些特点,系统拟采用单片机与现场可编程门阵列(FPGA)组合的方式。FPGA主要完成人机界面、测定发射机工作频率及调整元件位置的逻辑设计,单片机则完成上位机通信、元件位置数据采集、存储系统参数等任务。本系统设计中主要完成系统逻辑部分设计。图2所示为系统逻辑结构。

系统中的各逻辑模块设计主要用VHDL硬件描述语言完成。

发射机自动调谐是指在调谐过程中根据当前发射机的工作频率,将各个调谐元件调到与该频率相对应位置的操作过程。短波发射机各用电单元的通断,是通过配电箱中相应接触器的通断来实现。控制接触器通断的信号是由调谐逻辑小盒产生。自动调谐控制套箱是用来实现本发射机的高频回路元件在换频时的机械定位进行调谐控制。为了达到调谐的目的,自动调谐系统需要完成以下几项工作:

(1)为了实现工作人员对发射台的远程监控,需要将自动调谐系统与在线计算机相连;

(2)系统需要设置各种参数,需要有简易的人机界面,主要是键盘和LED显示;

(3)系统参数的存储及调用;

(4)发射机实际工作频率的测定;

(5)调谐元件位置信息的采集;

(6)控制执行电机调节元件位置。

操作人员先通过控制面板创建各个工作频道,每个工作频道中保存有发射机的工作频率及频率所对应的可调元件位置值。创建完工作频道后,就可以进入正常的调谐工作。选择一个工作频道,并按功能键,系统将向单片机发出中断请求,FPGA从单片机的EEPROM中取出该频道所对应的频率值及8个调谐元件位置信息,经单片机采集的8路调谐元件

实际位置信息也传送给FPGA,用于与预置值相比较,差值用于控制电机。调谐系统还有一个自动测频模块,该模块用于测定发射机实际工作频率,当该数值与预定值相等时,系统自动预置元件位置值。

系统的主要有效参数有:工作频道、工作频率、被调元件的位置值。

全机共有8个被调元件:

1路— — 高前级回路电容器,作为本级调谐(粗调、细调)用;

2路—— 高末级腔体短路板,仅作粗调:

3路—— 高末级态调谐电容,作为粗调、细调用;

4路—— 高末级调谐电容,作为粗调用;

5路—— 高末级调载电容,作为粗调、细调用:

6路—— 高末级调载线圈,作为粗调用;

7路—— 作为备用;

8路—— 高前级调谐电感,作为粗调用。

本系统具有“手动”、“半自动”、“自动’,3种调谐方式。

系统正常工作过程中主要使用“自动”调谐方式;能采用“预置”的前提是被调元件到位,系统的机械回差和电气都在允许的范围内;“半自动”方式是辅助方式,它能克服自动方式中总有个别频率不能调到状态的缺点。

(1)手动方式

“手动”方式是在操作面板上进行人工调谐的工作方式,用于初调谐和创建频道、工作频率及相应被调元件的位置值。全部被调元件的细调和初始粗调都用手动控制完成的;“手动”给定位值的获得,可通过面板上的使能键和0-9数字键盘手动进行频道初始化、工作频率设置、8个可调元件的位置设置,每设置完一个频道,可保存设置值。

设置一个频道参数。一个频道中的频道值、工作频率、元件位置值具有一一对应关系,其中一个工作频率对应的8路元件值是给定值,如果存在偏差,可以进行手动微调后再次保存。微调是人工目测,直至“鉴相器”的输出值为零时,微调就告完成。通过微调以达到获的数据的目的。

(2)自动方式

“自动”和“半自动”都是在“预置”的方式下完成的。预置是指根据需要将存储于存储器中的有效参数(包括频道、工作频率、被调元件的实际位置)传送至系统逻辑控制单元,用来重现曾经调整正常的工作频率。调谐装置是根据激励器的实际工作频率进行自动调谐工作的,自动调整过程分为下面几个步骤。

①选定工作的频道或工作频率,为频率预置;制器ATmega103。这个过程可称 4.2 开发软件

②根据工作频率预置8路元件位置值,频率和电平;

③将8路的预置位置分别与各自的实际位置进行比较,计算出存在的比较误差:

④根据各自比较结果误差的大小和极性来控制相应的执行电机的正/反转,直至比较结果误差等于零为止,电机不转。

至此,系统调谐的粗调完成,这时整机无高频输出。,接通高频,合上相应高压,令鉴相器工作,系统自动地将发射机准确地调谐在振点上,称为细调。

自动方式具有跟踪工作频率的能力,也称为频率跟踪调谐。发射机共有8个可调元件,其中只有3个需要细调,分别为1路、3路和5路。

自动调谐是按以下顺序自动完成调谐的全过程:粗调—前级细调一末级调谐—末级调载—激励电平设置。

(3)半自动方式

“半自动”方式是根据常用的工作频道自动进行预置,用“手动微调”手段进行人工调谐的工作方式。主要是用于人工干预减缓调谐进程和调试过程。半自动调谐方式对各路可调元件而言。频率预置是自动进行,而自动调谐的5个步骤(粗调、前级细调、末级细调、末级调载、电平调整)是手动干预分步进行的。因此,频率预置过程与自动方式一样。

本调谐系统设计目的之一就是对偏远地区的广播发射设备进行技术改造,因此调谐系统的开发成本是必须考虑的问题之一。另外,本调谐系统逻辑设计大概需9万逻辑门。而且FPGA芯片资源利用不宜过满。据此,FPGA选用XILINX公司Spartan—II系列FPGA :XC2S100—5 PQ208。

xc2s100—5 PQ208提供的系统门数为1O万门,具有208个引脚,速度等级为5。xC2S100的内核采用2.5v供电,工作频率可达200MHz。xC2S100具有丰富的I/O资源,I/O端口供电电压为3.3V,可承受5V的输入高电平,I/O口输出缓冲器可以接收高达24 mA的拉电流和48 rnA的灌电流。

单片机采用ATMEL公司8位低功耗AVR微控制器ATmega103。

使用Xilinx FoudaTIon F3.1i软件开发XC2S100—5 PQ2O8芯片。设计流程为:首先用编写VHDL语言程序、绘制原理图或设计状态机的方法生成表,功能仿真正确后,经过逻辑综合和布线、时序仿真,仿真通过后将编程。

模块化设计是用可编程逻辑器件设计数字系统的特点之一,这样可以简化系统设计,同时有利于协同设计。只需通过元件例化或原理图连接将多个模块联系在一起,组成一个完整的逻辑系统。本调谐系统逻辑设计由多个模块组成,下面重点介绍通信模快、键盘扫描及显示、测频模快、电机控制模块。

4.3.1 FPGA与单片机通信

自动调谐系统是由单片机子系统及FPGA组成的,这就存在两者之间的通信问题。单片机系统主要完成了可调元件的实际位置的数据采集、系统参数的存储等,这些数据需要经过FPGA的处理。

通信模块要完成的数据传输有:频道数、工作频率及对应的元件位置值,元件位置信息包括实际值和预置值,实际值有单片机系统采集得来,传送至FPGA与预置值比较,产生控制信号。

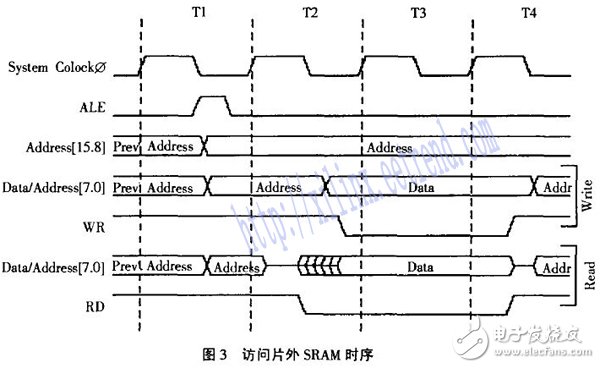

通信模块根据单片机的读写时序完成两者之间的互相通信。ATmegal03访问片外SRAM的时序见图3。

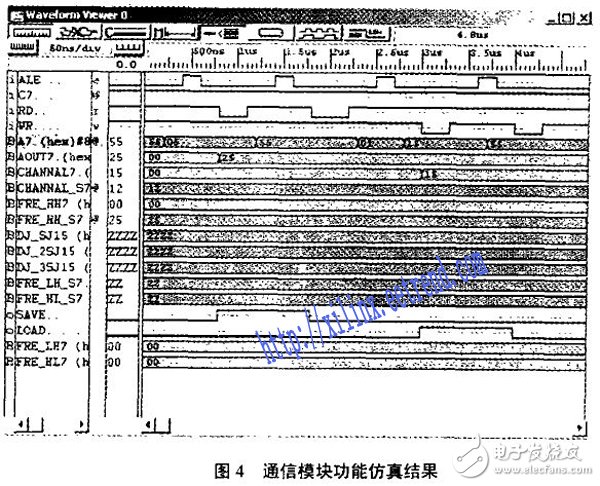

仿真中的时序是按照单片机的时序,从仿真结果中看出FPGA与单片机能按预定时序交换数据。图4所示为通信模块中部分信号的功能仿真结果。

4.3.2 键盘扫描及显示

(1)键盘扫描

在键盘中按键数量较多时,为了减少I/O口的占用,通常将按键排列成矩阵形式,矩阵式键盘扫描及显示都采用单片机来完成,这是因为单片机可以极方便的对矩阵式键盘进行扫描控制。如果使用键盘显示专用芯片,那将使控制变得更加简单。但是,即使采用矩阵式键盘,扫描时仍然要占用大量的1/O资源,这对于I/O资源很有限的单片机来说,将会使编程变得很困难。对于本调谐系统来说,单片机需要完成于上位机的通信、元件数据采集、数据存储等多项工作,I/O资源已经很紧张。因此,本系统用FPGA进行键盘扫描及显示。一方面可以充分利用FPGAI/O资源丰富的优势,另一方面FPGA的稳定性也能保证输入显示工作的准确无误。

(2)数码管显示

本模块中的显示采用动态扫描显示。显示位码与寄存器acc中的数具有一一对应关系,对应关系由状态扫描信号k来连接。信号k有5个状态,对应5位显示位码。显示部分的是7段译码,本系统只需显示数据,因此只对1O个数字进行译码。

4.3.3 测频模块

为了保证测试的,一般对低频信号采用测周期法,对高频信号采用测频法。本调谐系统所需测量的频率范围是:3.9MHz一26.1MHz,适合用测频法,而且误差不大。

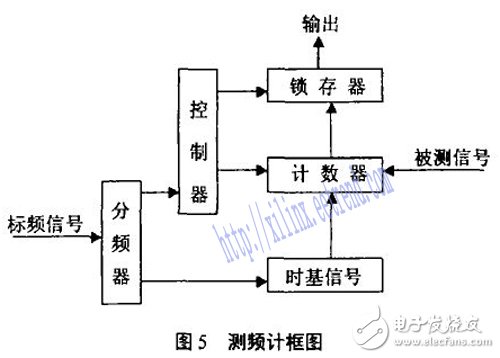

根据系统的要求,测频计需要对单位时间内的信号脉冲进行计数,从而测量出信号的频率。首先要产生一个计数允许信号,即时基信号,时基信号的宽度为单位时间,例如1s或lOOms。在时基信号有效的时间内对被测信号计数,即为信号频率。测量过程结束,需要锁存计数值或留出一段时间显示测量值,下测量前,应该对计数器清零。如图5所示:

测频计由控制器、分频器、计数器、锁存器4部分组成。控制器发出相应的控制信号,完成计数值的锁存和计数器的清零。分频器将标频信号分成一系列较低频率信号,其中一个作为测量的时基信号,该系统的分频器由专门的分频模块完成。计数器的作用是对一个时基信号中的被测信号脉冲数进行计数,计数结果即为被测频率对所选用时基的相对值。锁存器用来锁存计数结果,以便其它模块调用。

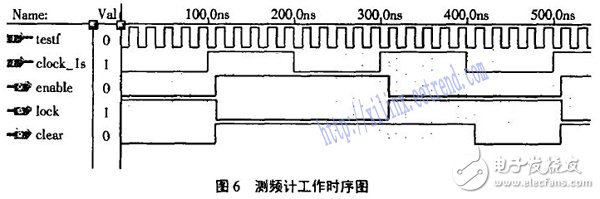

为了便于处理,系统采用频率为1Hz的信号作为时基信号。图6为测频计工作时的时序。其中testf为被测信号,clock_ls为时基信号,enable为计数使能信号,为高时有效,lock为锁存信号,脉冲上升沿工作,clear为清零信号,为低时清零。

计数使能信号enable是时基信号的二分频信号,在enable为高的半个周期里,刚好可以计完一个时基信号周期。lock信号是enable信号的取反,在上升沿将恰好计完的计数值锁存。Clear信号是在clock_ ls信号和enable信号同时为低时置低,其它情况都为高。

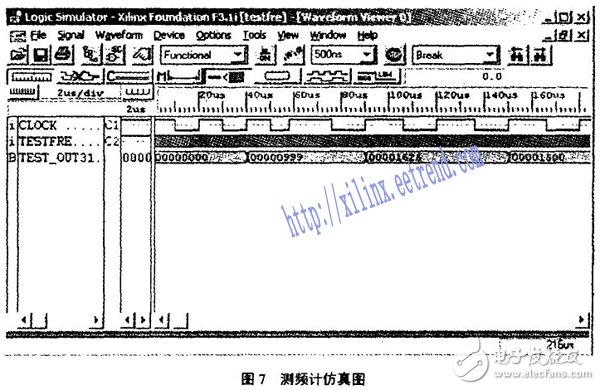

通过功能仿真发现,当被测信号换频时,会出现一个小于被测频率的计数值,2个周期后计数值正常显示,这与实际情况完全相同。这是因为在换频时,计数使能信号已经有效,这就会少计数一段时间,导致计数值小于实际值。当正常计数后,计数值会因为小数问题有微小的波动,但很快趋于正常。见图7

4.3.4 电机控制

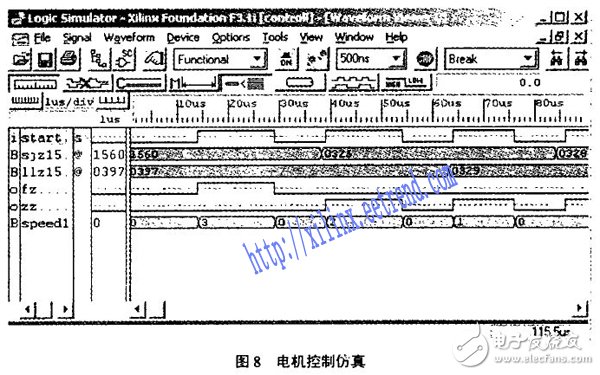

通过单片机采集的调谐元件实际位置,与EEPROM中保存的此调谐元件的工作位置(理论值)相比较。如果不等,按其差值的大小和极性来控制步进电机的转速和方向,直至二者的差值为零,即可达到调谐的目的。此模块就是理论值和实际值相比较,输出值用于控制电机的正、反转及转速的快慢。当位置预置值大于实际位置值,控制电机正/反转单元将发出指令控制电机正转;当位置预置值小于实际位置值,控制电机正/反转单元控制电机反转;当位置预置值等于实际位置值,执行电机不转;该模块还可控制电机的转速,理论值和实际值8位不等时,这表明两者差值较大,控制电机以快速度转动;当8位相等而次高4位(D4一D7)不等时,控制电机以次快速度转动;当高l2位相等而D2一D3不等时,控制电机以较慢速度转动;当2位(DO—D1)不等时,控制电机以慢速度转动。这样设计可以使每次换频时的调谐时间基本一致,而且保证了自动调谐的。

该模块也是用VHDL语言描述实现,语言描述可以很方便的调用开发软件内部IP资源。特别是在该模块中有多层次比较及减法运算,用原理图输入将会很复杂,而且容易出错。而VHDL语言支持大于、小于、不等等比较逻辑运算,应用这些比较逻辑运算将很容易实现该模块。

从仿真图中可看出电机控制模块符合设计要求,基本达到了控制目的。见图8。

FPGA的集成度高、逻辑实现能力强、设计灵活性更好。利用VHDL语言进行设计可以先装配后编程,成为产品后还可反复编程,为系统升级提供便利。系统的设计早期就能查验设计系统的功能可行性,随时可对设计进行仿真模拟。以达到降低开发成本的目的。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。