在通信及数字系统中,单片机以及DSP等电路如果出现设计缺陷,或者受到意外干扰,将会导致系统不能正常运行,死机现象时有发生,给整体电路造成较大的危害,当出现这种情况时,及时对系统进行复位就显得十分必要。本文应用FPGA设计实现一种快速响应的看门狗电路,可以对单片机、DSP、微处理器等电路提供快速响应监控。在该电路中,整体设计使用了FPGA器件,使得电路的整体性能和速度得到了极大的提高。

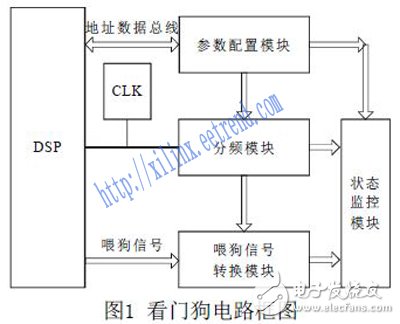

图1为所设计的看门狗电路框图。分频模块是看门狗电路的时钟产生模块;参数配置模块接收外部数据地址总线发出的参数配置信息,将信息进行提取,传送给时钟分频模块和状态监控模块;喂狗信号转换模块是根据被监控对象的喂狗方式,将不同方式的喂狗信号转换为标准统一的脉冲信号,对于喂狗的方式,可以是采用单I/O口交替写‘0’和‘1’进行,也可以使用地址数据总线写入预先约定好的数据指令进行;状态监控模块是对输入的标准统一喂狗信号进行监控。

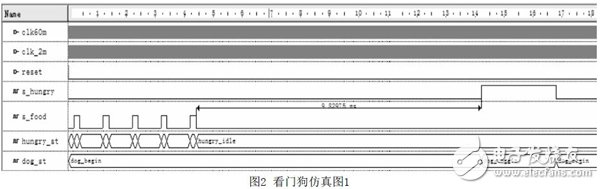

本设计采用Xilinx Spartan系列的FPGA实现,仿真结果如图2所示。如图所示clk60m和clk_2m信号是时钟输入信号,clk60m来自外部DSP的工作时钟,clk_2m是看门狗的工作时钟;reset是电路上电复位信号;s_food是由喂狗信号经过喂狗信号转换模块输出的喂狗信号;hungry_st和dog_st是状态监控模块的状态机信号;s_hungry是状态监控模块输出的监控报警信号。从图中可以看出,当喂狗信号脉冲消失大约10ms的时候,产生s_hungry监控信号,根据实际的使用需求,监控信号的响应速度可以自由调整。相对于传统的看门狗电路秒级的复位响应速度[2],该电路的响应速度提高到了毫秒的数量级。

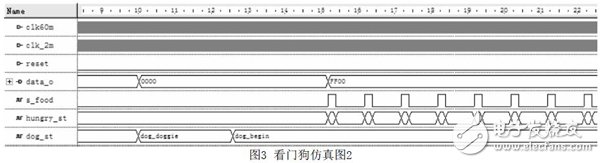

有图3可以看出,喂狗的原始信号是data_o,经过喂狗信号转换模块转换为标准的脉冲喂狗信号s_food,有标准的s_food输出状态监控模块进行状态监控。

本文采用FPGA设计实现了一种简单可行的看门狗电路,可以对实时处理的数字系统进行快速响应监控,该电路弥补了传统看门狗电路不足,具有良好的通用性、扩展性、灵活配置等特点,适用于各种实时处理的数字系统。

参考文献

[1] 李亚捷.一种FPGA+多DSP系统复位信号的设计方法.微计算机信息.嵌入式与SOC.2010,05.

[2] 李丙玉,王晓东.一种FPGA实现看门狗电路功能的方法.技术应用.

[3] 王叶辉,林贻侠,严伟.监视跟踪定时器电路的CPLD实现.电子工程师.测控技术与设备,2003,29(12).

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。