简介

精密模数转换器的每秒采样数具有明确定义且经过测试,精密数模转换器则不然,其数据手册中并未对此加以定义,因为的每秒采样数取决于许多因素。

多数情况下,数字接口支持高达50 MHz的时钟速率,假设输入移位寄存器为24位,则每秒可以执行2,000,000次写操作。然而,此数值仅表示数字接口接受新DAC码的能力,没有考虑数字处理延迟、时延以及模拟模块定时。

如果DAC无任何内部校准程序,则延迟可以忽略,通常在数ns左右。如果DAC包含校准例行程序,则延迟可能在1 μs到3 μs左右。

就模拟模块而言,有两种不同情况与新码更新相关:

更新速度受与DAC相连的有源级的带宽限制,有源级通常是缓冲器,可以位于内部或外部。

更新速度不受有源级限制,但受DAC内核限制。

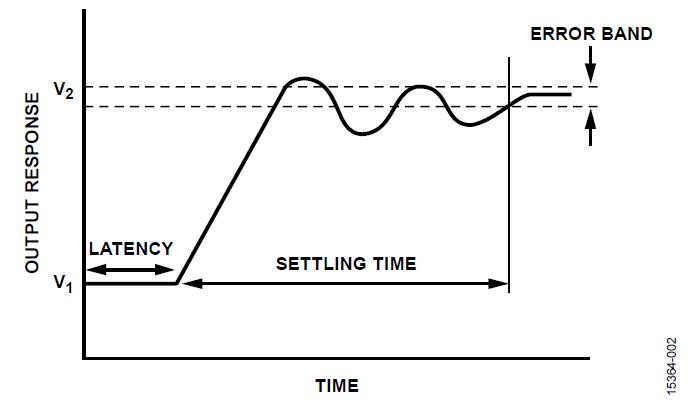

对于种情况,建立时间规格可以很好地用以估计模拟模块的能力。建立时间定义新码与前码的关系,通常是?到?比例,在规定容差之内约为终码的1 LSB左右。

对于大步进的码跃迁,压摆率是建立时间的主要影响因素。此外,建立时间还可能因为输出负载的虚部而增加,这与电容或电感类似,产生过冲或响铃振荡。

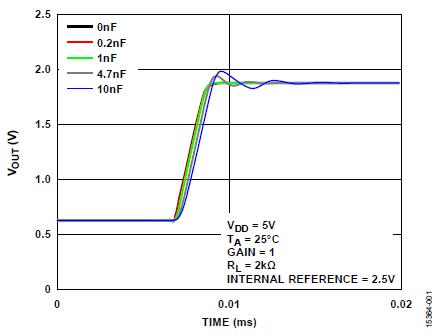

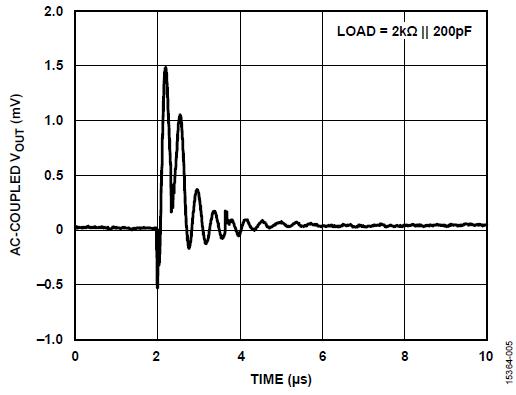

外部连接的虚阻抗值决定过冲幅度,从而影响建立时间,如图1所示。

图1.不同容性负载下VOUT与时间的关系

终建立时间是延迟、压摆率和响铃振荡时间共同影响的结果,如图2所示。

图2.终建立时间

所需的码步进越小,连接的电容越低,则终建立时间越快。

当新码接近前码时,建立时间或缓冲器能力不是限制性的;可以把这视为微调更新。

这种情况下,DAC内核的时延和动态效应是限制输出建立到规定容差范围内(即终码的1 LSB左右)所需时间的主要因素。

DAC在工作时会产生动态效应,数字模块(从外部引脚移入数据或处理命令)和模拟模块(输出更新为新码)内部产生的一些能量会传输到外部。具体来说,主要有如下两种能量:数字馈通和数模转换毛刺能量。

在输出粗调情况下,其中一些能量被缓冲器的压摆率隐藏,因为这是将能量注入输出负载的主要贡献因素,而在微调更新情况下,这两种能量均可呈现且可以测量出来。

DAC内核动态效应

任何DAC操作都会产生内部电流或电压尖峰,这些尖峰必然通过电源引脚(通常是VDD或GND)耗散。由于内部寄生效应,DAC操作时内部产生的能量无法通过这些路径完全耗散,部分能量会传输到输出负载,影响输出稳定性。

数字馈通是这样一种现象:在数据转换期间,外部数字引脚上的变化会干扰内部DAC。

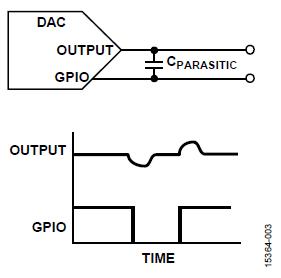

另外,外部印刷电路板(PCB)的不当布局也可能会放大数字馈通。

PCB布局的做法是让PCB中的数字走线远离PCB模拟走线,或至少避免模拟走线与数字走线并行,以使外部耦合效应。图3显示了布局不当引起数字馈通的一个例子。

图3.PCB上的容性效应

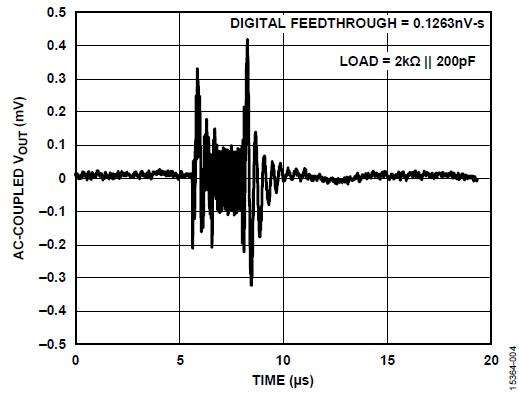

数字馈通是一个典型规格,因为传输到负载的能量取决于多个因素,例如数字输入电平、压摆率、信号发生变化的的数字走线数目(传输的数据)。

该规格测量的是面积(nV-s)表征的是外部传输的能量。图4显示了一个与写入输入寄存器相关的数字馈通效应示例。

图4.数字馈通测量示例——AD5686R

要测量与数字馈通相关的能量,须向DAC写入一个命令但并不更新DAC内核输出(例如更新控制寄存器),以免测量其他可能提高内部产生能量(即DAC内核更新时产生的能量)的效应,或测量与任何内部校准例行程序相关的额外能量。

执行内部校准例行程序所产生的能量包括在数模转换毛刺中。数字馈通表现在每次读/写访问中。

当DAC内核输出更新时,可以在DAC输出上观测到另一种动态现象以毛刺形式表现出来。此规格与DAC内核中内部开关控制线路之间的不同传播延迟有关,称为数模转换毛刺脉冲或毛刺能量,因为它是在数字字被转换为模拟信号(通过切换开关来选择DAC电阻)时产生的。

数模转换毛刺脉冲是器件固有的,但如果PCB布局不当,它会像数字馈通一样恶化。

数模转换毛刺脉冲的典型性能也用主进位跃迁1 LSB的净面积(nV-s)来衡量。对于一个16位DAC,主进位发生在DAC码0x7FFF和0x8000相互切换之间,这通常会造成内部绝大多数DAC开关发生切换。

图5显示了一个与写入DAC寄存器相关的数模转换毛刺脉冲效应示例。若要无视数字馈通贡献,可以让DAC利用延迟硬件LDAC事件进行更新,即在数字馈通产生的能量完全耗散之后进行更新。

图5.数模转换毛刺脉冲测量示例——AD5686R

不同DAC码会产生不同的毛刺能量,因为码变化涉及到不同的开关。

数模转换毛刺的差情形并不一定是主码跃迁(中间位电平码的1 LSB变化)。这取决于两个因素:布局中的内部寄生效应和DAC(包括内部校准引擎)中的内部寄生效应。实际上,数字中间位电平码并不一定是中间位电平DAC码。然而,数字主码跃迁被认为是量化数模转换毛刺能量的一个很好的基准。

DAC内核动态效应的传播

输出端的压摆率和响铃振荡是低频时的事件,而数字馈通和数模转换毛刺脉冲主要是中频到高频效应。

产生数字馈通的频率与数字传输有关,例如50 MHz时钟速度或更高速度。例如,压摆率为1 nV/s时,信号音可以高达300 MHz。图4和图5显示了动态事件频率所引起的可观测快速瞬变。

在所有情况下,内部产生的部分能量都可以在外部测量,如上面的图形所示。传输到负载的动态能量取决于与输出引脚相连的外部电容,它会产生如下的电压增量:

从基准测量结果可以看出,电压增量与外部连接的电容是相对独立的,因为传输到外部的动态能量通过DAC输出引脚这一低阻抗路径进行耗散。

连续DAC操作

如果DAC在要求快速微调的应用中连续更新,则传输到负载的能量不会完全耗散,故而在输出端会测量到额外的偏移。

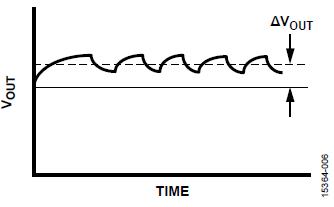

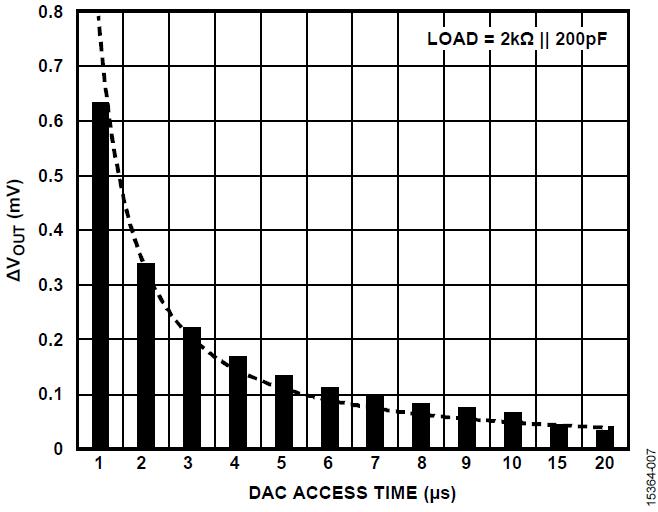

电压增量的值取决于两个因素:传输的能量值和电容的放电时间,如图6所示。

图6.VOUT增量与更新速率的关系

假设DAC连续更新,则内部产生的能量是数字馈通和模拟毛刺共同作用的结果。

某些情况下,当DAC仅访问读/写寄存器且不执行DAC内核更新操作时,电压增量仅由数字馈通引起。

AD5686R 4通道16位nanoDAC+研究

为了解说这些概念,下面以AD5686R为例进行说明。

连续更新AD5686R输出会延迟写操作的间隔时间,从1 μs到20 μs不等。

内部产生的能量在大约1 μs内传输出去,该时间是数字馈通持续时间、24位传输时间(36 MHz SCLK时钟)和模拟毛刺持续时间的总和。

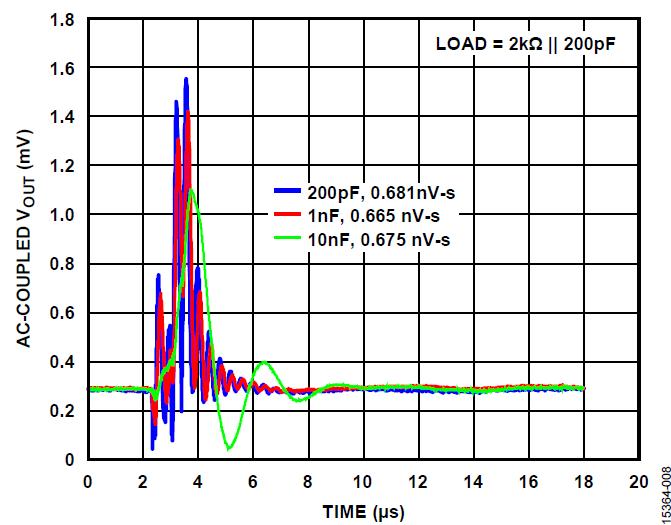

当更新时间与能量事件相似,或比能量事件更长时,根据电容值(如图7所示),产生的电压增量可近似计算如下:

干扰面积(V–s)

更新间隔时间(s)

图7.不同负载电容下AD5686R的动态能量示例

1 μs更新时,测得的电压增量与数字馈通能量和模拟毛刺一致,0.13 nV-s + 0.5 nV-s = 0.63 nV-s,如图8所示。

图8.产生的ΔVOUT与DAC访问时间的关系

举个例子,若干扰为0.63 nV-s,更新频率为2 μs,则产生的电压增量为:

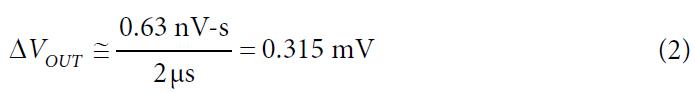

图9显示了基准测量结果与等式1之间的一致性。

图9.实测ΔVOUT结果与利用等式1得到的估计值的比较——AD5686R

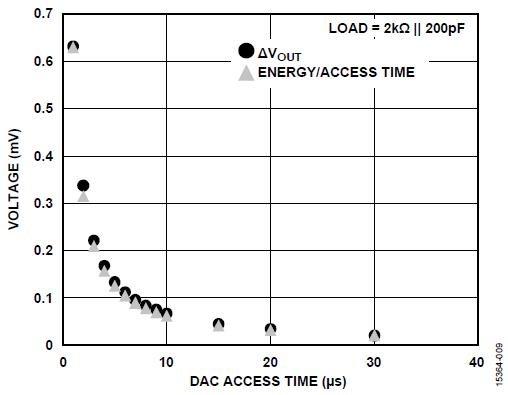

并非所有码都产生相同的净面积,ΔVOUT会略有差异。图10显示了中间电平附近代码的结果示例。产生较高动态能量的代码也会表现出较高的ΔVOUT。平均能量与AD5686R数据手册规格相当(约0.6 nV-s)。

图10.动态能量和ΔVOUT与DAC码的关系示例——AD5686R

要以高分辨率测量动态能量,输出信号必须交流耦合。这样,当试图以快速访问时间测量动态能量时,部分直流分量可能会丢失。因此,当DAC访问时间过快导致此多余能量无足够时间耗散时,ΔVOUT(直流值)是量化此能量的更好方法。

如前所述,测得的净面积与外部连接的电容无关,如图7所示。

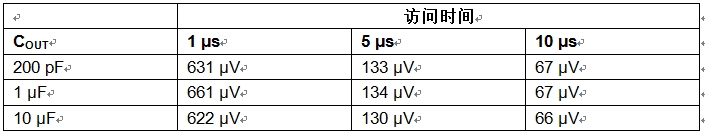

表1显示,给定访问时间时,在不同负载电容下测得的ΔVOUT略有差异。

表1.不同DAC访问时间和负载电容对应的ΔVOUT值示例——AD5686R1

1输出负载 = 2 kΩ,SCLK = 36 MHz。每个器件测量一个通道。

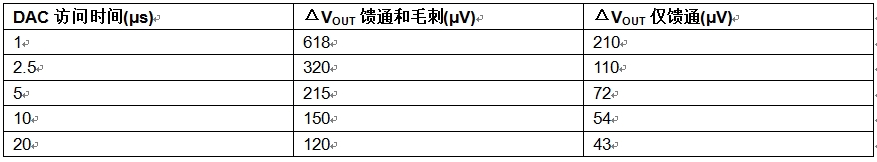

表2显示了AD5686R在不同DAC访问时间下测得的ΔVOUT:既有不同访问时间下数字馈通和数模转换毛刺脉冲两个因素引起的典型ΔVOUT结果(这种情况下更新DAC输出),也有仅数字馈通引起的结果(这种情况下DAC码写入输入寄存器,但输出不更新)。

表2.AD5686R1典型值

1输出负载 = 2 kΩ || 200 pF,SCLK = 36 MHz。

结语

由于动态现象的本质及其效应与寄生参量和耦合电路紧密相关,它们在不同DAC上会有不同的表现。动态效应的变化取决于具体应用、电路配置和工作条件。

对于DAC输出的粗调更新,建立时间和时延是DAC更新速率的限制因素。当仅涉及DAC输出的微调时,或写入器件而不更新输出时,DAC内核动态效应产生的额外能量可能会引起一些额外偏移。

如果直流性能在应用中非常重要,请勿以快速度(由数字接口决定)操作DAC。当应用明确要求较快更新速率时,必须评估能量面积以了解其对系统性能的潜在影响。要恰当地量化此影响,做法是实际测量。当系统中存在多余直流电压(ΔVOUT)时,建议在不同访问时间下测量该值,以便消除复杂且相对不可靠的交流测量需求。

一般而言,当使用DAC时,应仔细评估动态性能(建立时间、数字馈通和数模转换毛刺)及系统配置,以确立一个可靠的访问时间(更新速率)。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。