摘要:为解决现场测试系统中微弱信号的高速实时采集处理和及时可靠存储的问题,本文提出了基于PCI总线的数据采集电路的设计方案,该方案将模拟信号通过高速A/D芯片有效采样,在FPGA的控制下将数据上传到PC机进行分析处理和保存, 从而实现微弱数据信号的高速采集和将采集到数据流的稳定传输和处理、显示。

1.引言

随着微电子技术的广泛普及、计算机技术的快速发展,现场信息实时采集系统的性能越来越受到大量关注。从测试系统和科研领域产生的动态信息中提取有用数据进行现场实时采集并存储显得尤为重要。设计结合实际项目要求,提出基于PCI总线的微弱数据信号采集电路设计方案,将采集数据流通过前端处理电路和AD转换电路后,在中央控制模块FPGA控制下将数据流通过PCI总线传输给上位机保存,以便分析处理和显示,从而实现采集系统对微弱数据信号进行高速采集存储和分析。

2.总体设计方案

在实际研究和现场测试中,数采系统常采用PC机为测试平台,使用PCI总线作为中介实现数据流采集和传输到PC机中进行显示分析。

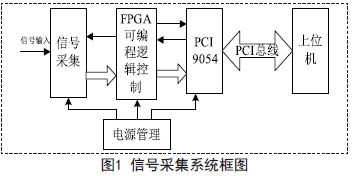

系统常采用传感器将物理量转换为电流或电压信号,经过前端调理电路滤波放大将幅度放大到可测试范围。但在实际信号采集时存在由系统本身和外界产生的各种噪声影响,使得传感器输出的微弱有用信号被淹没,因此需要采取有效的措施和算法来抑制噪声、增大微弱信号幅度,从而提取有用信号,提高系统输出信号的信噪比,实现微弱信号的高采集。基于PCI总线的微弱信号采集系统电路设计可分为:信号采集,FPGA逻辑控制,PCI总线界面以及电源管理等模块。信号采集即实现模拟信号的接收和将其数字化;FPGA逻辑控制则实现对采集数据流缓冲处理、控制采样时钟频率以及采集模块与PCI9054界面芯片的握手通信完成数据传输。系统设计总体方案如图1所示。

采集系统上电启动后,PC机扫描查找采集卡,然后通过上位机对系统进行初始化,并配置采样参数。系统采集部分在FPGA控制下将接收数据进行调理、AD转换后存储到FPGA内部FIFO中缓存,继而通过PCI总线将数据传入PC机进行实验数据的分析显示和存储。

3.硬件电路设计

采集系统主要包括AD转换电路、PCI总线界面电路以及外围电路。设计采用可编程FPGA和高速AD实现信号采集处理功能,PCI总线界面电路采用控制器PCI9054实现数据传输,并通过FPGA控制电路时序。

3.1 数据采集电路设计

系统数据转换模块采用1.8V单电源供电的14位高速AD模数转换器AD9246,采样率为125MSPS,采用多级差分流水线结构。

采样频率为70MHz输入时,无杂散动态范围为8 5 d B c,信噪比为7 1 . 7 d B c,低功耗设计(395mW@125MSPS)。AD9246为差分输入器件,输入信号通过衰减等处理抑制外界干扰,实现在干扰信号比较强时有效的捕捉有用频带宽度范围内的微弱信号。为有效抑制周围环境噪声对输入信号的影响,设计将AD转换芯片的信号和时钟输入设为差分输入,即采用差分转换芯片AD8138将模拟信号转换为差分信号送入AD转换器,使其在时钟控制下输出14位并行数据传送给后续电路。差分时钟则通过FPGA分频转换产生以实现AD9246内模数转换周期的控制。

3.2 PCI总线界面模块设计

PCI界面模块选用控制器芯片PCI9054来实现PCI总线和本地总线之间信息的传递。

PCI9054是PLX公司生产的32位,33MHz的PCI总线通用桥接芯片,具有132MB/S的突发传输速率,可以将PCI总线复杂的逻辑控制转换为简易的本地总线的逻辑控制。设计通过对PCI总线界面电路进行读写来实现采集数据的传输和上位机控制信号的下传。PCI9054提供有PCI总线界面、本地总线界面和E2PROM界面。

在设计PCI9054与本地总线界面电路中,将本地总线界面配置为C模式,即设置MODE[1:0]=00,将MODE0和MODE1管脚接地。在系统上电初始化时,PCI9054根据串行E2PROM界面参数配置内部寄存器,采用2Kb的E2PROM芯片93CS56L来存储PCI9054界面芯片的配置参数。

4.FPGA控制逻辑设计

FPGA控制模块主要实现对AD采集信号的控制和预处理,以及PCI的界面功能,完成数据的实时采集处理。系统中FPGA选用Xilinx公司的Virtex-4系列芯片XC4VLX25-10SF363I作为设计主控器件,并选择XCF08PVO48C作为配置芯片。

FPGA内部逻辑包括控制模块,双口RAM缓冲模块,时钟控制模块,32位加法器模块。

其中由控制模块完成对累计次数,AD读写,PCI总线读写,采样时钟转换,加法器等的控制功能。其中时钟转换即实现数采频率100MHz和PCI读数40MHz时钟的转换;累加次数控制是通过上位机软件发送给的,由PCI写时序控制的,由于AD9246为14位转换器,系统数据宽度为32位,所以可达218次的累加次数。

4.1 FPGA数采逻辑控制

在FPGA对数据采集AD转换的控制设计中,主要在FPGA中对采样时钟分频以输出AD时钟信号和控制允许信号,以及为AD提供不同的采样频率和数据接收触发信号来完成AD数采功能。

4.2 FPGA对PCI界面控制

通过使用FPGA对PCI总线界面逻辑控制实现PCI界面芯片PCI9054与本地总线之间数据通信。设计采用DMA方式作为PCI9054本地总线端的传输方式,并将操作模式配置为C模式。DMA传输方式即使用PCI9054芯片内部DMA控制器来实现PCI总线与本地总线之间数据传输。通过上位机软件设置芯片工作方式和参数,从而确定数据传输要求,直接利用芯片内DAM控制器启动传输工作对PCI总线和本地总线之间读写进行操作,节省了占有计算机CUP从而加快传输速率。

5.测试结果

通过对采集信号测试,可以看到原始包含噪声的信号如图2所示,对信号进行不同累加取平均的结果如图3和4所示。通过分析可得当提供累加次数可改善信号的信噪比。

6.小结

本文提出了一种基于PCI总线的微弱数据信号采集电路设计方案, 方案中设计了基于PCI总线的数采系统对微弱信号进行检测处理,实现数据采集系统的实时传输。设计选用高速AD转换芯片AD9246采样,选用差分方式有效抑制噪声影响。通过对采集信号源测试分析,可以对信号进行可靠实时的传输,从而证实本方案的可行性。(作者:王静宜,靳鸿)

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。