相关资料:

3 导航计算机硬件设计

导航系统的主要任务是测量各种载体的即时位置、速度、航向等导航参数,具有实时性高、运算量大等特点。因此在导航系统中,计算机设计是系统设计的关键。在基于DSP和单片机的导航系统中,导航计算机的任务首先是数据采集,包括采集惯性测量单元输出信号,接收外部系统校正信息,如GPS输出信息、初始位置信息等。其次是数据处理与运算,包括惯性测量元件的误差补偿、初始对准、导航参数解算、组合导航算法实现等。是输出导航系统级系统状态量,包括输出导航参数以及与其它设备交换信息等。所有这些任务,如果都由一个CPU来进行运算的同时,还要兼顾系统控制和数据输入输出,并响应频繁的中断,必然降低系统运行效率,所以为了提高系统运行速度和效率,减轻导航计算机的负担,设计一种以DSP和单片机为主的主从系统。导航计算机工作流程为:经过前端处理的模拟信号由ADS1258完成采样转换后,给DSP一个中断,读取各个通道的数据并存储在片外SRAM 数据区,同时DSP进行惯性测量元件的初始对准、误差补偿,在线校正滤波和导航参数解算,从而完成对系统目标的定位功能,再由双口RAM 实现DSP和单片机目标信息的交换,终通过单片机完成系统的I/O接口和外部接口设备控制,系统总体结构如图1所示。

图1 导航计算机系统总体结构图

在导航计算机中,需要对接受到的模拟数据进行采样,并转换为数字信号,送给CPU 计算和处理,处理器TMS320VC33与ADS1258通讯采用了TMS320VC33的SPI接口,TMS320VC33通过SPI接口对ADS1258进行初始化及读取数掘,把通过TMS320VC33数字滤波器处理过的数据发送给ADS1258的DIN、DOUT分别用于数据的输入和输出,SCLK用于串行时钟的输入;START是AD的启动信号,高电平有效,将DSP的XF0设置为通用I/O口,以XF0信号连接AD的START,启动AD转换器开始采样和转换;/DRDY是AD转换结束信号,低电平有效;从AD读出转换数据都是在AD转换完成后/DRDY为低电平时开始的,读出转换数据之前DSP需查询DRDY的状态。

本系统采用中断方式,将/DRDY信号直接连接在DSP的外部中断信号INT0上,提高了系统运行效率。

图2 AD转换器与DSP接口设计图

TMS320VC33 无内部ROM 存储器,需扩展外部存储器,外部存储器采用FLASH 和SRAM 的配置方式,FLASH用来存储DSP系统的程序以及初始化数据,系统启动后,TMS320VC33自动将程序和初始化数据从FLASH 加载到SRAM 中,加载完成后,程序在SRAM 中运行。本系统设计选用AM29LV800BB-90EC,容量大小为512K×16位,访问时间:90ns;存储容量:8Mbit;工作温度范围:-55~+125℃;在线编程电压:3.0~3.6V;低功耗:读操作时电流为7mA,编程/擦除时电流为15mA.AM29LV800BB-90EC的地址线A0~A18与TMS320VC33的地址线A0~A18连接,AM29LV800BB-90EC的数据线D0~D15与TMS320VC33的低16 位数据线D0~D15 连接,TMS320VC33 的/PAGE0 连接AM29LV800BB-90EC 的片选信号/CE,TMS320VC33的R/W 信号连接AM29LV800BB-90EC的写信号/WE,选择16位数据模式。

图3 DSP与FLASH存储器接口设计图

由于系统运行时,需要对SRAM 进行频繁读写操作,因此采用快速存储器件ISSI的IS61LV51216,它集成度高、功耗低、是一个8M 容量,结构为512K*16位字长的高速率SRAM.采用两片IS61LV51216 芯片与DSP 连接。

IS61LV51216的地址线A0~A18与TMS320VC33的地址线A0~A18连接,片IS61LV51216的数据线D0~D15与TMS320VC33的低16位数据线D0~D15连接,第二片IS61LV51216的数据线D0~D15与TMS320VC33的高16位数据线D16~D31连接,TMS320VC33的/PAGE1连接IS61LV51216的片选信号/CE,TMS320VC33的R/W 信号连接IS61LV51216的写信号/WE,选择16位数据模式。

图4 DSP与SRAM 存储器接口设计图。

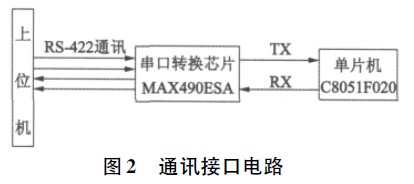

计算机需要接受GPS定位信息,并进行解码计算,还需要接受输入输出控制,处理的数据量很大,对数据通讯的稳定性和可靠性要求都比较高。传统的数据通讯主要有串行、并行、DMA以及双口RAM 等方式。综合各种通讯方式的优缺点,考虑到该导航系统实时性高。数据量大的特点,采用双口RAM 的方法实现DSP和单片机的实时数据通讯。系统选用IDT7005S,它是一款高速8K*8双端口静态RAM,与单片机组成接口电路时可直接相连。89C51的地址总线宽度为16位,数据总线为8位;而IDT7005S的地址总线宽度为13位,数据总线为8位,需对单片机进行总线扩展,具体使用锁存器74LS373的使能信号,对数据进行分时读写,实现总线扩展。

图5 单片机DSP与双口RAM 接口设计图

4 系统软件设计

整个软件基于中断方式。DSP软件工作流程为:系统上电复位后,加载外部flash的程序文件到外部SRAM 程序区,DSP初始化各个部分后运行。程序始终查询AD的中断信号,在获得AD的中断后进入中断服务程序,采集后的数据存储在外部SRAM 数据区,然后调用探测定位程序获取声音目标的方位等参数,并写入双口ram中,供单片机读取后进行融合。本系统的DSP软件流程如图5所示。

图6 DSP软件设计流程图

5 结语

本文结合了现代导航新技术的发展与需求,以DSP作为处理器实现导航系统的算法,以FPGA实现外围接口的扩展,采用了高AD转换器采集惯导数据,设计了基于DSP微小型的导航计算机。采用FPGA实现外围接口的扩展,体积上省去了串口芯片,功能上能够辅助DSP完成对GPS和数据采集的接受,这样不仅省去了CPU 的一定工作量,还可以使CPU更能够专注于组合导航的算法的计算,从而进一步提高系统的性能。本系统采用的高AD转换器ADS1258为TI公司刚刚推出的高AD,在以及转换速度上大大优于以往的AD转换器,这对于导航系统的性能奠定了硬件基础。对DSP导航计算机硬件的设计在日后的发展也起到了很好的带动作用。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。