引 言

变频器的英文译名是VFD(Variable-frequency Drive),这可能是现代科技由中文反向译为英文的为数不多实例之一。(但VFD也可解释为Vacuum fluorescent display,真空荧光管,故这种译法并不常用)。变频器是应用变频技术与微电子技术,通过改变电机工作电源的频率和幅度的方式来控制交流电动机的电力传动元件。变频器在中、韩等亚洲地区受日本厂商影响而曾被称作VVVF。

上变频器是射频发射机不可或缺的重要器件,其性能受电磁兼容等多方面的影响,因此上变频器的设计是保证输出信号质量的重要前提。

当前市场上有多款针对特定应用的上变频芯片,但是在使用上缺乏灵活性。主要的上变频电路设计也针对相应频点或频段,并且缺少针对的输出功率控制和运行时可变频点的设计。本文结合工程实际应用设计了一种以L波段为主的兼容多波段上变频器,包括混混频,锁相环(PLL)电路,自动增益控制(AGC)电路、衰减和电磁屏蔽多方面内容。

本文综合考虑各个影响因素,设计的兼容多波段上变频器可以灵活的设置本振信号频点,的控制输出功率。实际测试表明本振信号稳定,频率可以选用不同的器件实现在L波段的任意设置,能够实现-130dBm的低功率信号输出,并且可以在-130dBm到-80dBm之间以0.25dB步进实时调整。

2 上变频器原理

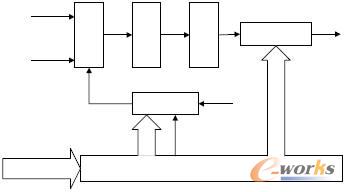

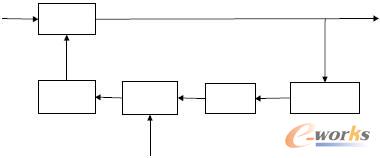

上变频器的组成原理框图如图1所示。

图1 上变频器总体框图

上变频器的输入信号为I/Q两路,与单路混频上变频相比可以更好地抑制载波和一个边带。为了使射频输出能够进行的功率控制,信号滤波后使用AGC电路去除器件噪声和输入信号不稳的影响,结合多级数控衰减器和固定衰减器输出组成的衰减网络,达到功率控制的目的。本振模块采用可编程的PLL电路,使设计可以应用于L波段多个频点上变频器的本振信号产生。

3 主要模块的分析和设计

3.1 IQ调制电路分析和设计

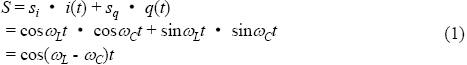

假设两路中频信号分别为i(t)、q(t),正交的载波分别为si、sq,输出信号为S,则有:

其中,i(t)=cosωCt ,q(t)=sinωCt ,si=cosωLt ,sq=sinωLt

由此可见当两路信号正交时,载波和一个边带被完全抑制,这就减少了对射频滤波器的要求。如果两路信号不正交,令i(t)=Acos(ωCt+φ)+B ,其中A表示信道增益不平衡,φ表示相位不平衡,B表示直流偏差,则:

此时,输出信号不能完全抑制载波和一个边带,且会对需要的边带产生影响。为了减少IQ正交性对输出信号性能的影响,上变频器的IQ两信道要对称,并且提供相同的直流驱动来提高IQ调制电路的载波和边带抑制能力。

3.2 PLL电路设计

锁相环路是一种反馈控制电路,简称锁相环(PLL,Phase-Locked Loop)。锁相环的特点是:利用外部输入的参考信号控制环路内部振荡信号的频率和相位。因锁相环可以实现输出信号频率对输入信号频率的自动跟踪,所以锁相环通常用于闭环跟踪电路。锁相环在工作的过程中,当输出信号的频率与输入信号的频率相等时,输出电压与输入电压保持固定的相位差值,即输出电压与输入电压的相位被锁住,这就是锁相环名称的由来。

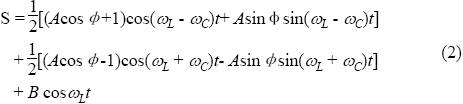

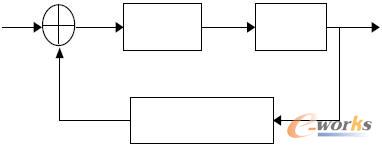

PLL电路产生本振信号。PLL是一种相位反馈控制系统,它能使压控振荡器的频率和相位均与输入信号保持确定关系,并且使输入信号中存在的噪声及压控振荡器自身的相位噪声得到一定的抑制,PLL电路原理如图2所示:

图2 锁相环电路原理框图

设计中可以使用内部集成鉴相器和分频器的可编程频率合成器,与外部环路滤波器和VCO构成完整的PLL。由于产生的本振频点的可编程性,使电路的设计对不同频点信号具有通用性,可以适应不同系统的要求。

在使用集成频率合成器和VCO的PLL电路设计中环路滤波器的设计是关键,其作用是抑制鉴相器输出电压中的载频分量和高频噪声,降低由VCO控制电压的不纯而引起的寄存器输出,对输出的本振信号频率稳定度有很大的影响。

3.3 AGC电路设计

自动发电量控制AGC(Automatic Generation Control)是能量管理系统EMS中的一项重要功能,它控制着调频机组的出力,以满足不断变化的用户电力需求,并使系统处于经济的运行状态。控制电压形成电路的基本部件是 AGC 检波器和低通平滑滤波器,有时也包含门电路和直流放大器等部件。放大电路的输出信号u0 经检波并经滤波器滤除低频调制分量和噪声后,产生用以控制增益受控放大器的电压uc 。当输入信号ui增大时,u0和uc亦随之增大。

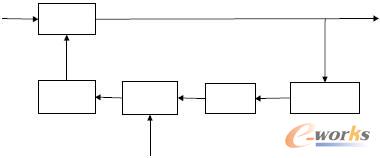

AGC电路是一种在输入信号幅度变化很大的情况下使输出信号幅度在较小范围内变化的自动控制电路。常用的反馈型AGC原理和线性模型如图3~4所示。

图3 AGC原理框图

图4 AGC控制环路模型

在上变频器中,为了抑制器件温漂、输入变化以及其他干扰从而实现对射频输出功率的控制,需要使用AGC电路稳定调制器输出信号的功率。

3.4 阻抗匹配和屏蔽

信号传输过程中负载阻抗和信源内阻抗之间的特定配合关系。一件器材的输出阻抗和所连接的负载阻抗之间所应满足的某种关系,以免接上负载后对器材本身的工作状态产生明显的影响。对电子设备互连来说,例如信号源连放大器,前级连后级,只要后的输入阻抗大于前的输出阻抗5-10倍以上,就可认为阻抗匹配良好;对于放大器连接音箱来说,电子管机应选用与其输出端标称阻抗相等或接近的音箱,而晶体管放大器则无此限制,可以接任何阻抗的音箱。

为了保证信号传输效率,PCB 板要充分考虑阻抗匹配的问题,主要包括各个模块之间以及信号线的匹配。以三端连接时50Ω阻抗匹配为例,每端串联16或18欧姆电阻,则每端看入的阻抗均为:(16/18+50)/2+16/18≈50(Ω)。

射频电路的每个部分均封装在金属盒的分腔中,减少前后级射频辐射的相互影响,尤其对于多级衰减电路,屏蔽的作用尤为重要。同时在PCB电路板布线时,要充分考虑射频辐射的影响。

3.5 软件设计

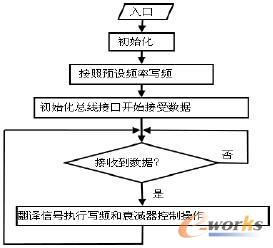

控制信号接口的微控制器的软件主要功能是接收和解析上级电路的写频控制信号和功率控制控制信号,使用I2C总线传输,协议简单且两条传输线占用空间少,软件流程如图5所示。

图5 软件流程图

4 电路实现和测试结果

4.1 电路实现

(1)IQ调制电路实现

IQ调制芯片使用ADI公司的AD8346是由ANALOG DEVICES公司生产的正交调制器,其调制信号的3dB带宽为70MHz,载波的频率范围为0.8GHz ~2.5GHz,其可调制的基带信号带宽为直流到70 MHz。单端2.7~5.5 V供电,静态工作状态下电流值为45 mA,休眠状态下电流仅为lμA。该器件具有较高,在1.9 GHz时,正交均方误差仅为l°,I/Q幅度平衡仅为0.2dB。其的相位和幅度平衡特性使其可直接将信号调制到射频。它可实现 QPSK/GMSK、QAM、AM、SSB、BPSK 等多种调制,在GSM、CDMA、PCS、DCS 等数字通信系统中有较为广泛的应用前景。

(2)PLL电路实现

PLL电路选用ADI公司的小数分频频率合成器ADF4153,频率范围500MHz~4GHz,包含低噪声数字鉴相器,精密的电荷泵以及可编程的参考分频器(三线串行接口,可以使用微控制器通过CLK、DATA和LE三条线进行写频,并且支持SPI总线方式)。

以参考频率10.23MHz,分辨率10kHz,产生1222MHz本振为例,ADF4153频率设置如下:

MOD=10.23MHz/10kHz=1023

INT=1222MHz/10.23MHz=119(取整数部分)

FRAC=(1222/10.23-119)*MOD=463

然后根据MOD INT FRAC设置芯片N和R寄存器的相应位。压控振荡器选用ZCOMM公司的V585ME15,频率范围是1100MHz~1400MHz,典型的1Hz带宽情况下10kHz偏移量处的相位噪声为~100dB/Hz。

(3)AGC电路实现

AGC电路中可控增益放大器选用ADL5330,ADL5330是一款宽带电压可变增益放大器,额定工作频率范围为10 MHz至3 GHz。该器件可以在60 dB范围内提供精密线性dB增益控制,衰减约为-40 dB,增益约为+20 dB。在60 dB范围内设置增益或衰减时,需要0至1.4 V的增益控制输入电压。ADL5330可提供高线性度输出功率,因而是无线基础设施发射信号路径的理想解决方案。它集成了宽带放大器和衰减器,所以比分立器件实现方案极大地节省印制电路板面积、减少元器件数量并且降低成本。ADL5330具有60dB动态增益和衰减范围(约+20dB增益和-40dB衰减),22dBm输出功率水平(1dB压缩点)以及在1GHz频率和8dB噪声系数(NF)下具有+31dBm输出三阶截点(OIP3)。

ADL5330可以和ADI公司的I/Q调制器(选用的是AD8346)和功率检测器(选用的是AD8361)较好的配合使用,构成完整的信号通道。

电平检测选用ADI公司的AD8361,AD8361是一款TruPwr?检波RFIC,首次以集成形式提供均方根(RMS)响应功率检波功能,它能够将一个2.5 GHz的复合调制RF信号转换为代表该信号均方根电平的直流电压。该器件具有高线性度和高温度稳定性,适用于CDMA、QAM和其它复合调制方案的检波。

动态范围为30 dB。测量在14 dB范围为0.25 dB,在23 dB范围为1 dB。该器件提供8引脚小型SO封装,采用2.7 V至5.5 V电源供电,功耗仅为4 mA。

通过调节环路的直流增益(检波器后面的运放)可以调节AGC输出,稳定后输入变化环路自动调节VGA的放大倍数从而保持输出不变,实际电路经调试可以保证在输入变化50dBm的范围内变化输出基本保持稳定。

(4)控制信号接口电路实现

控制信号接口模块的微控制器选用Atmel公司的ATmg16单片机,硬件支持I2C总线,程序设计更为方便。

4.2 测试结果

本文实现了可以进行实时功率控制和本振频率控制的上变频器,实际电路设计中各个部分采用分腔的结构,通过对各个分腔模块的调整可以实现对不同波段和功率要求应用的快速调整和重新设计。

图6~7为一个具体上变频器的实际测试结果。中频输入信号为46.52MHz,上变频至1268.52MHz , 功率控制范围为-130dBm~-50dBm, 步进量为0.25dBm,频点可以在1100MHz~1400MHz范围内以10kHz的分辨率任意设置。测试结果表明电路产生的本振信号稳定,IQ调制器输出对载波和下边带抑制达到30-40dB,上变频后的信号质量较好。

图6 本振信号

图7 上变频后载波和下边带的抑制情况

5 结束语

本文分析了发射机射频上变频器各个组成部分,提出了多波段兼容上变频器的设计方案,并且具体设计和实现了一个L波段上变频电路,给出了实际测试结果。实际测试结果表明电路性能良好,为通用射频模块设计提供一种解决方案。

本文作者创新点:射频电路设计和调试往往比较困难。本文设计了一种适用于多个频点的通用上变频器,可以对本振信号频点和输出功率进行实时控制,电路结构清晰,实际电路性能良好,提供了一种通用射频上变频器的设计方案。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。