芯片的烧写与自加载是一个DSP系统能够顺利运行的基本条件。在DSP加载技术方面已经有大量文献和工作成果,比较好地解决了DSP自加载方面的许多基本问题。而传统的烧写/加载方案在调试、更新程序时需要反复外接仿真器,配置跳线,并且只能加载运行指定地址空间上的工程。这些对处于安装调试阶段的系统影响不大,但在诸如航天设备、大型机械或其他恶劣环境中工作,难以直接进行仿真器连接的DSP系统中,无法采用普通的烧写/加载方案对其进行更新和调试。

在许多DSP应用系统中,都需要DSP芯片能够在加电后自动从外部设备加载程序,也就是引导(Boot-load)。TI公司的TMS320C6000系列芯片有三种引导方式可供选择,分别是不加载、ROM加载和主机加载,详细工作流程如下:

不加载:CPU直接从地址0处开始执行代码。如果该处内存是SDRAM,那么CPU会先挂起,等待SDRAM的初始化完成。

ROM加载:位于外部CE1空间的ROM中的代码首先通过DMA/EDMA被搬入地址0处。加载过程在复位信号撤销后开始,此时CPU内部保持复位状态,由DMA/EDMA执行一个单帧的数据块传输。对于C620x/C670x,DMA从CE1空间中拷贝64 KB数据到地址0处。传输完成后,CPU退出复位状态,开始执行地址0处的指令。对于C62x/C67x,用户还可以指定外部加载ROM的存储宽度,EMIF会自动把相邻的8 b/16 b数据合成32 b的指令。

主机加载:也就是HPI加载。CPU停留在复位状态,芯片其余部分保持正常状态。引导过程中,外部主机通过主机接口初始化CPU的存储空间。主机完成所有的初始化工作后,向接口控制寄存器的DSPINT位写1,结束引导过程。此时CPU退出复位状态,开始执行地址0处的指令。

TMS320C6701(以下简称C6701)是TI公司近年来推出的含多个处理单元的一种新型新点DSP芯片。它采用VLIW结构,在167MHz的主频下可以得到1GFLOPS的高处理速度。CPU中包括报两套对套的运算单元(L,S,M,D)和相应的两套寄存器组,每组有16个32位宽的寄存器。每个功能单元输入输出端口相互独立,可实现并行处理。C6701的地址总线为32位,寻址范围达到4GB.存储空间可分为四部分:片内程序空间、片内数据空间、外部存储空间和内部外围设备空间,可通过对五个BOOTMODE引脚的灵活设置设定各空间的地址范围。

1 ROM加载的实现

究竟使用哪种引导方式取决于芯片引导模式设置,而引导模式由BOOTMODE[4:0]管脚确定。系统加电后,RESET信号有效,DSP芯片复位,在RESET信号上升沿处锁存BOOTMODE[4:0]管脚上的设置值,以此决定DSP芯片内存映射方式、地址0处的内存类型以及复位后芯片的引导模式。本例中C6701的BOOTMODE值设为01101,即8 b ROM加载。

ROM加载是工程中常见的加载方式,这种方式可以把程序代码段和数据段保存在ROM,FLASH等非易失存储器中,加载过程完全由DSP自动完成,在实际应用中十分方便。ROM加载的具体步骤如下。

1.1 分配存储空间,生成目标文件(。out)

对于TI公司TM系列DSP的ROM加载过程是:位于CE1空间的ROM中的代码首先通过DMA/EDMA被搬入地址0开始的内部存储器。加载过程在复位信号撤消之后开始,此时CPU内部保持复位状态,由DMA/EDMA执行1个单帧的数据块传输。传输完成后,CPU退出复位状态,开始执行地址0处的指令。对于C62x/C67x,用户可以指定外部加载ROM的存储宽度,EMIF会自动将相邻的8bit/16bit数据合成为32bit的指令。对C620x/C670x,ROM中的程序必须按little-endian的存储模式存储;对C621x/C671x,ROM中的程序存储格式应当与芯片的endian模式设置一致。C64x只支持8bit的ROM加在,ROM中的程序存储格式需要与芯片的endian模式设置一致。对于不同的芯片,加载过程还略有不同。

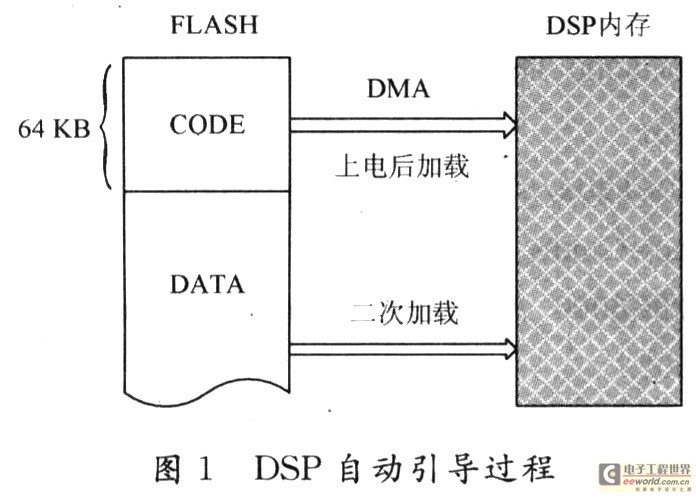

在ROM加载模式下,复位后C6701将通过DMA方式将FLASH中的前64 KB数据搬运到DSP的片内程序RAM执行,因此,必须将前面编译好的工作程序的代码段烧写到FLASH地址空间中的前64 KB,而数据段则应该烧写在FLASH首地址64 KB以后。这就需要在DSP芯片的内存段管理中,将数据段的加载地址(Load Address)配置为CE1空间FLASH上的指定地址,以保证DSP在复位后能正确地从FLASH上的不同地址读取代码和数据(见图1)。

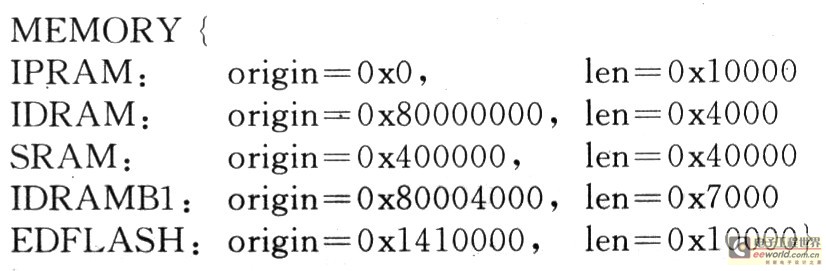

利用CCS自带的DSP/BIOS配置工具,可以在类似Windows Explorer的窗口界面下直观方便地初始化DSP芯片的数据结构并设置不同的参数,而不需要再单独编写连接命令文件。保存该配置文件时,配置工具自动生成匹配当前配置的汇编源文件和头文件以及一个链接命令文件。当构建(Build)应用程序时,这些文件都会自动被链接进应用程序。在CCS中打开DSP/BIOS中的。cdb文件,操作System下的MEM(Memory Section Manag-er)模块就可以对DSP存储器映射空间进行配置,并可以设置程序编译后生成的代码段、数据段是如何分配到这些存储器空间的。这对ROM加载能否成功至关重要,要实现ROM加载必须把一些关键的代码和数据段装在系统的ROM中,但上电后仍在较快的DSP片内RAM中运行。这需要在DSP的内存映射空间上先划分出外部FLASH的起始地址和长度(如图2中的ED-FLASH段),并将CCS编译产生的各个段的运行地址和加载地址分配到合适的存储空间。需要特别注意的是,数据及代码初始化段的加载地址必需放在FLASH空间上(如图3),只读的段都可以放在FLASH上,非初始化段只需要分配运行地址。

下面是用DSP/BIOS配置工具在DSP内存空间中划分好的各段开始地址及长度,其中EDFLASH就是外部FLASH上用于二次加载的地址空间。代码则存放在FLASH的首地址,也就是0x1400000.

1.2 转换文件格式,得到烧写文件(。h)

程序编译好后输出的是COFF格式的。out文件,这种文件无法直接写进FLASH,所以只能将其转换为其他FLASH支持的格式。一般来说,对FLASH烧写的传统方法是通过CCS自带的格式转换器hex6x把。out文件转换为FLASH可识别的十六进制格式,再用专门的编程器将其烧写到FLASH芯片中保存。该方法的实现需要使用专门的FLASH烧写器,实际应用中较为不便,本工程中,在CCS环境下,通过JTAG口,完全由DSP控制对FLASH进行烧写和擦除,实现了对外部FLASH的在线编程。

由于烧写是在CCS程序中实现,所以首先要把。out格式的目标文件转换为工程中可包含的。h文件。根据前面提到的方法,需要把工作程序编译后得到的代码段和数据段分别写进FLASH中的不同地址,这就需要将COFF文件中的代码段和数据段分别提取出来。具体做法是:使用CCS中"FiIe-Data-Save"分别把代码段和数据段保存为dat文件(code.dat和data.dat),代码段和数据段的具体起始地址及长度可以参考程序连接后自动生成的连接过程结果说明文件(后缀为。map,其中记录了段的各种详细信息,从中还可以知道各段的地址分配是否正确)。虽然保存下来的代码段和数据段都是。dat格式,但其内容已经是我们所需要的DSP工作需要的底层机器码,所以只需要将其作为一个数组的内容,再给数组加上合适的类型定义,就可以直接将其格式改为能在CCS工程中直接调用的。h文件(code.h和data.h)。这样也就巧妙地解决了格式转换问题。

1.3 烧写FLASH

TI公司提供了一个烧写FLASH的软件,但是那需要将程序编译后生成的OUT文件再转换成ROM格式;或者是先将应用程序编译后导出到一个二进制文件中,再通过CCS编程序从这个二进制文件中一个一个的读入并写进FLASH.

有了。h格式的烧写文件,下面就只需要再编写一个用于擦除和烧写FLASFI的DSP工作程序,由DSP控制并通过JTAG线操作FLASH芯片,烧写和擦除时要按照FLASH芯片手册中的要求先向指定地址写入指定关键字。注意代码和数据应分别写入FLASH中相应的存储地址。以上三步完成后,DSP就可以在重新加电时实现自动引导:首先从地址0x1400000处搬移64 KB初始化程序到片内运行,然后再从地址0x1410000处加载剩余的代码和数据。

2 结 语

实际工程中的应用证明了上述方法可以使TMS320C6701在脱离上位机的情况下实现上电后自动加载运行,并且稳定可靠,操作方便,使用JTAG线和仿真器就可完成所有操作。该方法只要对一些存储空间的配置稍作修改即可用于C6000系列其他DSP芯片的自动加载。另外,本文思路也可推广到其他DSP芯片的自动加载设计中。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。