l 引言

视频监控系统是安全防范系统的重要组成部分,也是一种防范能力较强的综合系统。视频监控系统以其直观、方便、信息内容丰富而广泛应用于许多领域。近年来,随着计算机、网络及图像处理、传输技术的飞速发展,视频监控技术也得到长足的进步,集多媒体技术、数字图像处理和远程网络传输等技术为一体的多媒体数字监控系统正在逐步取代传统的模拟视频监控系统。目前,市场上专用的视频压缩电路只能实现一种压缩算法,灵活性和可扩展性较差,基本不具备在此基础上进行二次开发的能力;各种基于ISA、PCI等总线的图形采集卡也能在市场上买到,但价格较贵,且处理功能简单,二次开发效率低,不能很好地满足用户的特殊需要。

为了适应多媒体通信技术的发展,美国德州仪器公司推出一款针对视频和图像解决方案的TMS320DM642型高性能数字媒体处理器,它是TI公司C6000系列DSP中的定点DSP,其是C6416型高性能数字信号处理器,具有极强的处理性能、高度的灵活性和可编程性,同时外围集成了非常完整的音频、视频和网络通信等设备及接口,特别适用于机器视觉、医学成像、网络视频监控、数字广播以及基于数字视频/图像处理的消费类电子产品等高速DSP应用领域。

2 DM642简介

DM642DM采用第二代高性能、先进的超长指令字velociTI.2结构的DSP核及增强的并行机制,在720 MHz的时钟频率下,其处理性能为5 760Ml/s,使得该款DSP成为数字媒体解决方案的产品。它不仅拥有高速控制器的操作灵活性,而且具有阵列处理器的数字处理能力。DM642的外围集成了非常完整的音频、视频和网络通信接口,主要包括:

3个可配置的视频端口(VPORTO-2),能够与通用的视频编、解码器实现无缝连接,支持多种视频分辨率及视频标准,支持RAW视频输入/输出、传输流模式;1个10/100Mb/s以太网接口(EMAC),符合IEEE 802.3标准;1个多通道带缓冲音频串行端口(McASP),支持I2S、DIT、S/PDIF、IEC60958-1、AES-3、CP-430等音频格式;2个多通道带缓冲串行端口(McBSP),采用RS232电平驱动;1个VCXO内插控制单元(VIC),支持音/视频同步;1个32位、66MHz、3.3 V主/从PCI接口,遵循PCI2.2规范;1个用户可配置的16/32位主机接口(HPI);1个16位通用输入/输出端口(GPIO);1个64位外部存储器接口(EMIF),能够与大多数异步存储器(SRAM、EPROM)及同步存储器(SDRAM、SBSRAM、ZBT SRAM、FIFO)无缝连接,可寻址外部存储器空间为1 024MB;1个具有64路独立通道的增强型直接内存访问控制器(EDMA);1个数据管理输入/输出模块(MDIO);1个I2C总线模块;3个32位通用定时器;1个符合IEEE 1149.1标准的JTAG接口及子板接口等。有关DM642的详细性能介绍请参照其数据手册。

3 系统功能与硬件电路设计

3.1 系统总体结构

系统总体结构如图1所示,图像采集和预处理单元主要完成图像信号的输入,具有多路信号复用功能,对输入的模拟视频信号进行数字化及格式的转变。FPGA控制系统的逻辑和图像数据的流向,并且可对DM642输出的图像数据进行加工,进而输出到图像编码单元。图像处理单元采用DM642进行高速数据处理和分析。图像编码单元对图像数据进行编码,形成标准的模拟视频信号,可以直接输出到显示设备上。

对于4路视频和4路音频信号,CPU在1个时刻只能处理1路数据,DM642片外位于EMIF的CEO地址空间扩展了2个4 Mx32 bit的SDRAM,可分别存放图像采集数据和图像处理数据,以提高数据采集和存储速度。

3.2 视频口接口设计

DM642有3个视频口,每个都可以配置为上下2个通道,但2个通道必须同时为视频输入口或输出口。结合实际应用,DM642带了4路模拟视频输入(cif格式,分辨率为352288)和1路模拟视频输出。

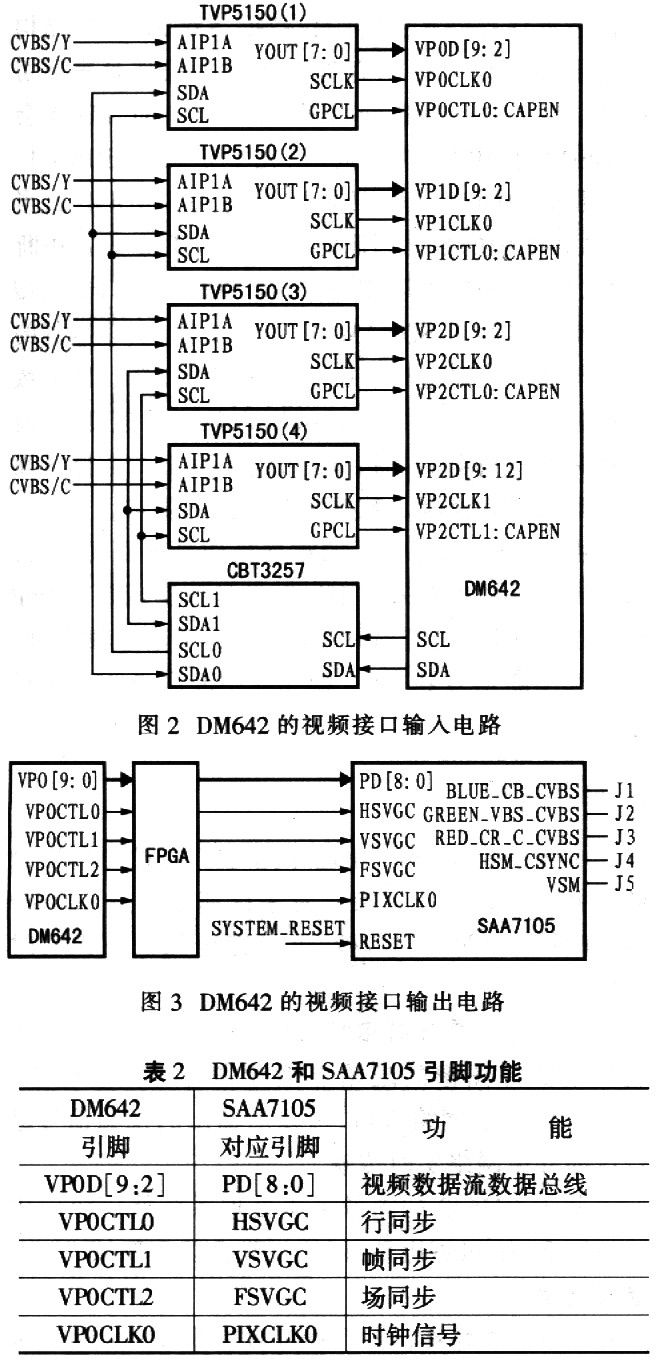

VPO A通道配置为8-bit BT.656视频输入或输出口,接通道视频输入或视频输出。VPl A通道配置为8-bit BT.656视频输入口,接第二通道视频输入。VP2 A和B通道配置为2个8-bit BT.656视频输入口,接第三和第四通道视频输入。VP0和VPI的B通道配置为MCASP,接4个音频Codec。

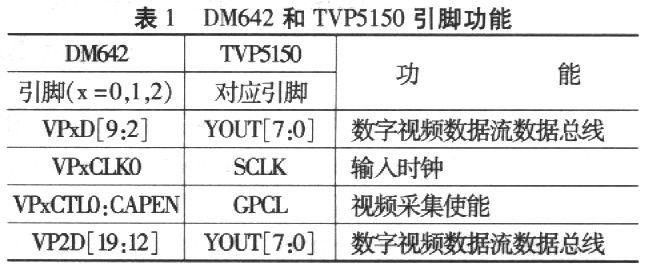

TVP5150型视频编码器支持PAL/NTSC、CVBS或Y/C模拟视频输入,8-bit BT.656数字视频数据流输出。SAA7105型视频解码器支持8-bit BT.656数字视频数据流输入,PAL/NTSC CVBS或Y/C模拟视频输出。通过DM642的I2C总线对视频编/解码器的内部寄存器进行编程,实现不同的输入输出。DM642和TVP5150的对应引脚功能见表1。

视频编解码器的参数通过I2C总线配置,由于TVP5150的I2C从地址只有2种选择,因此需要用CBT3257型2选l转换开关来切换。

作为视频输入口时,视频数据的行/场同步又包含BT.656数字视频数据流中的EAV和SAV时基信号控制,视频口只需视频采样时钟和采样使能信号(控制采样起始),TVP5150用系统时钟SCLK提供采样时钟,用可编程引脚GPCL提供采样使能。作为视频输出口时,视频口要为SAA7105提供时钟和行/场同步信号。

在视频输出电路中,J1、J2、J3可配置成RGB输出信号,J2、J3可连接S端子,J1、J2、J3、J4、J5可直接输出到电脑的显示器上。具体接口电路如图2和图3所示。DM642与SAA7105的对应引脚功能见表2所列。

3.3 多通道音频串口的接口设计

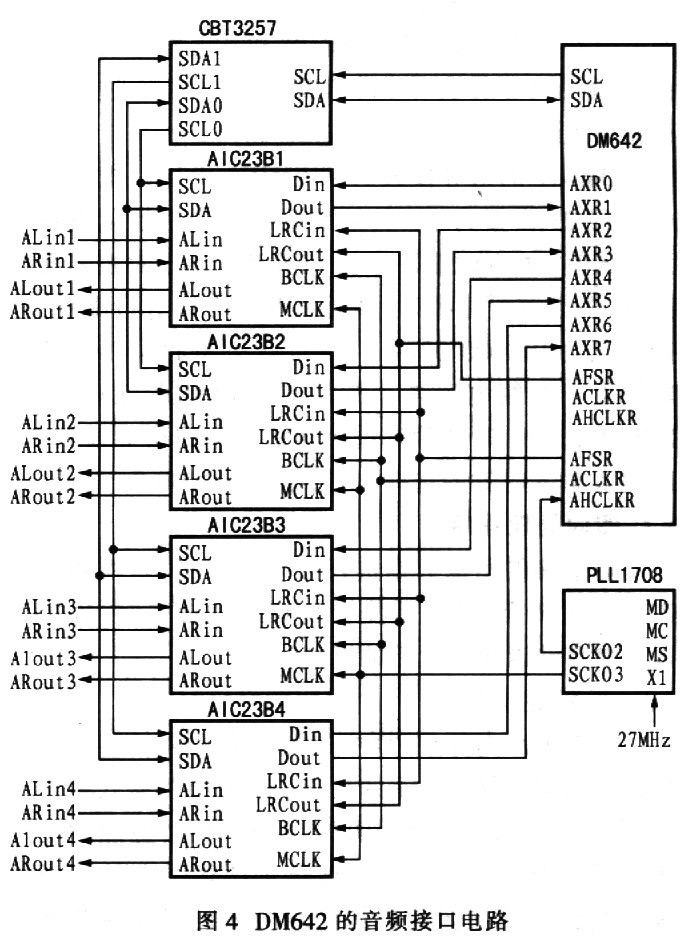

笔者采用了4路模拟音频输入和1路模拟音频输出,采用TLV320AIC23B型音频编/解码器,它支持麦克风/立体声模拟输入/输出和数字音频数据流输出/输入。

PLLl708型可编程视频/音频同步数字锁相环给McASP和TLV320AIC23B提供时钟信号,SCK02端口接McASP的AHCLKX,SCK03端口接TLV320AIC23B的主时钟MCLK。PLLl708的时钟输入为27 MHz。DM642与TLV320AIC23B的对应引脚功能见表3。

AIC23B数据口配置为从,McASP的8个收/发引脚配置为4收/4发,分别接4个编解码器的Dout/Din。McASP的接收帧同步配置为输出,同时给4个编解码器的LRCout。McASP的发送帧同步配置为输出,同时给4个编解码器的LRCin。McASP的发送位时钟ACLKX配置为输出(由AHCLKX分频),同时给4个编解码器的BCLK。AIC23B的控制口配置为I2C,由CBT3257型2选1开关来切换。具体电路如图4所示。

另外,给DM642供电时应注意CPU的上电次序:CHU内核应先于I/O上电,后于I/O掉电,CPU内核与I/0应尽可能同时供电,二者的时差不能太大(<1 s),否则会影响器件的寿命或损坏器件。用可编程时钟电路可很好地解决整个电路的时钟问题。

4 系统软件设计

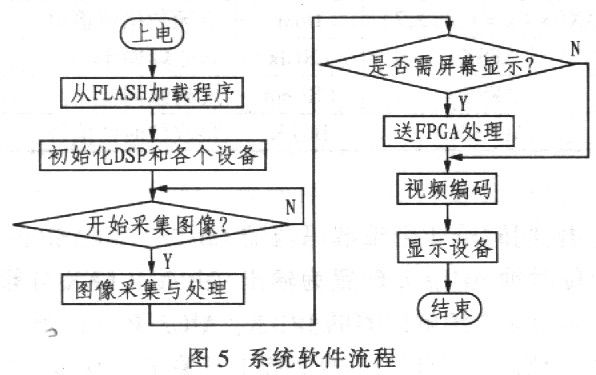

系统软件包括系统初始化设置、图像处理算法和屏幕叠加程序,具体软件流程如图5所示。

4.1 系统初始化设置程序

对整个硬件系统进行初始化,其中包括DM642的上电初始化、DM642的寄存器和系统配置引脚的设置、利用I2C总线对TVP5150和SAA7105进行寄存器设置。

DM642的引导模式为从EMIFA引导,把引脚AEA[22:21]设置为ll,其他配置引脚的初始化设置为默认值。外围配置寄存器(PERCFG)用于对控制视频口、多通道缓冲串口、多通道音频串口进行配置,初始化为0x0000 0079h。设备状态寄存器(DEVS-TAT)用于控制电路各个外围设备的状态:EMAC、HPI、PCI、CPU时钟频率选择模式、电路引导模式、EMIFA输入时钟的选择,初始化为0x0000 005Ch。

4.2 图像处理程序

对采集的图像数据进行处理和分析,对视频流进行格式转换,可以是复合视频或分量视频,也可以压缩存储以便于此后的浏览。

4.3 屏幕叠加程序

把FPGA内部FIFO中的数据和视频口输出的数据混和完成屏幕显示的功能。屏幕叠加有几种方式,背景为透明的、半透明的、不透明的,叠加的位置也可任意设置,只需修改叠加图像的起始点坐标,把相应的图像信息加到对应的视频图像队列中。

4.4 视/音频信号采集存储与图像数据读取程序

对于4路视频信号和4路音频信号,CPU在1个时刻只能处理1路数据,因此在DM642片外扩展了2个4Mx32bit的SDRAM,在系统工作的任一时刻,一个用于图像的采集,采集部分向该存储区写图像数据,另一个用于外部对图像数据的读取,DSP可以读取该存储区中的图像数据。双SDRAM结构的重要特点是DSP对存储区的数据操作是来回切换的。当A/D转换数据写满SDRAM-l时,FPGA会向DSP发出中断信号,此时,在DSP读取SDRAM-l中数据的同时,A/D转换数据写入SDRAM-2,当SDRAM-2中的数据写满时,FPGA向DSP发出中断信号,此时DSP读取SDRAM-2中的数据,同时,A/D转换数据写入SDRAM-l,如此交替,实现数据的写入与读取同时进行。由于DSP读取SDRAM中数据的速度远远大于A/D转换写入数据的速度,因而允许采集与外部访问同时进行,采用2个存储区操作的乒乓式切换满足数据实时交换的要求。

由于DSP对存储区的数据操作是来回切换的,因此需要采用中断来实现取数。具体实现是在DSP内部设置中断,这里选用INT6作为中断触发引脚。当外部中断信号到来时,则相应中断服务程序执行中断响应。

5 结束语

本系统能够同时处理4路CIF格式的数字视频,并且可以动态切换,总采样速率可达100帧/秒,每路速率为25帧/秒,可以完全保证图像实时采集。

对图像的叠加有多种方法,叠加的位置也可通过修改叠加图像的起始点坐标来进行任意设置。DM642还具有网络接口,可以对输出的视频信号进行压缩并由网络实时传输。

基于DM642的图像采集处理系统能广泛应用于机顶盒、IP可视电话、网络视频会议等领域。

[1]. PCI datasheet https://www.dzsc.com/datasheet/PCI_1201469.html.

[2]. TMS320DM642 datasheet https://www.dzsc.com/datasheet/TMS320DM642_14462.html.

[3]. RS232 datasheet https://www.dzsc.com/datasheet/RS232_585128.html.

[4]. EPROM datasheet https://www.dzsc.com/datasheet/EPROM_1128137.html.

[5]. TVP5150 datasheet https://www.dzsc.com/datasheet/TVP5150_665572.html.

[6]. SAA7105 datasheet https://www.dzsc.com/datasheet/SAA7105_1097495.html.

[7]. CBT3257 datasheet https://www.dzsc.com/datasheet/CBT3257_212808.html.

[8]. TLV320AIC23B datasheet https://www.dzsc.com/datasheet/TLV320AIC23B_10162.html.

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。