1 引言

由于短波通信具有通信距离远和信道不易摧毁等优点,它历来是政府、军事、外交、气象、商业等部门必要的通信手段。基于超外差理论的短波模拟接收机至今已有80多年的历史,其技术已相当成熟。归纳起来性能可达到如下水平:接收频段从5kHz到30MHz,调谐通常可达10Hz;音频处理带宽从 300Hz到16kHz,可有5种选择或略多一些;解调方式有调幅(AM)、等幅报(CW)、调频(FM)、单边带(SSB)和独立边带(ISB)等几种。众所周知,超外差接收机是将接收到的射频信号变换到频率为455kHz的中频(IF)信号,之后的放大、滤波和解调等都在该IF段利用模拟电路来完成。在这类模拟接收机中一直存在的问题是模拟滤波器的种类不可能太多,一部接收机由于体积所限,至多装入5~6个滤波器,其抗干扰分辨性能是相当有限的;解调方式仅限于几种,缺乏灵活应变性;对工作频带内的窄带干扰无能为力,接收微弱信号的能力低,否则模拟电路将变得十分复杂。

在信息爆炸的现代社会里,短波通信越来越广泛地在政府、军事、外交、气象、商业等部门得到应用,这就使短波波段的电台变得越来越拥挤,相互间的干扰也越来越严重,传统的模拟接收机已经难以适应现代短波通信的需求,所以,必须研制新一代的短波接收机,即短波数字化接收机。

随着数字信号处理器(DSP)运算速度的日益提高,高大动态范围模拟数字转换器(A/D)的出现和广泛使用,采用数字运算方式来处理IF信号已经提到了日程[1~5]. 近几年来,美国和德国一些比较着名的接收机厂商已经推出了他们的数字化接收机产品,例如美国WJ-8711、8712、8712P、9103短波数字化接收机等。这些接收机的共同特点是,在接收机进入数字化处理之前,接收机前端包括变频、滤波以及高中频放大,采用数级模拟电路,后续电路包括变频,中频放大,中频滤波和解调等采用高速数字信号处理器代替原来的许多模拟模块,接收机中的所有控制电路,如调谐、增益控制、带宽、静噪、解调方式选择、AGC时间常数选择等均实现数字控制。采用数字信号处理技术以后,数字滤波器(FIR,IIR)、精密正弦波发生器、多种解调算法都可以方便灵活运用。接收机厂家可以通过DSP软件的升级和版本的更新,方便地提高设备的性能和增加设备的功能。在短波通信领域广泛使用的便携式战术接收机目前国内尚无数字化的替代产品;TI公司在90年代中后期推出了高性能、低功耗、低价位的C2XX系列DSP芯片,从而使便携式战术接收机的数字化成为可能。本文介绍的用TI公司的TMS320C203来完成战术接收机数字化改造的解决方案。

2 TMS320C203芯片介绍

该战术接收机中使用了16位定点、40MIPS的TMS320C203DSP,这种DSP产品价格低廉,因而具有较高的性能价格比。该系列芯片是基于C5X系列的结构而设计的,因而大大节省了功耗和芯片体积。

C2XX系列DSP芯片采用改进的哈佛结构,这种结构的程序存储器和数据存储器的内部总线是分开的。各型号具有相同的CPU和总线结构。其CPU包括:32-bit算术逻辑单元CALL、32-bit累加器、16×16bit并行乘法器、32-bit乘积结果、3个定标器和8个16-bit辅助寄存器,且带有数据空间间接寻址用的专用算术单元;

程序控制部分提供了指令执行的4级流水结构,8级硬件堆栈和用户禁止中断线。程序控制部分的指令包括有指令操作、单周期乘法/累加指令、存储器块推移指令和检索寻址等。

C2XX系列的寻址空间为224kB,其中程序空间、数据空间和I/O空间各占64kB,全局空间占32kB(主要用于程序和数据引导)。在C203中具有544B的双访RAM(在一个指令周期内可以被访问两次,但至多允许写操作)可以分为B0、B1和B2三块。B0块长256B,被配置为片内程序/片内数据空间;B1块长256B,只能配置在数据空间(可间接寻址和页寻址,不能直接寻址);长32B的B2块只能配置于数据空间(地址为60H~7FH),可直接寻址)。

C203中具有一个片内16bit定时器,可用于程序、数据和I/O空间的软件可编程等待状态发生器(0~7个等待状态),以及时钟选择的片内振荡器和锁相环。为提高系统运行的稳定性,一般都使用锁相环方式。

C203提供的42个通用中断包括RS、INT1、INT2及不可屏中断NMI.RS为中断0,用于上电复位时将程序和数据从ROM中引导入RAM,INT1和INT2虽然各有引出脚等外设连接,但它们共用同一个中断向量。在C203内部还集成有一个同步串行口和一个异步串行口。

与C50相比,C203也具有自己的一些缺点:

⑴不能自动保护现场而必须由用户自己缺点:

⑵无桶形移位寄存器,滤波时不能对程序空间中的滤波器系数自动地实现寻址的首尾衔接;

⑶不能提供指令块重复执行功能。

以上这些特点决定了C203指令的执行效率要低于C50.

3 DSP处理模块硬件方案

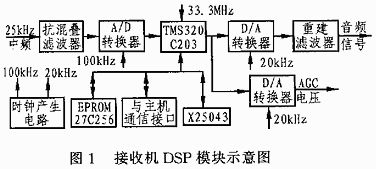

战术接收机DSP处理模块的硬件组成如图1所示。25kHz中频信号首先由轨对轨运放TLC2272进行低通放大,然后经过8阶巴特沃思型开关电容滤波器MAX295的抗混叠滤波,再经匝数比为1:1.8的变压器完成单双极转换后送往A/D转换器。图1中的A/D转换器为16位、并行输出的AD976A(功耗为100mW),其允许的采样率为200kSPS,对输入模拟电压的转换时间为4μs.重建滤波器采用MAX295,它输出的模拟信号一路是AGC电压,用以控制DSP板以前的放大器的增益;另一路为音频信号。选用的D/A转换器是12位的并口AD8582(功耗仅10mW)。

由于该电路相对比较简单,因而控制电路和时钟产生电路均采用74系列的CMOS芯片。EPROM27C256中存放有程序、4kB的正弦表和4kB的反正弦表以及各种滤波器系数。X25043为低电平复位的具有电压监控功能的E2PROM,该器件内部同时还集成了可编程看门狗定时器。X25043及其附属电路主要用于完成以下两个功能;

⑴系统上电复位时,将程序和数据从27C256引导至RAM中,平常则监控DSP的工作电压。

⑵存放校准滤波系数。校准时,该滤波器系数从X25043中调到DSP的双访RAM中,以准备进行校准滤波。

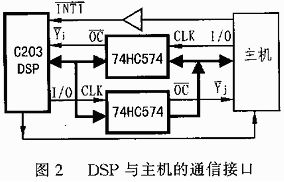

DSP与主机的通信接口如图2所示。由于成本、功耗和电路板面积的限制,电路中没有使用双端口RAM,而是采用两74HC574来形成与主机通信的双向通路。采样数据的接收采用中断方式,实际占用的是中断口2.而DSP则利用中断口1来接收主机所需发送的命令。

4 软件方案

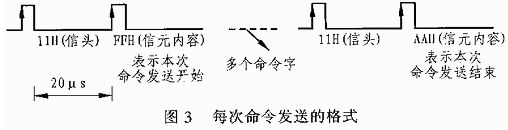

TMS320C203以中断方式1接收主机命令,由于主机的中断口均已被占用,因而其指令执行速度也远远慢于DSP.因此,主机采用查询方式接收DSP的返回信息(并口)。此时74HC574只相当于的缓冲,在下次写脉冲到来以前,其中的信息必须被取走,另外,还应当保证信息的保存时间不超过20μs,其命令发送格式如图3所示。

由于每次命令发送中都包含多个命令。且每一个命令字都包括一个信头标识和多个信元(总长多为4字节),因此接收命令的中断服务程序中设立了5单元的接收缓冲区和30单元的命令放置区。命令字的信头标识具有两个作用:

⑴以信头标识为偏址的命令字长度表为参照得出该命令令字长度。

⑵若DSP已收完该命令字,则将接收缓冲区中的各字节按含义拼装为字,并以信头标识为偏址,命令放置区首址为基础存入到命令放置区。

为确保命令传送的可靠性,该系统采用部分反馈重传的机制,即让DSP将工作方式字和解调方式字等重要命令回传给主机,主机再将其与近发送的对应字进行比较,若有差别,则认为出错并重发。当然,在通信程序中还应包含其它的容错处理。

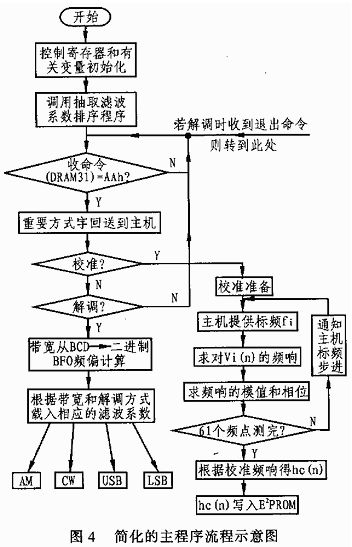

接收A/D采样数据采用中断2,由于要进行降5的抽取,因此,中断服务程序要对接收的数据个数计数,以在各解调程序中判断是否已收到5个采样数据。若是,则作解调处理,否则等待。解调程序运行一周所需的时间必须少于50μs,以便对下次收到的5个采样数据进行及时地处理。图4为简化的主程序流程示意图。

5 结束语

在短波数字化战术接收机研制过程中,由于所选的廉价DSP芯片不能全面运行,而且片内资源较小,因此笔者经过多次努力压缩运算量,解决了低噪声过大所造成的性能不高的问题。目前,该样机在灵敏度、动态范围、群时延、音频响应以及大信号信噪比等诸多关键指标上均优于同类的模拟机,而且体积减少了二分之一,重量减轻了三分之一,整机功耗被控制在5.5W.该样机已通过用户验收并以其性能好、功耗低、重量轻、便于野外作用而得到用户的好评,全面完成了对短波接收机系列化的数字化改造。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。