TI公司推出的16位定点运算数字信号处理器(DSP)TMS320C2XX,目前已成为单片机的理想替代品,在语音处理、军事、图像处理等领域得到了广泛的应用。在以TMS320C2XX为的数字化语言学习系统中,为了满足系统实时性要求,声卡与存储器之间的数据传送已经不能采用程序查询控制方式,所以我们采用直接存储器访问(DMA)控制。直接存储器访问控制是指数据传送时不需要CPU的介入,I/O设备和存储器直接交换信息。DMA方式的数据传送与程序查询方式的数据传送相比,具有数据传送速度高、I/O响应时间短、CPU额外开销小的明显优点。本文通过分析TMS320C2XX使用保持(HOLD)操作的直接存储器访问(DMA)和DMA控制器8237-5的工作原理,解决了DSP芯片TMS320F206与DMA控制器8237-5的软、硬件接口问题,实现了DMA在数字化语言学习系统中的应用。

1 TMS320C2XX使用HOLD操作的直接存储器访问

TMS320C2XX的主要特点是采用了改进的哈佛结构,片内具有相互独立的六条总线(三条内部地址总线:PAB、DRAB、DWAB;三条内部数据总线:PRDB、DRDB、DWEB),不仅使程序存储器与数据存储器的访问相互独立,且使数据存储器的读和写也相互独立并能同时执行,从而极大地优化了运算处理能力。

TMS320C2XX具有逻辑扫描电路,该电路与IEEE标准1149.1兼容,并通过八个专门引脚与外部14引脚的JTAG接口相连。通过JTAG接口可完成以下工作:(1)可对芯片引脚进行测试;(2)可对外部Data空间及I/O空间进行检测;(3)可对芯片内部FlashMemory进行编程;(4)可对片内片外RAM加载数据;(5)可进行在线运行仿真。以上特点给硬件的调试及软件的开发带来很大便利。

TMS320C2XX的HOLD操作允许对外部程序、数据以及I/O空间进行直接存储器访问。该过程由/HOLD/HOLDA两个信号控制。

(1)/HOLD.外部设备可以把该引脚驱动到低电平从而请求对外部总线的控制。如果HOLD/INT1中断线被允许,那么将触发中断。

(2)/HOLDA.在响应/HOLD中断时,软件逻辑可以使处理器发出/HOLD应答信号,表示它将放弃对其外部总线的控制。根据/HOLDA,外部地址信号(A15~A0)、数据信号(D15~D0)以及存储器控制信号(/PS,/DS,/BR,/STRB,R/W,/RD,/WE)被置为高阻状态。

在本设计中,HOLD/INT1中断服务子程序只用于HOLD操作以便控制DMA传送,因此DSP的断控制寄存器(ICR)中的方式(MODE)位置为0.此时,中断线INT1对下降沿和上升沿二者都敏感。当CPU检测到下降沿时,它完成正在执行的挡前指令,然后迫使程序控制转到中断服务子程序。在成功的测试到MODE=0之后,此子程序执行IDLE(空闲)指令。根据IDLE,/HOLDA变为有效而外部总线被置为高阻状态。只有在检测到HOLD/INT1引脚上的上升沿之后,CPU才退出IDLE状态,/HOLDA变为无效,并使外部总线返回到正常状态。

HOLD操作的子程序将在本文结合具有本示例中给出,需注意的是:IDLE指令应当放在断服务子程序内以便发出/HOLDA.同时要注意的是:中断程序代码禁止除HOLD/INT1之外的所可屏蔽中断,从而允许/HOLDA和总线的安全恢复。

2 DMA控制器8237-5的工作原理

8237-5是一个高性能的40引脚双列直插式可编程DMA控制器芯片,可以方便地与DSP微处理器相连,实现我户口设备与存储之间数据交换。该控制器通过编程可提供多种类型的控制特,以优化系统性能,增大数据吞吐量,数据传输速率可达1.5MB/S.

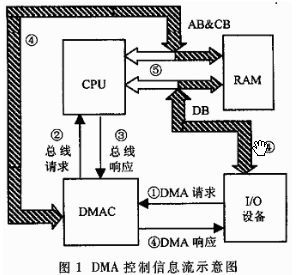

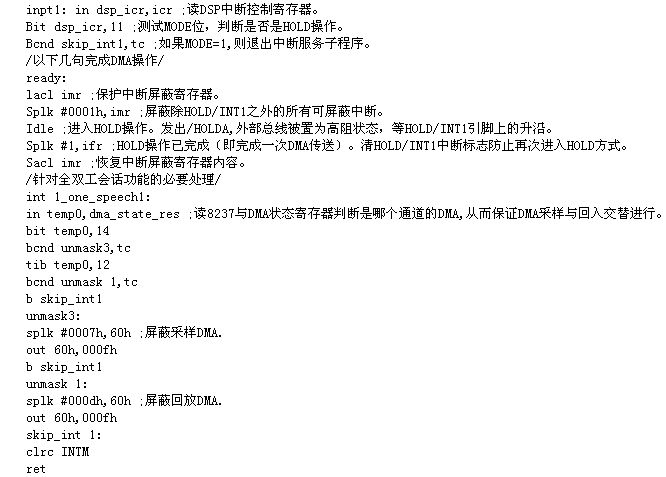

DMA控制器实现DMA传送的控制原理可用图1的信息流示意图表示。现结合该图将DMA控制原理操作顺序说明如下:

①I/O设备准备好后,向DMA控制器(DMAC)发出DMA请求信号DMARQ.

②DMAC向CPU发出总线请求信号BUSRQ.

③按照预定的DMAC占用总线方式,CPU响应BUSRQ,向DMAC发出总线确认信号BUSAK.从这时起,CPU总线控制权交由DMAC接管,开始进入DMA有效周期,如图1中阴影部分所示。

④DMAC接管总线后,先向I/O设备发出DMA请求的响应信号DACK,表示允许外设进行DMA传送。然后按事先设置的初始地址和需传送的字节数,依次发送地址和读写命令,使RAM和I/O设备直接交换数据,直至全部数据交换完毕。

⑤DMA传送结束后,自动撤消向CPU的总线请求信号BUSRQ,从而使BUSAK和DACK相继变为无效,CPU又重新控制总线,恢复正常工作。

3 DSP与DMA控制器8237-5的接口电路

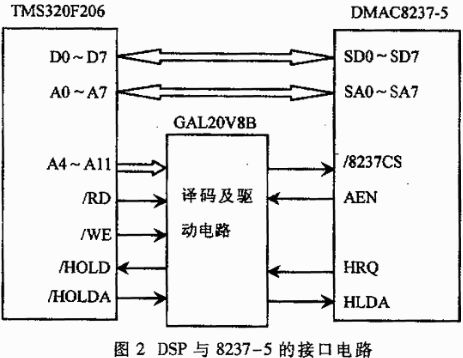

通过上述分析可以知道,DSP与8237-5的接口关键是要解决DSP的/HOLD、/HOLDA信号与8237-5的总线保持请求输出信号HRQ(即BUSRQ)、总线保持响应输入信号HLDA(即BUSAK)之间的联系问题。图2给出DSP与8237-5的接口电路。

(1)数据线、地址线可以直接相连,8237-5仅使用8根据数据线和地址线。

(2)由于8247-5要向DSP申请对外部总线的控制,所以DSP的/HOLD信号决定于HRQ,而二者的有效电平正发是反相关系;另一方面,当DPS在合适程序代码的协助下使/HOLDA有效,从而对/HOLD有效作出响应时,它就应该通知DMAC可以获得总线控制权。因此HLDA、/HOLD信号线的译码逻辑关系如下:

HLDA=/HOLDA

/HOLD=HRQ

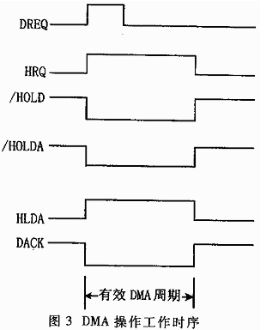

DMA操作的时序关系如图2所示。

可见,当8237-5任一通道的DREQ被置为有效电平且相应通道的屏蔽位被清除时,就使HRQ信号变为高电平,从而使DSP的/HOLD变低,表示有外部设备请求对外部总线的控制。随即DSP发出/HOLDA来响应/HOLD,8237-5的HLDA变高,取得总线控制权,并产生相应的DMA响应信号DACK以通知外设。完成DMA周期后,总线又回到正常状态。

4 软件编程

实现DMA控制方式的软件编程主要包括DMA控制器8237-5的初始化、DSP的HOLD操作以及外设初始化相关设置等三部分。根据所实现的具体功能不同,各部分的一些细节可以有所区别。

下面给出DMA控制方式在以DSP为的语言学习系统中的一个具体应用。它可以实现DMA方式的采样和回放,用于两个人之间的全双工会话功能。所用外设是声卡。由于要同时进行采样和回放,所以8237-5需要使用两个DMA通道。

4.1 8237-5的初始化

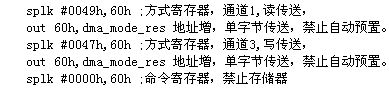

根据全双工会话功能的具体要求,本例程的方式寄存器和命令寄存器初始化如下:

out 60h,dma_command_res 到存储器传送,禁止通道0地址保持,允许芯片工作,正常时序,固定优先级,滞写入选择,DREQ高电平有效,DACK低电平有效。

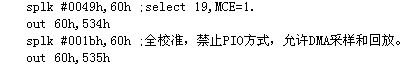

4.2 声卡初始化中的相关设置

声卡一般默认DMA0=1为回放通道、DMA1=3为采样通道,这在其PNP初始化中规定。19寄存器用于禁止声卡并行传送方式,启动DMA方式:

声卡还有几个与DMA操作有关的寄存器:I14、I15、I30、I31.I14、I15用于设定DMA回放的计数其值,I30、I31则用于设定DMA采样的计数基值。它可以产生一个中断以方便用户做相应处理。

4.3 DSP的HOLD操作中断服务子程序

5 结语

DMA控制方式在DSP中的成功运用解决了系统中存储器与外设之间数据传送的速度问题,极大地减轻了CPU的负担,实现了DSP对声卡DMA方式的录音与回放、立体声及全双工操作,可以很方便地实现全数字化语言学习系统的各项功能。

[1]. TMS320F206 datasheet https://www.dzsc.com/datasheet/TMS320F206_17297.html.

[2]. A15 datasheet https://www.dzsc.com/datasheet/A15_1244519.html.

[3]. D15 datasheet https://www.dzsc.com/datasheet/D15_1092218.html.

[4]. DMAC datasheet https://www.dzsc.com/datasheet/DMAC_1401012.html.

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。