数字技术的出现与应用为人类带来了深远的影响,人们如今已生活在一个几乎数字化的世界之中,而数字音频技术则称得上是应用为广泛的数字技术之一,CD、 VCD等早已走进千家万户,数字化广播正在范围内逐步得到开展,正是这些与广大消费者密切相关的产品及应用促使数字音频压缩技术得以产生和发展。

随着数字语音压缩技术的应用领域越来越广,将高质量语音编码算法实用化的需求也越来越迫切。16kbit/s LD-CELP ITU-T G.728语音编码标准,采用后向自适应技术,单向编码延迟小于2ms,主观评价MOS分4.0,达到进入公众通信网的需求,因而广泛适用于数字卫星系统、数字线路倍增设备(DCME)、综合业务数字网(ISDN)、公共交换电话网(PSTN)、话音存储转发系统等。但其算法复杂度高,运算量庞大,定点实现时,一路全双工约需30~40MIPS.一般通用的数字信号处理器(DSP),只能做到一片DSP实现一路G.728语音编解码。

TMS320C6201是TI公司推出的C6X数字信号处理芯片系列中具代表性的定点处理芯片。由于内部含有具备超长指令字(VLIW)处理能力的CPU和8个功能单元,故它可在一个时钟周期内执行多达8条指令。此外,1M位的片内RAM、可扩展的外部RAM接口和灵活的外围设备使其成为实现具有高速运算的复杂处理系统的芯片。

本文研究了在单片TMS320C6201芯片上实时实现ITU-T G.728语音编码标准,实验结果表明,单片TMS320C6201能实现至少4路语音编解码。这对于扩展基于G.728标准的单路处理系统的功能或降低基于G.728标准的多路处理系统的系统复杂度都具有现实的意义。

文中将扼要介绍G.728编解码算法和TMS320C6201芯片,并详细讨论G.728算法在TMS320C6201上的实时实现,给出结论。

1 G.728语音编解码原理简介

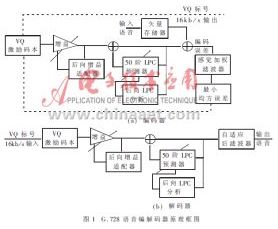

图1给出了G.728语音编解码器的原理框图。

编码器中五个连续语音样点形成一个5维语音矢量。激励码本中共有1024个5维的码矢量,对于每个输入语音矢量,编码器利用合成分析法从码本中搜索出码矢,然后将其标号选出,LP系数和增益均由后向自适应提取和更新。

解码操作也是逐个矢量地进行。根据接收到的码本标号,从激励码本中找到相应的激励矢量,经过增益调整后得到激励信号,将其输入综合滤波器合成语音信号,再经自适应后滤波处理,以增强语音的主观感觉质量。

由于编码器只缓冲5个样点(一个语音矢量),在8kHz的采样率下,算法延迟只有0.625ms,加上处理延迟和传输延迟,故总的单向编码延迟小于2ms.采用后向自适应技术,预测器参数在解码端通过LP分析恢复,不再作为传输内容,编解码器间仅需传送码矢的索引值,故码率为10bit/0.625ms=16kbit/s.

2 TMS320C6201定点数字信号处理芯片简介

TMS320C6201是美国德州仪器公司(TI)推出的含多处理单元的C6X数字信号处理芯片中具有代表性的定点芯片。VLIW结构提供的高输出量、高效开发工具保证的易用性、以及可接受的价格,使得TMS320C6201成为高速运算的理想选择。以下从硬件结构和软件资源两方面,简要介绍TMS320C6201芯片。

2.1 C6201的硬件结构

2.1.1 CPU

采用了VelociTI的VLIW结构,因而在每个时钟周期内多可并行执行八条32位宽(一个字长)的指令,在200MHz的主频下可以得到1600MIPS的高处理速度。CPU中包括了两套对称的运算单元(L,S,M,D)和相应的两套寄存器组,每组有16个32位宽的寄存器。

2.1.2 存储空间

C6201的地址总线为32位,寻址范围达到4GB.存储空间可分为四部分:片内程序空间、片内数据空间、外部存储空间和内部外围设备空间,可通过对五个BOOTMODE引脚的灵活设置设定各空间的地址范围。片内数据空间分成四个8K×16的交织块,使得CPU可同时访问数据RAM的两个块而不会发生冲突。片内程序空间可设为Cache ,存储经常使用的代码,减少片外访问次数,从而提高程序运行速度。

2.1.3 外设

C6201的外围设备包括DMA控制器、主机接口(HPI)、中断选择等。两个多通道缓存串行口(McBSP ,除多通道、双缓存外,还支持多种数据格式、硬件A/μ率压扩、位时钟和帧时钟的灵活编程。

2.2 C6201的软件资源

2.2.1 丰富的指令

C6201的指令集共有五十余条指令,大部分是单周期的,可完成数据传输、算术逻辑运算和程序控制等功能。指令支持8/16/32位数据存取,给不同结构的数据操作带来方便。由于多处理单元的采用,在无资源冲突下,C6201多可并行执行8条基本指令。

2.2.2 流水线操作

流水线操作和超长指令字是C6201的高性能特点。其指令执行可分为四个步骤:取指(Fetch)、指令拆装(Dispatch)、译码(Decode)、执行(Execute)。流水线操作即指以上四个步骤的并行操作。由于引入了多单元结构和超长指令字,所以和常见的数字处理芯片相比,多了一个指令拆装的过程。

2.2.3 灵活的寻址方式

C6201支持多种寻址方式,如寄存器寻址、直接寻址、短立即数寻址、长立即数寻址和相对寻址。此外,它还提供循环寻址方式,适用于相关和卷积运算中的存储器寻址。

3 G.728在TMS320C6201上的实时实现

3.1 硬件结构

由上面介绍的TMS320C6201的结构特点可见,以C6201为器件,辅以相应的输入输出电路,可完成对单路语音信号的实时编解码工作,同时具备多路(如T1/E1群)语音信号的输入输出接口。

本文应用了TI公司的TMS320C6201EVM板。板上配有单片TMS320C6201和与串口McBSP0连接的16位A/D芯片CS4231.EVM板通过ISA总线与PC机相连,启动时由PC机将程序装载入C6201的片内存储空间,在C6201全速运行时,PC机可以查询其运行状态,读取压缩后的G.728码流,或送入待解码的G.728码流。串口0接CS4231,用于接收和发送模拟信号;串口1用于接收和发送已压缩的G.728码流,因此系统可仿真实现单路G.728语音编解码。通过进一步对算法复杂度的分析,可判断多路G.728编解码的实现能力。

3.2 软件开发

编解码软件采用定点算法,用标准ANSIC语言和TMS320C6201汇编语言混合编制完成。软件包括主处理程序和中断服务程序,流程图如图2所示。

在编程中,需注意以下几点:

(1)双缓冲区的运用

为实时处理输入语音和合成语音,避免数据覆盖,必须设置两个双缓冲区。对编码过程而言,当串口将语音信号写入输入缓冲区A时,编码器处理输入缓冲区B中已存储的5个语音样点;同理,对解码过程,当串口送出输出缓冲区A'中合成语音时,解码器的输出结果写入缓冲区B'.在中断程序中,计数判断何时切换相应缓冲区。

(2)数据的处理

C6201是定点DSP芯片,为确保运算和防止数据溢出,在实现时主要采用了两种方法:一是对某些要求较高的运算,将计算的中间变量采用32位来表示;二是对于幅度范围变化比较大的变量或数组,如激励增益、50阶杜宾算法的自相关数组等,采用标量浮点或块浮点表示,用一个字存储使该数或数组归一化所需的左移位数(NLS),其余字存储归一化后的尾数。

(3)存储空间的分配

C6201 1M位的片内存储区包括64Kbyte程序空间和64Kbyte数据空间,足够单路G.728编解码算法的使用。但若应用于多路语音处理,则需谨慎分配存储空间。由于编解码程序、常数表格等均可公用,多路应用主要考虑数据空间的使用。对临时变量、数组等采用公共域(UNION)分时存储技术,能有效提高存储空间的利用率,确保全部数据都在片内处理。

(4)计算量的均衡

C6201的高速运算能力,使实现G.728编解码算法不再需要考虑运算量的均衡。但若考虑到与其它实时性要求高的控制处理模块协调工作,则仍需按标准中介绍的方法均衡运算量。

3.3 软件优化

TMS320C6201的代码开发流程与传统DSP截然不同,它是一个不断调整C代码与线性汇编代码比例的过程,力求在性能与开发周期上寻得平衡点。代码开发有三步:

步,在通用的C平台上开发ANSIC代码,调试通过后不做任何变化地移植到C6201开发平台上,由C编译器完成所有的优化。利用测试工具判断代码性能是否达到要求,从而决定是否需要后续的优化步骤。这一阶段,开发者不需要对DSP有所了解,开发容易,但C编译器优化后的代码并行性差,未能充分利用C6201独特的硬件结构和软件资源,运行效率低。

第二步,优化C代码。在此阶段,开发者应该根据C6201的特点,如充分利用数据宽度、使用内在函数等,对C代码加以改进。这一阶段要求开发者了解C6201DSP并掌握常用的技巧。经过此步优化后,代码的效率将大幅度提高。

第三步,编写线性汇编代码。当上一步的优化仍不能满足要求时,就必须把那些对效率影响重大的模块抽取出来,改由线性汇编语言实现。在这一阶段,编程者一定要对C6201DSP有深入的了解并具备一定的编程经验,才能较好地解决诸如资源分配、消除数据的关联性等关键问题。此步优化难度较大,但运用于模块,能显着提高代码的并行性。

在TMS320C6201优化G.728代码过程中,主要应用了以下技巧:

(1)资源分配的技巧

C6201的8个功能单元能并行处理,因此在一个算法中用得多的那个运算单元会构成瓶颈。常发生的是内存访问瓶颈,循环展开是有效的解决方法。充分利用数据宽度,将半字(16bit)访问改用字(32bit)访问就是简单而又有效的循环展开技术。

循环展开是提高资源利用率的主要方法,但它所引起的代码空间膨胀也是惊人的。在编程时,必须在程序空间和程序速度这一对矛盾中作出合适的折衷。

(2) 数据关联性简化的技巧

数据关联性是并行编程中的障碍,有两种典型情况:

① 存在循环反馈路径

此种路径常见于递归算法中。当下的循环中必须读取上循环中产生的数据,就形成了一条循环反馈路径。由于反馈路径不可能消除,的方法是尽量缩短它,减少不可并行的操作。

② 生存期过长

当变量生存期过长时,软件流水化会导致误操作。有两种解决方法:一是循环展开,因为循环展开会增加循环周期数;二是用MV指令增加一个中间变量,使原变量的生存期由两个变量共同承担。

(3) 解决存储空间冲突的技巧

此冲突是引起C6201执行速度急剧下降的主要原因,但在编程时却很容易被忽略。前面介绍的C6201的存储区结构,64Kbyte的片内数据空间分成四块,每一块在每个周期只能被访问,否则就会产生存储空间冲突。执行时,流水线会自动暂停一个周期。

在调试、优化程序的过程中,随时观察有无流水线冲突,通过调整存储空间分配,可基本解决这一问题。

3.4 实验结果

表1给出了G.728编解码算法实时实现时所需的计算量和内存占用状况。在200MHz主频下,TMS320C6201芯片处理能力为200MCPS(Million Cycle per Second ,在充分发挥并行潜力时,可达到1600MCPS(200×8=1600)。由表中可见,G.728算法实现编码需24.4MCPS,解码需14.3MCPS,程序空间和数据空间分别占用55.8Kbyte和11.4Kbyte,故单片C6201可实现四路G.728语音编解码。

对编解码器还进行了实时处理语音性能的实验。以男生、女生、音乐等多种音源输入的实验表明,系统具有良好的适应性。非正式试听测试,恢复语音保留了较好的讲话人特征,具有较高的自然度和可懂度。

ITU-T G.728标准在较低码率下实现了低延时、高质量的语音编解码,在公众通信网中有着广泛的应用。本文在新型TMS320C6201定点DSP芯片上设计了基于G.728的实时语音编解码系统。由于充分发挥了C6201强大的运算能力和系统接口能力,系统构造简单,运行效率高,单片C6201至少能实现四路G.728语音编解码。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。