开放化、高速化和高化都是现代信息技术的发展趋势和研究热点。数据采集系统是通信技术和数控技术领域的重要功能模块,应用领域十分广泛。在许多测量与控制领域,如电力谐波测试、声光信号处理、现代雷达系统等元均要求在线进行小波数字信号分析与处理,其中为关键的是如何利用香农(Shannon)采样理论将外部信号毫无失真地采集并转化为计算机所用的数字信号。目前较为流行的方法是提高A/D的转换速率和计算机的处理速度。同时,提高数据的传输速率也是较为关键的。本文以高速数转换芯片AD1674为基础,采用PCI总线协议,从硬件和软件设计入手探讨提高整个数据采集系统的采样频率和高可靠性的方法,其中有些方法得到了实践证实。

AD1674 是美国AD 公司推出的一种12 位并行模/数转换的单片集成电路。它采用逐次逼近工作方式,转换速度快,采样频率可达100KHZ,且片内自带有采样/保持器和具有三态输出的缓冲器,能使电路设计更为简单且易与各种计算机连接。 AD1674 与原有的同系列的AD574 , AD674A 相比,具有内部结构更加紧凑、集成度更高、工作性能(尤其是高低温稳定性) 也更好, 而且可以使设计板面积大大减小, AD1674 的电源电压有较好的稳定性和较小的噪声,且产生的代码很稳定,因而可降低成本并提高系统的可靠性。

一般而言,触发A/D转换有软件触发、实时器同步触发及外部触发三种方式。而数据的传输方式有软件查询、中断方式、DMA方式及FIFO方式。四种数据传输的速率比较如下(以A/D转换基频10MHz为例):

软件查询 10~20kS/s(每秒10k次,与所用计算机的主频有关)

中断方式 10~30kS/s

DMA方式 200kS/s

FIFO方式(w/repeat input string) 330kS/s

本系统中采用了定时器同步触发A/D与FIFO(带重复字符输入方式)数据传输方式相结合的方法大大提高了系统的采样频率和数据的可靠性,改善了在Windows环境下数据传输的性能。

1 高速连续数据采集系统设计的几项关键技术

1.1 定时触发脉冲源的设计

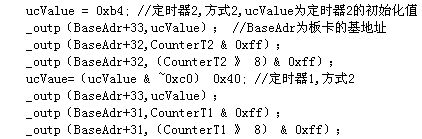

由于系统要求高可靠性、高采样频率以及连续采样,利用Intel 8254定时计数功能来触发A/D转换,严格控制时序以及数据采样间隔,合理利用Intel 8254的三个定时计数器。定时计数器0作备用,用作A/D的外部触发源,定时器1和2配合使用。其中定时器1的输入和定时时钟基频(40MHz)相联,其输出作为定时器2的输入,定时器2的输出作为A/D转换的定时脉冲触发源。

定时器1和2均采用方式2工作。定时计数器1和2的计数值CounterT1和CounterT2,必须满足如下关系式:

CounterT1×CounterT2=时钟基频/SampleSpeed(系统的采样频率)。

其初始化程序如下(编程平台为Visual C++6.0):

1.2 双端口RAM技术

系统要求不间断连续要样。为了克服常规的固定I/O端口读写方式容易造成丢失数据且数据传输速率低的缺陷,系统采用双端口RAM技术。利用计算机内存直接映象技术,对内存物理地址直接读写,克服了数据传输的瓶颈效应,满足了系统的实时性。在双端口RAM设计过程中,按照工业控制标准实行全地址译码,以确保全地址空间的每一个存储单元的地址在总线上。

双端口RAM采用英国ARCT公司的双端口RAM HK12S25(8K×8bit),采样数据与PC接口采用FIFO存储器(先入先出存储器)作为缓冲,系统具有FIFO全满(FULL)、半满(HALF)标志。HALF标志用于决定PC机什么时间开始读取转换结果,当PC监测到HALF信号有效,表明在FIFO中至少有4K个数据可以为PC读取。同时FIFO至少提供4000个空间作为读数时A/D数据存放的缓冲区。由于PC采用RAM映射方式从FIFO读数据,通常速度为1.2M~2M字/秒,PC机有充足的时间来进行实时数据处理等操作。

寄存器的定义(BaseAdr+20):

D7 D6 D5 D4 D3 D2 D1 D0

FULL HALF 中断标志

输入模拟通道转换控制采用LUT(RAM查找表)驱动模式,LUT的容量为256单元,即输入通道转换有256种模式。同时,LUT专门提供一条额外的控制线输出到外部,可以为用户提供可编程状态标志、同步采样保持器控制等功能。同时应特别注意LUT驱动通道转换的功能,它可以提供非线性通道控制模式--不同的通道具有不同的采样速度。

1.3 多线程的数据采集软件设计

在要求高速、高可靠性和连续采样的情况下,一方面要求系统不间断地进行数据采集,同时还要进行数据的在线定时处理,否则将会造成数据的丢失或不连续。在软件设计中,引入了Windows线程的多任务处理技术(multitasking)。一个线程是程序的一条执行路径。MFC(Microsoft Foundation Class)明确区分了两种线程:用户界面线程(UI)是一个消息泵,用于处理用户界面的任务;工作者线程(Worker Thread)完成用户自己定义的任务,可以充分利用工作者线程来完成数据的采集、传输以及处理,以保证数据的实时性、完整性和连续性。

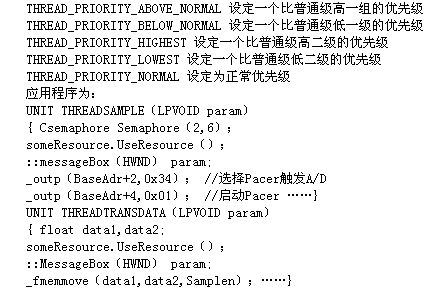

在使用多线程时,如何防止两个线程同时访问同一个数据集(SRAM中的4K个数据可以看作是一个数据集),以及当HALF FLAG标准已出现,一个线程正在往SRAM中写数据时,另一个线程要读取SRAM的数据,该如何处理,是保证数据完整性和连续性的关键。有四种使线程编程更安全的线程同步对象,保证多个线程能在一起适当地协调工作:Critical Section(临界区)、Mutexe(互斥)、Semaphore(信号量)以及Event(事件)。其中Critical Section是保证在某一个时刻只有一个线程能访问SRAM的简易方法,通过对邻界区对象的Locking(加锁)和Unlocking(解锁)来使得任何线程都可以调用访问SRAM中的数据集;Mutexe与Critical Section很相似,只是使用起来稍复杂一点;Semaphore与前两者也很相似,但Semaphore允许多个线程同时访问同一资源。这与前两者在同一时刻只允许一个线程访问一个资源的限制不同。在本系统中,主要有数据采集、标志位辨别、数据传输、信号处理等线程,使用Semaphore方法已足以满足要求。但是在设计线程时,要合理规划多个线程对同一资源的使用顺序,这可以通过设定每个线程的优先级别来实现。在本系统中数据采集具有的优先级,其次为数据传输。线程优先级常量设定如下:

1.4 高速数据锁存技术

在高速连续数据采集系统设计时,高速数据的锁存一直是个难点。A/D转换的速率越快,数据锁存的难度越大。为确保数据的完整性,采用将数据输出端口的数据分成四路输出,为了补偿数据的传输延时以及SRAM的建立时间,在进行四分频时要推迟1~2个时钟,数据进入SRAM后,便可以将数据分组打包传输给计算机进行处理。

1.5 板卡的抗干扰措施

在高速连续数据采集系统设计时,应避免各个信号之间的共模干扰以及信号的完整性。在本PCB设计时,采用了六层板设计技术,分别为布线和元件层、模拟地和±12V电源层、数字地以及ECL的VCC信号层、模拟+5V和数字+5V和+3.3V层、模拟-5V和数字-5V和+2.5V层、布线和元件层,并且使用了大面积的电源和地层可以使各信号线与地或电源平面之间形成与紧偶合以达到减少信号线之间的共模干扰。模拟信号与数字信号相互隔离,并单独供电。这些措施的采用,有效地抑制了信号间的共模干扰。

2 实际应用

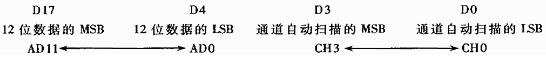

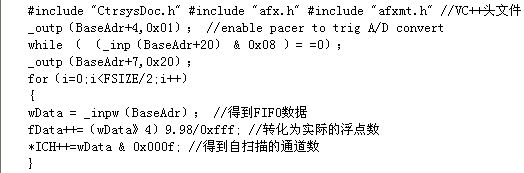

笔者设计的基于PCI总线协议的板卡已应用于某国防项目,由于篇幅的原因,省略硬件结构图,程序框图如图1所示。为了加快数据的读写速度,采用了16Bits寄存器,在读取A/D转换结果时可读入16Bits数据。16Bits数据格式如下:

部分关键源代码如下:

本文探讨了基于PCI总线的高速数据采集卡设计的一些方法,具有一定的参考价值,经实践证实用可靠。其中还有许多相关技术有待于研究和开发,特别是DSP技术的发展,会更加促进这一技术的完善和发展。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。