今天针对DSP优化的高性能FPGA已经在DSP领域扮演着重要的角色。DSP领域的设计工程师逐渐发现他们所处的环境变化十分迅速,标准快速演化并且不断融合,上市周期越来越短,设计工作受到经济和技术上的约束增多,但设计一旦成功获得的回报也很巨大。

由于在性能和灵活性方面的完美组合,FPGA在DSP领域的应用越来越普遍。诸如通信、多媒体和国防行业等高增长的市场都非常需要高性能的DSP技术。这些市场的特点在于始终处于连续的变化之中,不断变化的标准、市场需求、客户需求以及竞争态势。要跟上市场变化,企业就需要一种强大且灵活的处理器---FPGA就是这种特别适合的技术。

宽带革命

市场环境的变化将会改变未来几年内DSP实现的方式。显着地,宽带革命将带来的挑战。

宽带革命是由传统上分别属于不同领域的许多技术的融合所引发。其中包括计算、电信/无线、视频、图像和网络等。图1突出了由这一融合而新产生的一些新应用。

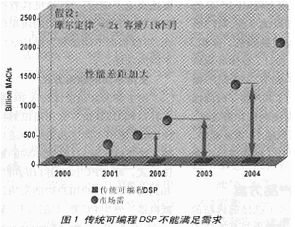

此类新兴应用需要处理的模拟和数字数据量呈指数型增长。这又进一步加大了对更快的DSP的需求。虽然摩尔定律仍适用于目前快的DSP,但在所需要的性能水平与实际DSP器件所提供性能水平间的差距仍在不断增大(参看图2)。因此很明显,DSP要满足宽带革命所提出的挑战必须寻求新的数据处理方法。

此外,今天快速变化的市场上,产品上市时间缩短。同时由于竞争产品跟上的速度更快,因此产品量产阶段更短。所以,上市时间变得更为关键,FPGA供应商很早就意识到了这一点。过去上市晚仅仅是利润少一些,今天则意味着根本没有利润,甚至某些情况下是生意彻底失败!

这意味着DSP需要足够灵活以满足不断缩短的上市时间要求。

采用FPGA实现高性能DSP

主流制造商,如TI、ADI和Motorola,生产的传统DSP有通用产品或特殊应用标准产品(ASSP)。通用DSP的优点是通过编程可以应用在广泛的产品中。而特殊应用产品则是针对特定的应用而开发的,如ADSL调制解调器(带DSP的ASSP),或针对特定客户而开发(带DSP的ASIC)。在性能要求较低的应用中,甚至也可利用微处理器作为DSP。

推动DSP应用对FPGA需求的重要因素之一就是传统处理器性能增长放缓。尽管在摩尔定律的推动下,处理器的制造工艺不断向更小节点发展,但仅仅简单地通过减小工艺节点来大幅提高DSP和GPP的性能变得越来越困难。

与此同时,由于通信系统将数据传输效率不断推向香农定理的上限,算法的复杂性以更快的速度提高。Turbo编码和MIMO系统等先进技术已经非常接受香农定律的理论极限,成本就是极高的计算复杂性。 这就导致了算法性能要求和处理器性能之间的差距越来越大。因此,设计人员必须寻找新的设计解决方案(如DSP),在固定结构处理器之外选择FPGA。

FPGA 的DSP性能的关键是其内在的并行机制,即利用并行架构实现DSP功能的功能。这一并行机制使得FPGA特别适用于完成像滤波这样的重复性DSP任务。因此,对于高度并行执行DSP任务来说,FPGA性能远超通用DSP处理器的串行执行架构。

例如,传统DSP处理器每个时钟周期多可完成8个MAC操作。要执行一个256抽头的滤波器,传统DSP处理器需要在1 GHz时钟下执行 32个时钟周期,才能达到31.25 MSPS的采样处理性能。与此相对比,有512个并行XtremeDSP逻辑片的赛灵思Virtex-4 SX55在500 MHz时钟下可达到500 MSPS的性能。因此在时钟慢一倍的情况下,FPGA提供的性能高了一个量级还多。

FIR滤波器对输入信号进行滤波,其方法是将每一输入信号数据样本与几个恒定数值(系统)相乘,然后对结果进行累加。加到输入信号上的MAC操作越多,滤波器越。例如,256阶FIR滤波器中对每个数据样本需要进行256次MAC操作,然后才能处理下一个样本。

FPGA提供的DSP性能已超过1280亿MAC每秒,大大高于目前主流供应商所能提供的传统DSP的性能。Virtex-II可以提供6千亿MAC每秒的性能。为达到这样的性能,FPGA采用了多路并行结构处理输入信号。

采用这种并行结构,256阶FIR滤波器中的每个样本可以在一个时钟周期内处理完,因此极大地改善了DSP的性能和效率。

PLD中嵌入DSP

很多PLD厂商开始采取行动。Xilinx作为世界可编程逻辑器件的领导厂商,拥有先进的FPGA技术以及先进的开发工具。2000年11月,推出DSP行动,试图进入这一市场。

Xilinx XtremeDSP行动的目标是希望满足宽带革命的高性能挑战。其它特性还包括根据如芯片面积和系统频率来优化DSP设计。XtremeDSP行动还推出了一些开发工具可弥补传统上在DSP和FPGA设计方法间存在的差距。

Virtex-II提供的性能包括:

·千万门FPGA结构允许实现大量的并行处理。

·多达192(18×18)个嵌入式乘法器,工作频率依字大小不同可达250MHz,可在的芯片面积上实现快速无延迟乘法操作。

·多3.5M位完全双口块RAM,可优化数据缓冲和存储。

新的Virtex-II系列的增强结构使其在实现需要计算的算法时具有独特的优势。Xilinx提供的测试数据表明,Xilinx FPGA比业界快的DSP运行要快100倍。因此,单个FPGA即可代替传统上所谓的DSP处理器阵列。

传统上基于SRAM的FPGA具有现场容易改变和升级的灵活性,除此以外,XtremeDSP还增加了如下性能。

两个这样的新性能即是分布式资源和分段布线(segmented routing)。

·分布式DSP资源——这使设计者可以根据算法和性能要求改变DSP结构,从而达到面积/成本或性能/系统频率的设计。

·分段布线(采用动态互连)——可保证与器件大小和集成到FPGA中的其它系统功能无关,始终达到的性能。

Xilinx XtremeDSP计划中令人心动的方面可能就是能够提高生产率。XtremeDSP计划缩短了FPGA DSP设计周期。将主要通过配合Simulink使用的MathWorks系统生成器和滤波器生成器来实现。

·Simulink系统生成器——传统上FPGA和DSP的设计流程非常不同。利用与MathWorks的伙伴关系,Xilinx开发的系统生成器填补了FPGA和传统DSP设计流程间的差距。

·滤波器生成器——如前面所述,数字滤波器是DSP经常的用途。一系列DSP供应商提供了滤波器生成器以加快漫长的滤波器设计过程。然而,目前市面的FPGA滤波器生成器要么只能生成完全串行(即生成芯片面积但性能的实施方案)的滤波器或完全并行(生成性能但芯片面积效率的实施方案)的滤波器。然后,多数的DSP设计并不是需要完全串行或完全并行的实施方案,而是介于其中的混合方案。Xilinx滤波器生成器是约束条件驱动的,可以根据给定的性能级别或并行程度生成占用资源的实施方案。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。