语音压缩技术指的是对原始数字音频信号流运用适当的数字信号处理技术,在不损失有用信息量,或所引入损失可忽略的条件下,压缩信号编码速率,也称为压缩编码。以生成适合传输的数字信号流,提高传输效率。这样做的优点在于可以适应在低码率的信道上实现可靠传输,也可以在同样的信道上传输更多的数据。对语音编码技术中语音质量的评价主要分为两类,客观评定方法和主观评定方法。其中客观评定方法用客观测量的手段来评价语音编码的质量,其特点是计算简单,但不能完全反映人对语音质量的感觉。主观评定方法符合人类听话时对语音质量的感觉,因而得到广泛应用。

本文介绍了DSPG公司生产的语音压缩专用芯片CT8022的引脚功能和主机与存储器的接口,给出了CT8022的工作原理、工作模式、工作流程和使用方法,给出了CT8022与主机组成的语音压缩应用电路的连接方法。

CT8022是DSPG公司开发的可实现多种压缩算法的专用DSP芯片。它可接受外部串行A/D提供的64/128kbits/s的8bit A/μ数据或16bit线性数据,并实现全/半双工压缩和解压,以将其压缩为由主机通过命令字决定的格式。另外,CT8022还提供了DTMF信号和呼叫继续音的产生和检测功能。可应用于H.323和H.324多媒体可视电话/视频会议等系统,也可用于实现数字数据/语音同传(DSVD)技术。

1 引脚说明

CT8022有128条管脚,分为6类。

(1)主机接口引脚

HSTDB0~7:主机数据总线。

HSTAB0~3:主机地址线。其中HSTAB0用来选择16位控制字的高8位或低8位,当为0时选择低8位,为1时选择高8位。

HSTRDN:主机读允许信号。允许主机从由HSTAB1~3译码后所选择的主机接口寄存器中读出数据。

HSTWRN:主机写允许信号。允许主机向由HSTAB1~3译码后所选择的主机接口寄存器中写入数据。

HSTCSN:主机接口选中信号。在对CT8022读写时,该引脚与HSTRDN,HSTWRN和HSTAB0~3共同作用。当HSTCSN有效时,HSTAB0~3应保持不变。在DMA方式时,此信号应置为无效。

(2)数据/程序存储器引脚

MDB0~15:外部数据存储器数据总线。

ADDR0~15:外部数据存储器地址总线。

BSEL:外部数据总线字节选择。当外接非16位宽度的内存时该引脚有用。

DRDN:外部数据存储器读允许。

DWRN:外部数据存储器写允许。

PRDN:外部程序内存读允许。

PRWN:外部程序内存写允许。

CREADN:同时读取外部程序和数据存储器引脚。

DCSN:外部数据存储器片选信号。不用时接地。

(3)时钟引脚

SLK:CODEC接口移位时钟。

FSYNC:CODEC接口帧同步时钟。

XIN:晶体/外部时钟输入。

XOUT:晶体输出端。

CLKOUT:CT8022语音压缩芯片的频率。由内部频率45.056MHz分频得到。分频因子可通过命令设置。

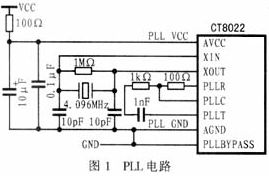

PLLR,PLLC,PLLT,AVCC,AGND:PLL支持管脚。连接方法如图1所示。

PLLBYPASS:禁用内部PLL。用于XIN端直接外接90.112MHz时钟时用。

(4)CODEC引脚

DX0:用于串行输出已解压信号至CODEC0。

DR0:用于从CODEC0串行输入8/16bit格式信号。

DX1:用于串行输出已解压信号至CODEC1。

DR1:用于从CODEC1串行输入8/16bit格式信号。

(5)DMA引脚

TXDREQ:DMA发送请求信号。数据的传输可采用DMA方式或主机访问方式。具体方式可在初始化时通过向硬件控制寄存器(HCR)写控制命令来控制。

TXDACKN:DMA发送允许。

RXDREQ:DMA接收请求信号。 RXDACKN:DMA接收允许信号。

注:在以上各管脚名称中,如果一个字母为N,则表示该管脚为低有效。

2 工作原理

2.1 与CODEC的接口

CT8022可以直接与一个或两个8 bit A/μ率编译码器(A/D和D/A)相连,也可以与16位线性编译码器相连。在作为输入/输出信号时,可通过主机接口命令来确定接口的具体参数。当CT8022向CODEC提供时钟信号时,时钟SCLK和FSYNC由其内部的时钟通过编程而分频得到。CODEC的抽样频率为FSYNC。SCLK、FSYNC和CT8022内部的时钟关系为:

SCLK=CT8022的内部时钟/(N+1),其中3≤N≤31;

FSYNC=SCLK/(M+1),其中18≤M≤1023。

式中M、N均为分频因子,具体值可根据采样频率在初始化时用命令写入。

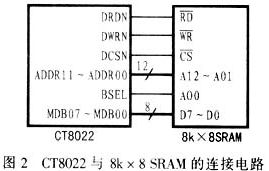

2.2 外部SRAM

CT8022至少需要8k×8的SRAM,以用来存储运算时所需的数据。基本操作和程序代码存储在片内的ROM中。CT8022与外部SRAM连接如图2所示。

其中BSEL用来选择高/低位字节,当SRAM地址线为16位时,此管脚不用。

2.3 主机控制接口

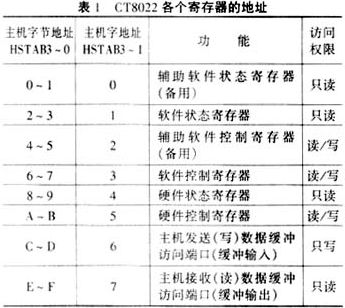

对CT8022语音压缩芯片的控制是通过片内的8/16位控制/状态/数据接口来进行的。这些控制寄存器包括硬件控制寄存器(HCS)、硬件状态寄存器(HSR)、软件控制寄存器(SCR)、软件状态寄存器(SSR)、辅助软件控制寄存器(ASCR)和辅助软件状态寄存器(ASSR)等,而器件中的缓冲器则通过主机读/写数据缓冲访问端口来进行语言数据的操作。

CT8022包含两个16字的数据缓冲区,通过它主机可以向CT8022发送数据,同时主机也可接收CT8022的数据。由于主机数据总线为8位,因此应根据HSTAB0选择来访问高/低字节,并由CT8022 内部的地址计数器产生访问所需的地址。各个寄存器的地址如表1所列。

表中的HSTAB0用来选择16位控制字的高8位或低8位。当HSTAB0为0时选择低8位,为1时选择高8位;访问时先低8位,后高8位。

3 工作模式

CT8022主要的工作模式有:空模式、重放(解压缩)模式和记录(压缩)模式。

在重放模式中,CT8022中的发送寄存器被激活,主机应向CT8022发送已被压缩的数据,以对其进行解压。当数据中断时,CT8022将重复解压发送寄存器内的数据,并将其发送到CODEC,直到主机重新发送有效数据。

当系统处于全双工模式时,可同时进行语音的压缩与解压。

CT8022的编译码器循环模式为测试模式,可用于将CODEC送来的码流不经压缩而直接送回CODEC。

4 工作流程

4.1 初始化

在使用CT8022时,必须先对其进行初始化操作,过程如下:

(1)在系统加电或复位后,直到CONTROLREADY位有效。

(2)主机首先向SCR写入设置CT8022为空模式的命令0000H。

(3)CT8022产生应答,并置HSR的STATUSREADY位。

(4)主机检测到STATUSREADY位有效时,从SSR读取状态信息。

(5)主机向SCR写入CODEC的配置命令。

(6)CT8022根据配置命令配置与CODEC的接口,并产生应答信息,同时置STATUSREADY位。

(7)主机检测到STATUSREADY位有效时,从SSR读取状态信息。

4.2 写控制字

在初始化完成后,主机便可写入控制字,以规定CT8022的具体工作状态。

下面以与ITU-G.723.1兼容的6.3kbits/s压缩算法为例来说明设置CT8022为压缩状态的具体过程。假设CT8022已经初始化完成并处于空模式,而且CODEC接口符合G.723.1的要求。

(1)主机检测HSR的CONTROLREADY位;

(2)通过向SCR写入命令字5131H来设置速率为6.3kbit/s;

(3)CT8022通过SSR发出应答信号;

(4)主机检测HSR的STATUSREADY位,检测到该位后读取SSR,并将STATUSREADY自动清零;

(5)向SCR写入控制字5102H,使数据可以在主机读/写数据缓冲端口与CT8022内部寄存器自动交换;

(6)CT8022通过SSR响应命令;

(7)主机检测HSR的STATUSREADY位,检测到后读取SSR,并将STATUSREADY自动清零;

(8)主机向SCR写入控制字1C03H,表明主机将通过主机接收数据缓冲访问端口读取数据;

(9)CT8022完成内部同步,并产生应答;

(10)主机检测HSR的STATUSREADY位,读取SSR,并将STATUSREADY自动清零;

(11)至此,CT8022已处于记录模式。可对由 CODEC发送来的数据以30ms的长度为一帧进行压缩。

4.3 停止操作

若要停止记录,可进行如下操作:

(1)向SCR写入空模式命令字0000H,或执行停止记录命令5120H;

(2)CT8022停止对数据的压缩,并清除RXReady位;

(3)CT8022向SSR写入命令应答信息;

(4)主机检测HSR的STATUSREADY位,检测到后读取SSR,并且将STATUSREADY自动清零。

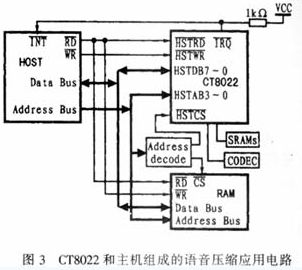

5 应用电路

由CT8022和主机组成的语音压缩应用电路框图如图3所示。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。