引言

随着通信与广播电视业务的发展,无线电频谱迅速、大量的被占用,频道拥挤和相互间干扰日趋严重,为了能有效地利用无线电频谱,减少相互间的干扰,信号监测业务随之成为必要。调幅广播信号监测系统是用于实时监测短波调幅广播信号的调幅度、载波频率的专用系统。

数字信号处理(Digital Signal Processing,简称DSP)是一门涉及许多学科而又广泛应用于许多领域的新兴学科。20世纪60年代以来,随着计算机和信息技术的飞速发展,数字信号处理技术应运而生并得到迅速的发展。数字信号处理是一种通过使用数学技巧执行转换或提取信息,来处理现实信号的方法,这些信号由数字序列表示。在过去的二十多年时间里,数字信号处理已经在通信等领域得到极为广泛的应用。德州仪器、Freescale等半导体厂商在这一领域拥有很强的实力。

DSP(digital signal processor)是一种独特的微处理器,是以数字信号来处理大量信息的器件。其工作原理是接收模拟信号,转换为0或1的数字信号。再对数字信号进行修改、删除、强化,并在其他系统芯片中把数字数据解译回模拟数据或实际环境格式。它不仅具有可编程性,而且其实时运行速度可达每秒数以千万条复杂指令程序,远远超过通用微处理器,是数字化电子世界中日益重要的电脑芯片。它的强大数据处理能力和高运行速度,是值得称道的两大特色。

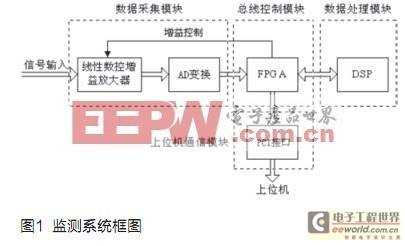

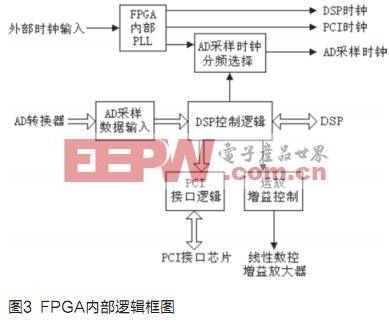

图1为调幅广播信号质量监测系统的系统框图。本系统由数据采集模块、总线控制模块、数据处理模块、上位机通信模块组成。其工作方式为:输入信号通过线性数控增益放大器后由A/D转换器采样,采样后的数据由FPGA送入DSP进行数据处理,所得到的监测结果由FPGA通过PCI接口送入上位机。同时由DSP对采样所得信号大小进行监测,通过FPGA对线性数控增益放大器的增益进行调整,使其输出信号满足系统测量要求。

算法和数字处理软件

调幅广播信号的特点是载波频率相对稳定而调幅度实时变化,所以系统每监测一百次调幅度再监测载波频率同样可以达到监测信号的目的。系统所要监测的信号的带宽小于10kHz,频率范围为1.5MHz~30MHz。若对信号进行过采样,为保证测量则采样频率要达到240MHz,后续数据处理难度较大,所以系统选择对信号进行欠采样。采样点数为N=4096。

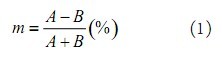

调幅信号调幅度的计算公式如下:

其中m为调幅度,A为包络上、下两正峰间的幅度,B为包络上、下两负峰间的幅度。

本系统中先用频域移相法求得A/D采样后信号的Hilbert变换,然后取即可得到AM信号的上包络。因为单音调幅信号的上、下包络关于零轴对称,所以只要得到上、下包络其中之一就能根据式(1)求得调幅度。

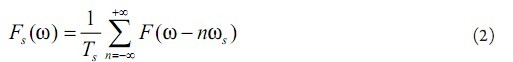

设输入信号为f(t),则由采样定理可知采样前信号的频谱F(w)和采样后信号的频谱FS(w)有如下关系:

设输入正弦信号为:

![]()

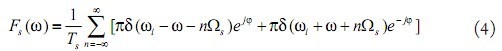

则采样后信号的频谱为:

根据上式可知,信号的频谱在w=wi-nW处有峰值。由下式可知只要计算出n值和通过傅里叶变换估计欠采样后信号的频率w,正弦信号的真实频率wS就可准确求出。

![]()

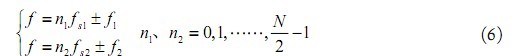

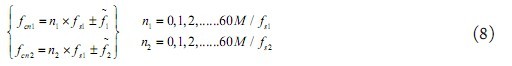

输入信号频率为30MHz,系统选取公倍数为60MHz的两个采样频率分别为fs1、fs2(fs1=60/264MHz=0.228MHz、fs2=60/261MHz=0.230MHz)对信号进行采样,对采样后的信号作FFT变换,与fs1和fs2相对应的频率分别为f1=fs1×n1/N和f2=fs2×n2/N。由此可粗略的得到信号的载波频率为:

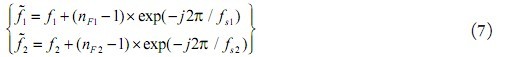

进而为了达到1Hz的测量,必须进行频谱细化。若要达到0.5Hz分辨率,则分析200Hz谱宽需要计算400点。在粗估计频率的前后100Hz内进行频率细化分析,分别对f1和f2作n1和n2周围400点的DFT变换。变换后得到频谱F1和F2,分别求出其幅度值对应的位置nF1和nF2,从而得到精估计的信号频率值![]() 和

和![]() :

:

根据式(6)可以列出两组载波频率的矩阵:

根据式(8)中接近的两个值fcn1和fcn2就可以计算出载波频率值为:

根据上述算法可得到DSP中数据处理软件的流程图(图2)。

FPGA逻辑设计

FPGA(Field-Programmable Gate Array),即现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

目前以硬件描述语言(Verilog 或 VHDL)所完成的电路设计,可以经过简单的综合与布局,快速的烧录至 FPGA 上进行测试,是现代 IC 设计验证的技术主流。这些可编辑元件可以被用来实现一些基本的逻辑门电路(比如AND、OR、XOR、NOT)或者更复杂一些的组合功能比如解码器或数学方程式。在大多数的FPGA里面,这些可编辑的元件里也包含记忆元件例如触发器(Flip-flop)或者其他更加完整的记忆块。

本系统中FPGA主要用来协调各个模块间的数据传输,分别为A/D采样数据到DSP的传输、DSP计算结果到PCI接口的传输以及数控增益放大器的增益控制。同时FPGA还为系统工作提供了必要的时钟、复位信号、控制信号(图3)。

器件选择

A/D转换器是整个监测系统的关键部件,它的性能往往直接影响整个监测系统的技术指标。当A/D有效位数大于12位时量化损失为0.0055dB,其对测量的影响可忽略不计。否则会造成失真,甚至烧毁芯片,所以要在AD9433之前用运放对信号幅度进行调控。同时根据调幅广播信号幅度实时变化的特点,要求所选择的运放增益可变。基于上述要求系统选用ADI公司的线性数控增益放大器AD8320。

系统对信号采样点数为N=4096,算法采用Hilbert变换解调求调幅度和欠采样求载波频率,所以每计算100次调幅度和1次载波频率所需要的运算量大概为:

![]()

本系统选用ADI公司SHARC系列的ADSP-21262作为数据处理芯片。

根据ADSP-21262性能可估算出系统完成调幅度测量所需要的时间大概为800μs,完成载波频率测量所需要的时间大概为10ms,可以满足系统实时性要求。

在总线控制模块中,系统选用Altera公司Cyclone II系列中的EP2C8Q208C8 FPGA芯片。

PCI接口模块选用PLX公司的PCI总线控制芯片PC19054。

结语

本文介绍了一种基于DSP的调幅广播信号监测系统,采用了数字信号处理的方法,与模拟监测技术相比处理更加灵活、测量更高、并且大大提高了系统的可靠性。本系统已成功应用于实践,经过实践检查,载波频率测量达到1Hz,调幅度测量达到3%,测量效果满足实际需要。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。