1 USB控制芯片

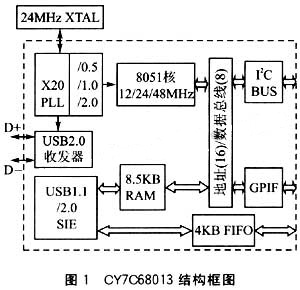

Cypress Semiconductor公司的EZ-USB FX2是世界上款集成USB2.0的微处理器,它集成了USB2.0收发器、SIE(串行接口引擎)、增强的8051微控制器和可编程的外围接口。FX2这种独创性结构可使数据传输率达到56Mbytes/s,即USB2.0允许的带宽。在FX2中,智能SIE可以硬件处理许多USB1.1和USB2.0协议,从而减少了开发时间和确保了USB的兼容性。GPIF(General Programmable Interface)和主/从端点FIFO(8位或16位数据总线)为ATA、UTOPIA、EPP、PCMCIA和DSP等提供了简单和无缝连接接口。CY7C68013有三种封装形式:56SSOP,100TQFP和128TQFP。

CY7C68013的结构框图如图1所示。

|

|---|

FX2的端点缓冲区分为大小两组:EP0、EP1(IN)、EP1(OUT)是小端点,大小为64字节,只能由CPU来存取,不能由外部逻辑连接;EP2和EP4默认为OUT端点,EP6和EP8默认为IN端点。FX2为其大端点提供多种缓冲方式,在OUT缓冲区中写入供外部处理器读取的数据。它具备全速与高速两种传输速率,而且具有USB协议所规定的4种传输模式,即控制传输、中断传输、块传输及等时传输。

2 系统硬件构架

2.1 USB与DSP的硬件连接

TMS320C6713是TI公司在TMS320C6711的基础上推出的C6000系列新一代浮点DSP芯片,它是目前为止C6000系列DSP芯片中性能的一种。TMS320C6713可在255MHZ的时钟频率下实现1800MIPS/1350MFLOPS的定点和浮点运算,因而可极大地满足通信、雷达、数字电视等高科技领域对信号处理实时性的要求。外设资源包括直接存储器访问控制器(DMA),外。部存储器接口(EMIF)、串行口、扩展总线或主机口、定时器等。CY7C68013能非常灵活地实现与DSP或MCU的接口。可采用同步或异步方式与主设备(如ASIC,DSP等)连接。

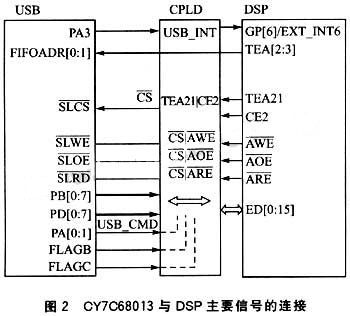

在本方案中,使其作为从设备,选用了Slave FIFOs,异步读/写,在这种模式下,DSP可以像读/写普通FIFO一样对CY7C68013内部的多层缓冲FIFO进行读/写。主要信号连接如图2所示。主机(PC)发出命令的同时也由PA3提供中断触发信号给DSP的外部中断引脚6(EXT_INT6)。其上升沿被检测到以后,DSP就进入相应中断服务程序,开始处理USB的传输,“或”组合逻辑满足严格的时序要求,FLAGB和FLAGC是CY7C68013内部FIFO的空、满状态标志,PA[0:1]表示PC发送的命令类型。这些信息在CPLD内部整合到数据总线ED[0:15],DSP开始传输数据包前对其提取判断,TMS320C6713对CY7C68013内部端点(EP)的选择,是通过地址线TEA[2:3]来实现。

|

|---|

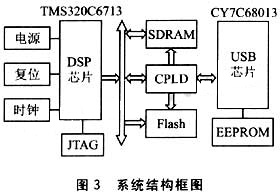

2.2 系统总体结构设计

根据上述硬件通信模式搭建基于PC、USB、DSP的主从式系统,当系统上电完成各模块固件配置和硬件初始化后,可由PC发出控制命令,以外部信号触发DSP进入相应的中断处理程序,自动完成数据流USB、DSB处理和USB回传的多次循环过程;PC显示处理后的结果。系统总体结构框图如图3所示。

|

|---|

DSP芯片通过片中的EMIF为SDRAM,Flash等器件提供接口。SDRAM为同步存储器件,EMIF有专门的控制线和时钟与它进行无缝连接。这里SDRAM用做数据存储器。

复位电路提供系统上电和工作电压异常时的自动复位及人工控制复位。时钟电路为DSP处理模块提供时钟信号。

USB的接口电路提供PC与DSP的高速数据传输通道,接口芯片通过CPLD与外部处理器DSP相连,置于EMIF的CE2空间(通信模式如前所述)。

3 通信模块软件设计

3.1 CY7C68013的固件程序规划

固件程序框架通过几个不同的功能模块,实现了一个简单的互操作任务执行器,首先,通过调用用户的初始化函数TD_Init(),初始化所有内部状态变量,之后,程序框架将USB口初始化为未配置状态,并且使能中断,以1s为时间间隔开始重新列举(renumerate)设备,直到端点0收到设置包为止,一旦检测端点0受多一个设置包,固件框架程序就启动执行一个互操作的任务分配器,按照给定的顺序重复执行下面的任务:调用函数TD_Poll(),判断是否有标准设备请求等待处理,确定USB核是否了USB挂起事件。

主要固件配置如下:

1)配置异步从FIFO(Asynchronous Slave FIFO)模式,接口驱动采用内部的48M赫兹的时钟源。

2)EndPoint4和EndPoint8作为双向传输的管道,分别对应缓冲FIFO4和FIFO8存放USB需要接收与下传的数据,它们均采用批量(BULK)传输方式。

3)设置FIFO4、FIFO8为自动方式,即在数据传输过程中无需CY7C68013的8051内核参与,以保证持续、高速、有效的数据传输。

EZ-USB FX2芯片定义了几个特殊寄存器,以辅助固件程序相应设备请求,并向主机传送数据,当设备收到设置包时,USB核会自动将设置数据放入8字节的SETUPBUF缓冲区中,用户只须从中读取设置数据,进行分析来判断请求的类型即可。

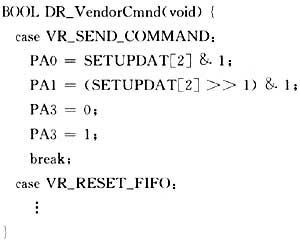

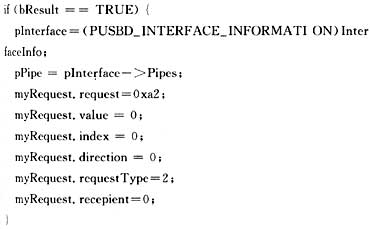

方案中部分设备请求代码如下:

|

|---|

读取缓冲区中第2字节由PA[0:1]发送至DSP,作为命令类型标志(00为下传,01为上传,10为处理);同时PA3口提供外部中断触发信号的上升沿。

固件就绪后通过Cypress公司提供的工具Control Panel加载至EEPROM中,当需要修改固件时,就可以在不改动硬件的情况下将主机上修改好的固件重新。

3.2 上位机流程

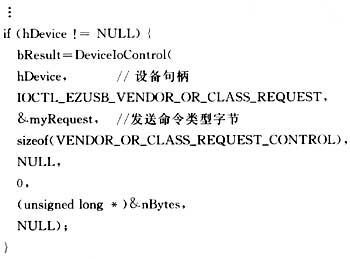

主机应用程序与操作系统相互作用,利用PC丰富的资源,实现显示验证,提高系统的可操作性,当操作系统认为有新设备接入时,就会自动调用相应的设备驱动。另外,该软件需要一个图形用户界面来控制所用的函数,这里采用VC++6.0来编制应用程序,首先调用CreateFile()打开USB接口设备,获得设备的句柄hDevice,然后计算机通过调用DeviceIoControl()函数向外设发出。部分程序如下:

|

|---|

myRequest的8个成员变量对应固件配置SETUPBUF缓冲区中8字节的(SETUPDAT)数据,其中value的值表示了主机向DSP发送的命令类型(00/01/10),使DSP配合完成接收,处理及上传的系统过程。

|

|---|

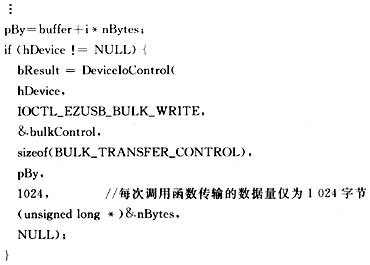

每次调用DeviceIoControl函数传输的数据量仅为1KB。为了满足大数据量或者整帧图像数据传输的要求,需要循环调用DeviceIoControl()函数,以数据流的过程为例,循环体中的代码如下:

|

|---|

buffer是主机发出数据块的头指针;pBy为每次下传数据块的首地址,是随着循环变量i递增的值。同样,上传数据的过程中也有类似的存储操作。

4 系统测试

利用图像序列对此主从式联机系统进行测试。

触发PC机上的界面控件(PA(0:1)=00),10幅经不同程序噪声污染的同一内容的图像,DSP检测到通用外部中断口EXT_INT6的信号(对应USB芯片的PA3)读入数据读取命令类型,将10帧图像数据存入SDRAM空间,之后,上位机继续发出处理命令,DSP检测到PA[0:1]=10对存储的多帧图像数据进行累加平均,从而提高图像的信噪比,在收到上传命令(PA[0:1]=01)时,DSP将处理完成的图像回送至PC机显示。

5 结语

本文详细介绍了通过TMS32C6713的EMIF扩展USB接口的硬件连接、USB2.0固件程序和应用程序的开发以及基于这种通信模式的小型联机系统的构成。经实际验证,系统运行可靠,是一种比较好的高速数据传输与处理的解决方案。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。