引言

许多现代数据采集系统均是由高速和高ADC组成的。由于其低成本和低功耗,基于CMOS开关型电容器的ADC通常被用于此类设计中。ADC使用一个无缓冲前端,直接耦合至采样网络。为了有效地化噪声和信号失真,需使用一款高速、低噪声和低失真的运算放大器来驱动该ADC。为了使失真化,将运算放大器输出在ADC采集时间内调节到理想的是非常重要的。通常,运算放大器建立时间是根据产品说明书中规定的频率响应时间计算得出的,也可以通过具有限制功能的示波器对输出进行测量得出,有时需要将运算放大器的输入与输出差值放大来实现更高的。但这些方法均受示波器以及电路寄生的限制。此外,运算放大器的建立时间还受由示波器探针导入的寄生电容和电感的影响。第二种方法是将运算放大器的输入输出差值放大来提高测量的。以上这些方法均未考虑 ADC 采样电路和采样数据包中的寄生电容和电感。

建立时间的定义

建立时间是指从理想的瞬时步进应用输入到闭环放大器的输出达到并保持在一个规定的对称性误差范围的时间。建立时间包括一个非常短暂的传播延迟时间,以及将输出转换至终值近似值所需的时间,然后结合转换从过载条件下恢复,稳定在规定误差范围内。对于高ADC来说,规定的误差范围通常为一个位(LSB)ADC的四分之一。

基本设置

此处使用的 ADC 是 TI 推出的 ADS8411,该器件是一款 16 位 2-MSPS 的逐次逼近寄存器 (SAR) ADC。驱动器运算放大器为 TI THS4031。图 1 显示了*估设置。

图 1 建立时间*估设置

利用一个模拟多路器 (MUX)(型号为 TI TS5A3159),通过开关其 2 个通道来产生瞬时步进输入。直流电压 V 连接到通道 2,通道 1 连接至接地;该设置可以产生一个步进输入,从零电压升至有电压,或从有电压降至零电压。此外,可以通过步进发生器来产生步进输入。步进发生器的建立时间速度要比运算放大器的建立时间快许多。

说明

步骤 1

ADC 首先对通道 1(连接至接地)进行采样。需要有一个较长的采样时间以确保 ADC 的输入电容被完全放电。

步骤 2

如图 2 所示,在瞬时 A 时,将模拟 MUX 从通道 1 切换到通道 2。该图显示了将 MUX 从通道 1 切换到通道 2 时 S 点(图 1)的电压。MUX 的建立时间用 ts 标识出来。假设 ts 比运算放大器的建立时间要短。

图 2 MUX 通道变化的建立时间

步骤3

一旦在瞬时 A 点开启模拟 MUX,运算放大器的输入就会立即开始发生变化。在瞬时 A 点之后,经过一个非常短暂的传播延迟,运算放大器的输出开始变化。通过转换率和产品说明书中规定的带宽可以大概计算出运算放大器建立时间 (tideal)。本文提出的方法描绘了运算放大器在瞬时 A 点到瞬时 B 点时的输出(如图 3)。瞬时 B 点和瞬时 A 点之间的差为 2tideal。

图 3 对 A 点到 B 点的 N 个采样求平均值,提高度

步骤 4

个 ADC 采样点是在瞬时 B 点,并记录下该点 n 个读数值(ADC 的数字输出)。求出这些数值的平均值,使其更为(稍后进行讨论)。借助图形发生器和可调时延发生器(见图 1),向左移 1 个毫微秒单位,得出下一个采样点(见图 3),再记录下该点的 n 个数值。按照此法,采样点每次以 1 个毫微秒单位从瞬时 B 点逐步移向瞬时 A 点,并以阵列的方式存储每个采样点平均值。该阵列是按照逆时间顺序绘制出来的,从而得出运算放大器输出建立时间的实图(如图 3 所示)。

求平均值,以获得更高

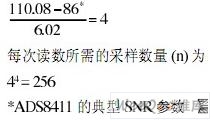

N 位 ADC 的输入应该少设定为 n+2 位,但测量出的输出在 ADC 上显示为 n 位数字代码。通过重复采样同一个输入和采用多个 (n) ADC 读数值,可以提高。求出 n 个输出数字代码的平均值。这表明每增加一位,读数值数量则为 4 个,因此增加了 w 位,则需要 4w 个读数值。

每增加一位,信噪比 (SNR) 就会增加 6. 02 dB。因此,16 位 ADC 就应该至少设定为 18 位。

SNR=6.02×N+1.76

其中,N 为 ADC 。对于 18 位 ADC 而言, SNR 的值为 110.08 dB,因此所需的更多位数 (w) 为:

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。