|

摘 要: 滤波和抗干扰是任何智能仪器系统都必须考虑的问题。在传统的应用系统中,滤波部分往往要占用较多的软件资源和硬件资源。复杂可编程逻辑器件(CPLD)的出现,为解决这一问题开辟了新的途径,采用CPLD实现滤波是一种高效可靠的方法。介绍了利用MAX+PLUSII对CPLD编程来实现对传感器和按键信号滤波和抗干扰。该方法已在产品开发中获得了成功应用。

| |

|

1 滤波和抗干扰概述

| |

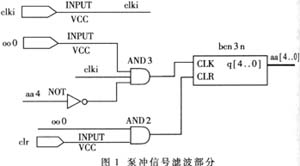

| 2 利用CPLD实现数字滤波及抗干扰 这里介绍的采用CPLD实现信号滤波及抗干扰的方法已经在智能仪器泵冲测量仪的开发中得到验证。下面就如何采用CPLD对系统的四路外部传感器脉冲信号和四路按键信号实现滤波、锁存、中断申请等功能进行阐述。 2.1 传感器信号滤波 由于要对传感器信号进行数字滤波,CPLD要引入时钟信号。因而我们对CPLD定义一输入端clki,作为数字滤波器的计数脉冲输入端。clki由单片机定时器1定时产生500Hz脉冲。以一路为例,泵冲信号滤波部分如图1所示。 | |

| |

| oo0为经电平转换后接近开关输出的信号。当oo0为低电平时,说明泵1未动作,封锁三端与门,时钟信号clki无法通过,计数器bcn3n不计数。同理,当aa4为高电平时,亦封锁三端与门(至于aa4如何变化及作用下文有介绍)。故当oo0为高、aa4为低时,clki接通计数器CLK端。当oo0和clr端任意一个为低时,计数器清零。计数器bcn3n由MAX+PLUSII的文本编辑器编辑,其文本如下: SUBDESIGN bcn3n ( clk INPUT q 4..0 OUTPUT VARIABLE Count 4..0 BEGIN count.clk=clk count=count +1 q=count END 其输出aa4..0等于计数器当前的计数值。Aa4就是aa4..0的位当计数值达到10H(十六进制)时,即aa4为高电平时,三端与门封锁,计数器保持10H不变,除非有清零信号。其波形如图2所示。 | |

| |

| 由波形可知,oo0为高,计数器开始计数。对于小的脉冲,计数器的位即aa4为低,认为是干扰信号;只有当aa4为"1"时才认为oo0的脉冲信号有效,并通过aa4将时钟脉冲阻断,使计数器值不再增加。这样做是为了防止由于oo0的脉冲不定宽,使aa4的电平不定,后面无法进行处理。还应注意的是,把oo0引入了清零信号。当信号有较多毛刺时,若oo0为低时不清零则使计数器不断累加,积累到一定程度,使aa4为1,系统将认为有一有效脉冲信号,产生误动作。 2.2 中断申请信号产生 中断申请信号由图3电路生成。 | |

| |

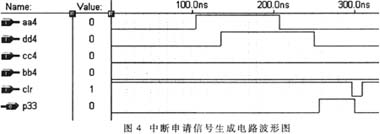

| 图中四个计数器的位接四端或门,只要有一路信号为高,或门输出就为高,并经过非门,输出低电平,接于D触发器的时钟端。D触发器的D端始终为高电平。D触发器为上升沿触发器,若输入D为1,在时钟脉冲的上升沿,把"1"送入触发器,使Q="1"。只有在CLRN端的clr信号有效时,D触发器清零,Q="0"。其波形如图4所示。 | |

| |

| 只要有一路信号为高,D触发器时钟端为低。当所有4路都为低时,时钟端由低变高,在上升沿,Q变为"1",发出中断请求信号。 如果多路脉冲信号有重叠,例如有两路信号发生重叠,而中断信号只有在四路都为低时才会产生,因此需要对信号进行锁存。本设计采用D触发器来实现锁存,电路如图5所示。 | |

| 当aa4为由低变高时,a4变为高电平。由clr信号清零。 2.3 按键消抖及数据输出 按键的消抖也通过计数器来实现,电路原理图如图6所示。 | |

|

|

| 按键未按下时为高电平,封锁时钟信号。按键按下时,计数器开始计数。当计数器输出位为"1"时,亦封锁时钟信号,防止按键时间不定使需要的k14信号不定。当按键信号为高电平时,对计数器清零,防止计数器累加干扰信号而造成误动作。波形如图7所示。 | |

| |

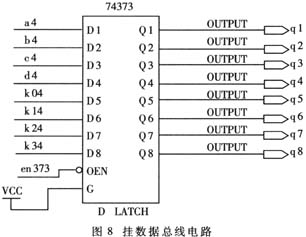

| 泵冲和按键经处理后的信号a4、b4、c4、d4、k04、k14、k24、k34,经74373挂于数据总线,如图8所示。74373使能信号由图9电路产生。 | |

| |

| |

| 它采用文本编辑,具体如下: SUBDESIGN bcn5nl A15a11 a10 a9 a8 wr rd INPUT

| |

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。