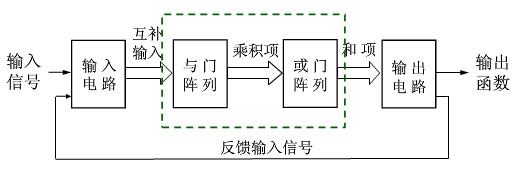

PLD即programmable logic device,译为可编程逻辑器件,是一个可以产生任意逻辑输出的通用型数字逻辑电路器件。PLD有很高的集成度,足以满足设计一般的数字系统的需要,与门、或门、非门是PLD最基本的构成。

早期的可编程逻辑器件只有可编程只读存贮器(PROM)、紫外线可按除只读存贮器(EPROM)和电可擦除只读存贮器(EEPROM)三种。由于结构的限制,它们只能完成简单的数字逻辑功能。

其后,出现了一类结构上稍复杂的可编程芯片,即可编程逻辑器件,它能够完成各种数字逻辑功能。典型的PLD由一个“与”门和一个“或”门阵列组成,而任意一个组合逻辑都可以用“与一或”表达式来描述,所以, PLD能以乘积和的形式完成大量的组合逻辑功能。这一阶段的产品主要有PAL和GAL。PAL由一个可编程的“与”平面和一个固定的“或”平面构成,或门的输出可以通过触发器有选择地被置为寄存状态。

PAL器件是现场可编程的,它的实现工艺有反熔丝技术、EPROM技术和EEPROM技术。还有一类结构更为灵活的逻辑器件是可编程逻辑阵列(PLA),它也由一个“与”平面和一个“或”平面构成,但是这两个平面的连接关系是可编程的。

PLA器件既有现场可编程的,也有掩膜可编程的。在PAL的基础上,又发展了一种通用阵列逻辑GAL,如GAL16V8,GAL22V10 等。它采用了EEPROM工艺,实现了电可按除、电可改写,其输出结构是可编程的逻辑宏单元,因而它的设计具有很强的灵活性,至今仍有许多人使用。这些早期的PLD器件的一个共同特点是可以实现速度特性较好的逻辑功能,但其过于简单的结构也使它们只能实现规模较小的电路。

为了弥补这一缺陷,20世纪80年代中期Altera和Xilinx分别推出了类似于PAL结构的扩展型 CPLD和与标准门阵列类似的FPGA,它们都具有体系结构和逻辑单元灵活、集成度高以及适用范围宽等特点。这两种器件兼容了PLD和通用门阵列的优点,可实现较大规模的电路,编程也很灵活。

与门阵列等其它ASIC相比,它们又具有设计开发周期短、设计制造成本低、开发工具先进、标准产品无需测试、质量稳定以及可实时在线检验等优点,因此被广泛应用于产品的原型设计和产品生产(一般在10,000件以下)之中。几乎所有应用门阵列、PLD和中小规模通用数字集成电路的场合均可应用FPGA和CPLD器件。

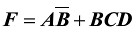

PLD是由“与门阵列”和“或门阵列”加上输入输出电路构成,任何组合函数都可以表示为与-或表达式:

用两级与-或电路实现

PLD要实现编程应用,其编程信息必须存储在芯片内部的编程元件中,或者说PLD(包括全部SPLD、CPLD、FPGA)必须使用某些特定的电子开关能够存储逻辑配置数据的存储器来作为它的编程元件

现代PLD使用的内部编程元件主要有如下三种类型

1 一次性编程的熔丝或反熔丝开关

2 基于浮栅技术的存储器。包括紫外线电擦除和电擦除的EPROM、E?PROM与闪存

3 允许无限次编程使用的静态存储器SRAM

熔丝(Fuse)或反熔丝(Antifuse)开关为一次性编程使 用的非易失性元件,编程后即使系统断电,它们中存 储的编程信息不会丢失.但它们只能写一次,故称之 为OTP(One Time Programming)编程元件.

基于浮栅技术的E2PROM和快闪存储器也是非易失性的 编程元件,但它们允许多次反复编程写入,并可为器 件设置保密位,以防止对PLD的非法复制.

静态存储器SRAM属于易失性的编程元件,掉电后它存 储的配置数据将立即消失,但它能在工作过程中快速 编程.

浮栅型编程元件和SRAM都可以多次,反复进行编程应 用.尤其是SRAM,其编程应用的次数几乎无限.