图文详情

产品属性

相关推荐

LC4032ZE-7TN48I

CPLD - 复杂可编程逻辑器件 32MC 32 I/O LOW PWR 1.8V 7.5ns

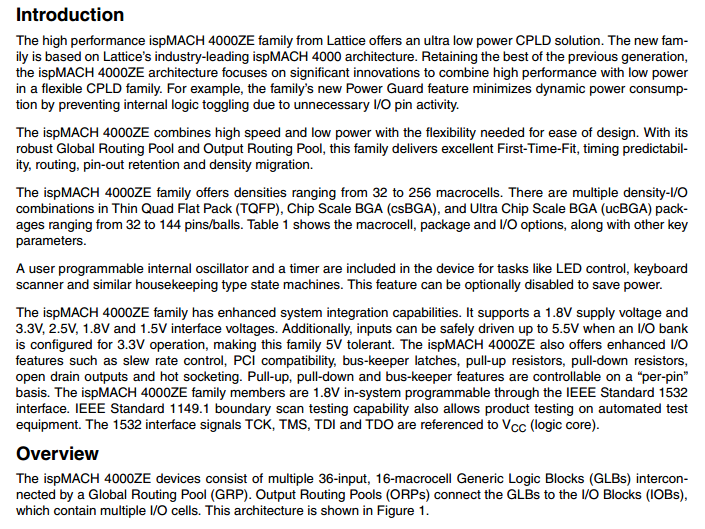

1.8V In-System Programmable Ultra Low Power PLDs

Overview LC4032ZE-7TN48I

The ispMACH 4000ZE devices consist of multiple 36-input, 16-macrocell Generic Logic Blocks (GLBs) interconnected by a Global Routing Pool (GRP). Output Routing Pools (ORPs) connect the GLBs to the I/O Blocks (IOBs), which contain multiple I/O cells. This architecture is shown in Figure 1.

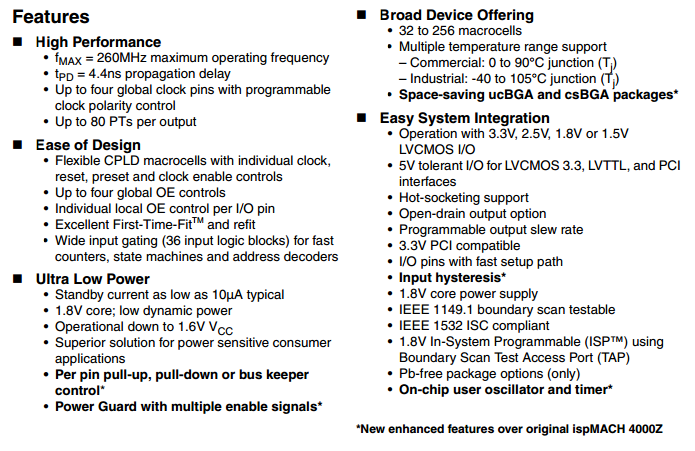

Features LC4032ZE-7TN48I

High Performance

• fMAX = 260MHz maximum operating frequency

• tPD = 4.4ns propagation delay

• Up to four global clock pins with programmable

clock polarity control

• Up to 80 PTs per output

Ease of Design LC4032ZE-7TN48I

• Flexible CPLD macrocells with individual clock,

reset, preset and clock enable controls

• Up to four global OE controls

• Individual local OE control per I/O pin

• Excellent First-Time-FitTM and refit

• Wide input gating (36 input logic blocks) for fast

counters, state machines and address decoders

Broad Device Offering

• 32 to 256 macrocells

• Multiple temperature range support

– Commercial: 0 to 90°C junction (Tj)

– Industrial: -40 to 105°C junction (Tj)

• Space-saving ucBGA and csBGA packages*

: 32

: 32 I/O

: 0.05 mA

: 1.8 V

: - 40 ℃

: + 105 ℃