图文详情

产品属性

相关推荐

MCIMX6Q5EYM10AD

处理器 - 专门应用 i.MX 6 series 32-bit MPU, Quad ARM Cortex-A9 core, 1GHz, FCBGA 624

Introduction MCIMX6Q5EYM10AD

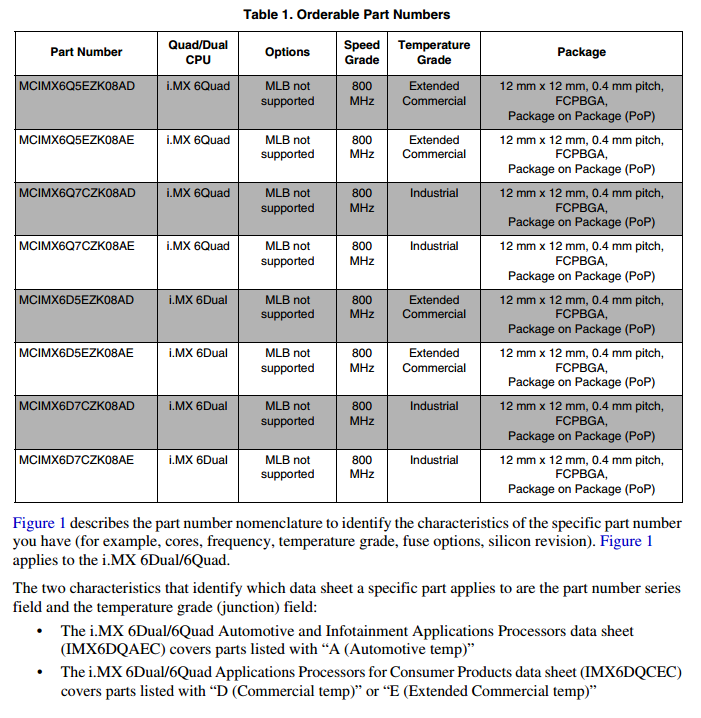

The i.MX 6Dual/6Quad processors are part of a growing family of multimedia-focused products that offer high performance processing and are optimized for lowest power consumption.

Features MCIMX6Q5EYM10AD

The i.MX 6Dual/6Quad processors are based on Arm Cortex-A9 MPCore platform, which has the following features:

• Arm Cortex-A9 MPCore 4xCPU processor (with TrustZone®)

• The core configuration is symmetric, where each core includes:

— 32 KByte L1 Instruction Cache

— 32 KByte L1 Data Cache

— Private Timer and Watchdog

— Cortex-A9 NEON MPE (Media Processing Engine) Co-processor

The Arm Cortex-A9 MPCore complex includes:• General Interrupt Controller (GIC) with 128 interrupt support

• Global Timer

• Snoop Control Unit (SCU)

• 1 MB unified I/D L2 cache, shared by two/four cores

• Two Master AXI (64-bit) bus interfaces output of L2 cache

• Frequency of the core (including Neon and L1 cache) as per Table 6.

• NEON MPE coprocessor

— SIMD Media Processing Architecture

— NEON register file with 32x64-bit general-purpose registers

— NEON Integer execute pipeline (ALU, Shift, MAC)

— NEON dual, single-precision floating point execute pipeline (FADD, FMUL)

— NEON load/store and permute pipeline

Signal Naming Convention MCIMX6Q5EYM10AD

Throughout this document, the updated signal names are used except where referenced as a ball name (such as the Functional Contact Assignments table, Ball Map table, and so on). A master list of the signal name changes is in the document, IMX 6 Series Standardized Signal Name Map (EB792). This list can be used to map the signal names used in older documentation to the new standardized naming conventions.

MCIMX6Q5EYM10AD

NXP

32位

4 Core

1 GHz

0.9 V to 1.3 V

256 kB