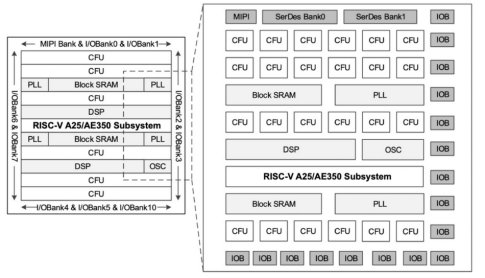

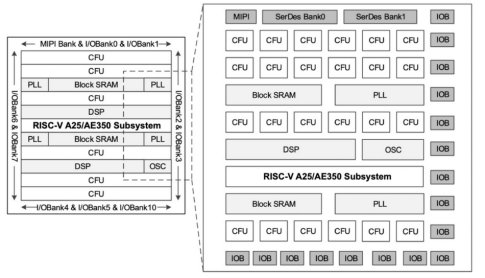

晶心科技 (TWSE: 6533; SIN: US03420C2089; ISIN: US03420C1099) 是高效率、低功耗 32/64 位 RISC-V 处理器核心的领先供应商,也是 RISC-V International 的创始高级成员,对此感到非常兴奋宣布其AndesCore? A25 RISC-V CPU IP和AE350外围子系统经过强化并嵌入到全球增长最快的FPGA公司高云半导体的GW5AST-138 FPGA芯片中。这种集成是 FPGA 中首批完整的 RISC-V 微控制器之一,为设计人员提供了 A25 处理器能力和大多数处理器所需的外设,而无需消耗任何 FPGA 资源。因此,硬件团队可以将其增值设计填充到 FPGA,而软件团队可以同时基于丰富的 RISC-V 生态系统创建应用程序代码。

“晶心致力于提供尖端的 RISC-V 技术,让开发人员能够创建创新且高效的解决方案。将A25 RISC-V CPU和AE350外围子系统作为硬核集成到高云半导体的GW5AST-138 FPGA中,标志着实现这一愿景的一个重要里程碑。”晶心北美销售副总裁Vivien Lin表示。“这代表了 RISC-V 架构的一个重要里程碑,因为它为我们的共同客户提供了一个多功能硬件开发平台,用于在提交硅制造网表之前创建、调试和验证他们的最终 SoC 设计。对于不需要 SoC 的客户来说,它将启用完整的 RISC-V 计算机来驱动他们的最终应用程序。”

“在 Arora V 系列中,我们集成了 RISC-V CPU 在硬实例化中通常需要的外设,”高云解决方案开发高级总监 Jim Taka 说道。“我们提供了完全可控的高速 SerDes,用于需要非常高数据速率的通信、视频聚合和 AI 计算加速应用。其他实例化功能包括支持 ECC 纠错的 Block RAM 模块、高性能多电压 GPIO 和高精度时钟架构。这些硬功能为设计人员的独特逻辑实现节省了多达 138K LUT 的 FPGA 可编程结构。”

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。