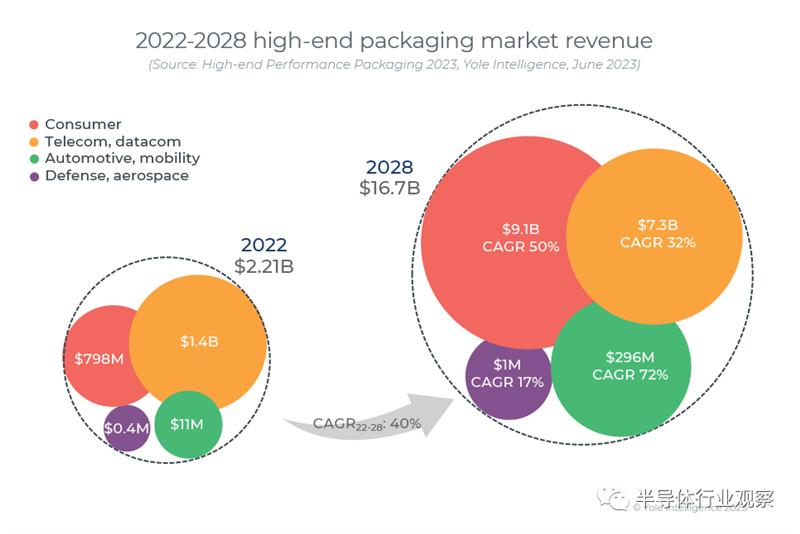

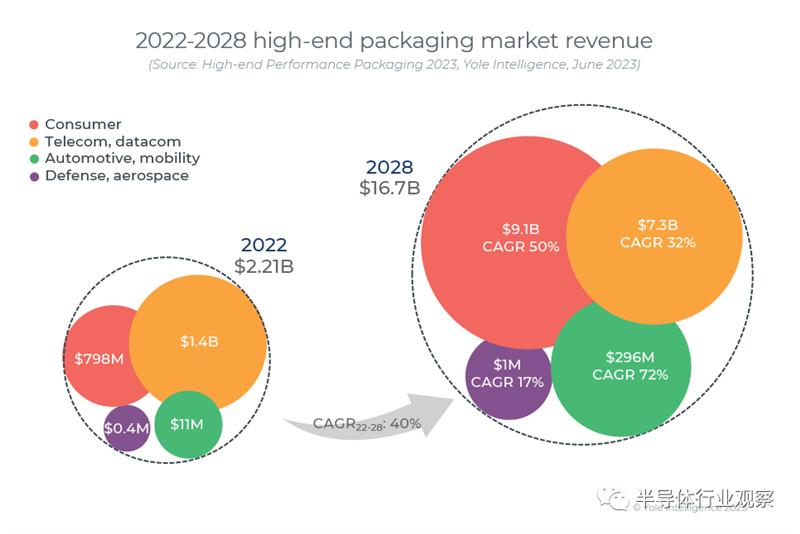

据Yole预测,高端封装市场在 2022 年价值22亿美元,预计到 2028 年将超过160亿美元,2022-2028 年的复合年增长率为40 %。进一步细分到终端市场,高端性能封装最大的终端市场是 “电信和基础设施”,到 2022 年占市场总收入的 60% 以上。但是,它应该被 “到 2027 年移动和消费终端市场。同样重要的是,高端封装的最快终端市场增长 来自“移动和消费”和“汽车和移动”,复合年增长率分别为 50% 和 32%。

就封装单位而言,高端封装预计将在2022 年至2028 年实现 43% 的复合年增长率,从 2022 年的 5.11 亿个增加到2028年的 43.79 亿个. 这种巨大的增长是由于高端封装的需求正在以非常健康的方式增长,平均售价与不太先进的封装相比非常高,因为价值从 2.5D&3D平台逼迫的前端业务到后端业务 。

3D 堆栈存储器——HBM、3DS 和 3D NAND——是最大的贡献者,到 2028 年占总市场份额的 70% 以上。增长最快的四大 =平台是 3D SoC、有源硅中介层、嵌入式硅桥和 3D NAND堆。

高端性能封装正变得越来越复杂 所有高端性能封装平台的主要技术趋势包括减少互连间距,无论类型如何。这涉及到 TSV、TMV、 微凸块,甚至混合键合,这已经是最激进的解决方案。除此之外,通孔直径和晶圆厚度有望降低。这种技术发展对于一方面保持更复杂的单片芯片的集成,另一方面保持小芯片的集成是必要的,以支持更快的数据处理和传输, 同时确保更低的功耗和损耗,并为后代提供更高的密度集成和带宽 .

Chiplet 和异构集成是推动采用 HEP 封装的另一个重要趋势,因为市场上已经有使用这种方法的产品。例如使用 EMIB 的 Sapphire Rapids;Ponte Vecchio 使用 Co-EMIB;和使用英特尔Foveros的Meteor Lake 。

此外,亚马逊在其 Graviton3中使用了英特尔的 EMIB 技术。AMD 是另一个在 Ryzen 和 Epyc等产品中采用这种技术方法的重要参与者,从第 3 代开始,以及在其 MI250 中重复裸片,这要归功于使用mold interposer 和mold compound中嵌入硅桥的封装。在mold compound中嵌入硅桥以及mold interposer也被用于 Apple 的 M1 Ultra,以实现芯片复制。特斯拉的 Dojo D1 使用台积电的InFO_SoW解决方案——在同一封装中互连 25 个小 芯片。Biren 使用台积电的 CoWoS解决方案在其 BR100 中互连两个小芯片芯片。正如英特尔、AMD、Nvidia 等重要参与者明确宣布的那样,更多包含分区或重复芯片的封装预计将在来年投放市场 。

共封装 pptics (CPO:Co-packaged pptics) 是一种先进的光学和硅在单个封装基板上的异构集成,旨在应对下一代带宽和功率挑战。即使它不会很快被采用,这种方法也将代表一项重要的技术 改进。事实上,ASE 已经在其路线图中宣布了为这种包配置提供服务的能力。

混合键合是当今的热门话题,因为该技术通过其用于 3D NAND 堆栈存储器和 CIS 的 W2W 解决方案以及 Graphcore 的 BOW IPU等逻辑到逻辑产品,这使其越来越受欢迎。2022 年, 由于台积电的 3DFabric的推出, AMD 将其 V-Cache 技术商业化,其 Ryzen 和Epyc 产品率先使用 D2W 方法进行 SRAM 到逻辑芯片互连。混合键合应该会受到更多关注,因为collective D2W 方法有望用于 HBM3+ 代中的 DRAM 堆叠。此外,使用这种方法的新参与者将渗透到市场中。下一步将是使用 D2D 方法来支持 chiplet 和异构集成趋势。

3D技术趋势是在未来几年采用更多的HB进行堆叠。内存玩家会多用W2W,然后集体D2W HB。逻辑玩家将使用更多的 D2W HB,这也为异构集成提供了更大的灵活性。W2W 方法将随之而来,也将越来越流行 。将 TSV 与用于 HBM 和 3DS 的微凸块相结合的经典方法将继续作为一种解决方案占据主导地位,而未来将有裸片到中介层 HB 选项。

总的趋势是将更多的 2.5D 平台与 3D 平台结合在同一个封装中。因此,我们预计未来的封装将使用 3D SoC、2.5 中介层、嵌入式硅桥和共同封装的光学器件集成 到 同一封装中。新的 2.5D 和 3D 封装平台将 在稍后投放市场,使 HEP 封装变得更加复杂。

随着一些参与者提出 HEP 封装解决方案,高端封装供应链正在朝着具有可持续商业案例的长期生存能力发展 ——如果没有这些解决方案,目前市场上的某些产品和性能甚至无法实现 。那是因为高端封装平台正在向前端制造靠拢。显然,需要前端能力来生产硅中介层、硅桥、3D 堆叠存储器和 3D SoC。因此,台积电、英特尔和三星是推动 HEP 封装创新的主要参与者。TSMC 展示了其 3DFabric,利用 CoWoS 、 InFO和 3D SoIC 解决方案。英特尔正在使用其 Foveros、EMIB 和 Co-EMIB 产品,以及后来的 Foveros Direct & Omni。三星是 HBM 和 3DS 内存的先驱 ,并提供 I- CubeS 、H-Cube,以及后来的 R-Cube 和 X-Cube 。

目前,不同商业模式(晶圆代工、IDM、OSAT)的企业都在同一个高端封装市场空间展开竞争。然而,能够实现高水平包装质量的玩家数量有限,因为高端或在某些情况下前端制造和集成的复杂程度使得玩家难以打入市场 。2022 年,长江存储、三星、SK 海力士和美光在收入市场份额方面占据市场主导地位,因为 3D 堆栈存储器是 HEP 封装业务的主要贡献者 。

高端封装供应链的进入门槛越来越高,尤其是混合键合的采用,让OSAT厂商无从下手。英特尔、台积电和三星等大公司已成功利用先进封装市场的增长,并在高端性能封装方面实现了比 OSAT 更快的上市时间。这种策略对 OSAT 构成了间接但强大的威胁。

在高端封装中,OSAT 的业务正在被代工厂和 IDM 蚕食。展望未来,无晶圆厂可能会被尖端交钥匙服务的前景所吸引,例如最新的硅节点制造技术加上先进的封装。然而,日月光、SPIL、Amkor、JCET、TF 和 华天等顶级 OSAT 正在努力跟上领先封装业务的步伐,专注于 2.5D 解决方案,如mold compound中的有机中介层和嵌入式硅桥。这是进入混合键合市场的缺失可能性的一个很好的替代方案。即使 OSAT 无法生产接近 FE 制造的 HEP 封装解决方案,它们在最终封装组装和测试中无处不在。

OSAT 和基板供应商可能会在系统级获得巨大的封装价值,但他们在财务或技术上不具备利用现有设备和材料专业知识自行制造和管理 FE 芯片的能力。因此,他们可以转向无晶圆厂、晶圆代工或 IDM 寻求合作伙伴关系,或直接寻求并购机会。

过去两年有很多投资和产能扩张公告,主要发生在中国。预计会有更多的 中国企业使用或提供 HEP 包装解决方案,参与业务增长。技术提供商仍然是主要参与者,提供更多 2.5D 和 3D 技术封装选项。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。