在

电子电路设计中,电源反接是一个可能导致电路损坏甚至引发安全事故的问题。为了避免这种情况的发生,各种防反接电路应运而生。下面我们将对常见的防反接电路进行深入解析,尤其聚焦于 MOS 管防反接电路。

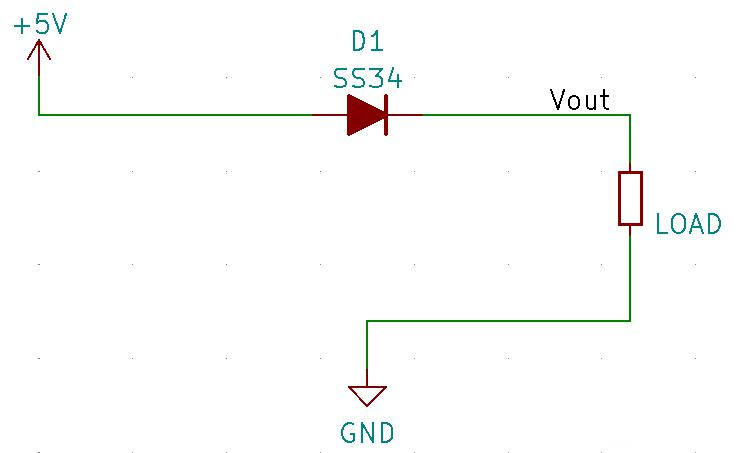

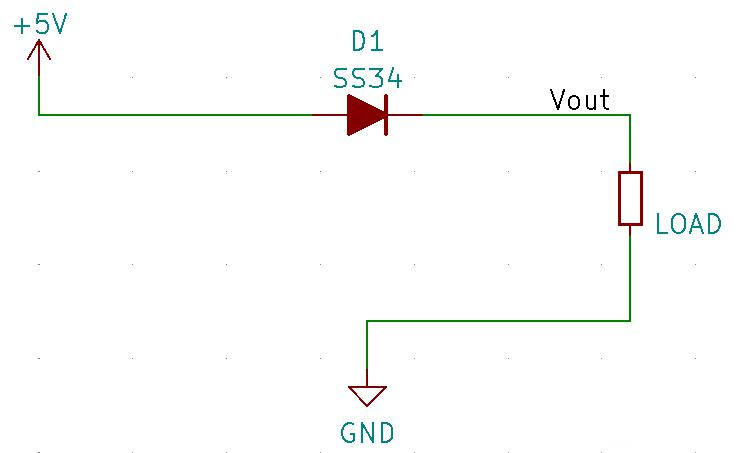

这种电路利用二极管的单向导电性,将电源的正极与负极相连。当电源极性正确时,二极管正向导通,电流可正常通过;而当电源极性反接时,二极管反向截止,电流无法通过,从而实现防反接功能。然而,该电路存在明显缺点,经过二极管后会产生压降,这会拉低负载电路的电压,影响负载的正常工作。

整流桥由 4 个二极管组成,能自动纠正电源的正负极性。当电源极性正确时,整流桥输出与电源输出相同;当电源极性反接时,整流桥会自动调换电源正负极性。不过,此电路会产生两个二极管的压降,同样会拉低负载电路电压。

该电路使用 PMOS 管作为开关。当电源极性正确时,MOS 管导通,电流正常通过;当电源极性反接时,MOS 管截止,电流无法通过。MOS 管的导通电阻极小,导通压降可忽略不计,这是其显著优点。

与正常 MOS 管应用电路不同的是,此处 VDS>0,后续会详细解释。

与正常 MOS 管应用电路不同的是,此处 VDS>0,后续会详细解释。

此电路结合了保险丝和稳压管。当电源极性正确时,保险丝正常工作;当电源极性反接时,稳压管反向导通,保险丝熔断,切断电路,保护后级电路安全。它不仅能防止反接,还能防止过压和过流。

在电源正接时,PMOS 的寄生二极管截止。假设 VS = 5V,VG = 0V,则 VGS = 0 - 5V = -5V <-VGS (th),PMOS 导通。但当电源反接时,寄生二极管会导通,电源与负载电路未完全断开,这种电路可靠性较差。

当电源正接时,VS = 5V - 0.7V = 4.3V,VG = 0V,VGS = 0 - 4.3V = -4.3V <-VGS (th),PMOS 导通。而在电源反接时,寄生二极管和 MOS 管都断开,电源与负载电路完全断开,可靠性高。

MOS 管存在寄生电容,如 C (GD)、C (GS)、C (DS)。寄生电容是指电感、电阻、芯片引脚等在高频情况下表现出的电容特性。一个电阻在高频下可等效为一个电容、一个电感和一个电阻的串联,低频时表现不明显,高频时等效值增大。MOS 管常需数十 K 乃至数 M 的开关频率,频率越高,交流成分越大,寄生电容会通过交流电流形成栅极电流,消耗电能并产生热量,不可忽视。MOS 管的寄生电容主要包括输入电容 (Ciss)、输出电容 (Coss) 和反向传输电容 (Crss)。输入电容是 MOS 管输入端施加信号时所需的电荷量,由栅极和源极、栅极和漏极之间的电容组成;输出电容是输出端施加信号时所需的电荷量,由漏极和源极、栅极和漏极之间的电容组成;反向传输电容是栅极施加信号时所需的电荷量,由栅极和漏极之间的电容组成。这些寄生电容会影响 MOS 管的开关速度和性能,在电路设计时需充分考虑,避免与外部电路冲突,确保电路正常运行。

GS 间的并联电阻有两个重要作用。一是作为泄放电阻,释放寄生电容 Cgs 的电流;二是保证 MOS 管有效关断。当 G 级开路时,DS 端的电压会给 C (GD) 充电,导致 G 级电压升高,使 MOS 管不能有效关断。有并联电阻后,G 级开路时 GS 端等电位,可保证 MOS 管有效关断。

G 级串联电阻也有两个关键作用。一是减小电流,它与 Ciss(Ciss = Cgd + Cgs)形成 RC 充放电电路,可减小瞬间电流值。二是减小振荡,MOS 管接入电路时,引线会产生寄生电感,与寄生电容一起形成 LC 振荡电路。开关方波波形包含多种频率成分,可能与谐振频率相同或相近,形成串联谐振电路。串联一个电阻可减小振荡电路的 Q 值,使振荡快速衰减,避免引起电路故障。

图 1:VDS<0 的 MOS 管防反接电路

图 2:VDS>0 的 MOS 管防反接电路

与正常 MOS 管应用电路不同的是,此处 VDS>0,后续会详细解释。

与正常 MOS 管应用电路不同的是,此处 VDS>0,后续会详细解释。