即使没有

电容器,如果用作AC

信号源,则设计思想(DI)pWM驱动电路的时间常数和非线性性质也有限制。当然,DI的标题清楚地表明,向负载提供交流电流不是性能目标。但是其中一位评论者对交付AC和DC电流感兴趣。

基本LM317当前来源 我想知道,如果由LM317和电阻RS和RC组成的子电路,如果电路是从合适的控制电流驱动的。在图1中,研究此过程的步是模拟由U1和RS1制成的基本LM317

电流源[1]驱动负载RL1。负载电流为10 mA。

图1在模拟和测试

工作台上研究的一系列LM317电路作为当前源。

模拟了电路的宽带PSRR,以欧姆测量,并定义为V1

电源与AC电流通过RL1的交流电压之比。从DC到近1 kHz,结果略高于100kΩ,在10kHz下降至10kΩ以下。到目前为止,一切都很好。接下来,测试了包含U2的候选子路。理想的无限阻抗DC电流源I1(选择为了确保子电路性能的降解)安排RL2也接收10 mA DC。我希望在这里几乎相同的PSRR。但令我惊讶的是,DC至1KHz的阻抗降至2kΩ略低于2kΩ,在10 kHz时降至100Ω以上!

,根本没有流过LM317调整引脚的电流,甚至没有数据表的标称50 A DC。结果,也没有任何AC电流流过RC2或调整,以解释PSRR降低。显然,LM317文件[2]用于模拟不适合测试PSRR。

对PSRR进行了测试的电路是将U3作为中心元素的电路。结果比从直流到1 kHz的模拟U1:500kΩ更接近,但也更好,在10 kHz时下降至360kΩ,在50 kHz时跌至80kΩ。但是当我在板凳上时,我开始仔细观察其他一些事情。

U3电路通过从LM317的VREF(OUT和ADJ之间的电压差)从RC3上减去VDROP的电压下降,并在RS3上施加VREF - VDROP。必须仔细注意VDROP的准确性,这是足够的挑战。但是那是vref;它的极限是什么?

我决定进行一些DC测量。我有八个Texas Instruments LM317KCS IC(TO-220套件),所有这些都带有相同的日期代码标记。使用U4电路,我测量了其中每个电路的VO(OUT),将V4设置为12 VDC。 VO范围从1.243 V到1.263 V,差异为20毫伏。对于其中一个,我将V4设置为5分钟,然后在同一时间段内将V4设置为25 V。

经过这些时间间隔后,测量结果显示VO中的27 mV下降。这超过25°C下的5 mV,该5 mV来自规格线调节,每1V线电压变化为.04%。因此,我重新检查了我的测量结果,但得到了相同的结果。从所有这些测量值中,不可能确定VREF在不同IC,负载电流,直流输入电压和任意电路的连接温度上的极限。当然,诺亚的报仇是:每40天,长期稳定参数每40天就可以给我们带来1%的VREF班次:12.5 mv。从所有这些方面,我对VREF的规格参考电压极限为1.25 v±50 mV。那么这种歧义有什么影响?

我们确实需要一个可编程的供应,因此,让我们坚持使用U2配置并延期考虑实用的可编程电流源代替I1。不管电阻值如何,该电路传递给负载的电流为:

iload = vref / rs +(iadj - i1) * rc / rs 当i1为零时,会发生ILOAD,IMAX的值。当要求电路传递IMAX/10时,(IADJ - I1) * RC理想情况下将设置为约9 * VREF。但是现在ILOAD等于125±50mV; ±40%的变化!如果需要小于iMax/10,情况会变得更糟。我欢迎有关如何处理此处看到的有限准确性和操作范围的建议。但是现在,让我们考虑图2电路。

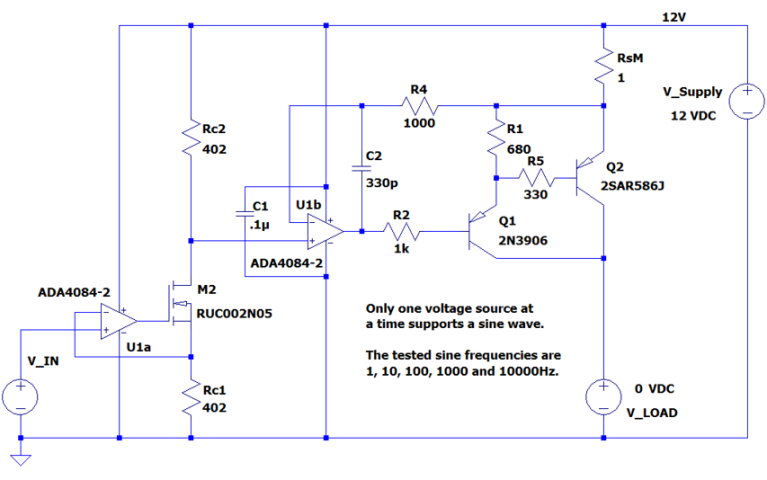

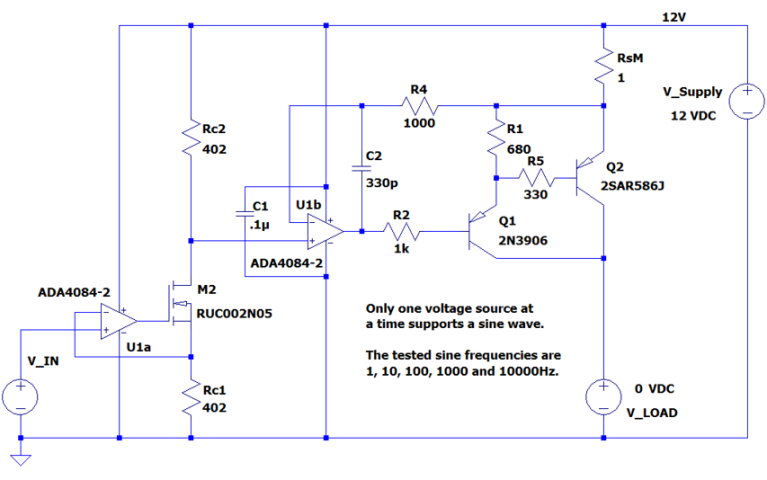

图2 Darlington Q1/Q2带有电流为0-Ω负载,V_负载。 R2,R5,R4和C2建立稳定性,应在组装电路中检查。 R1建立了Q1 DC偏置。

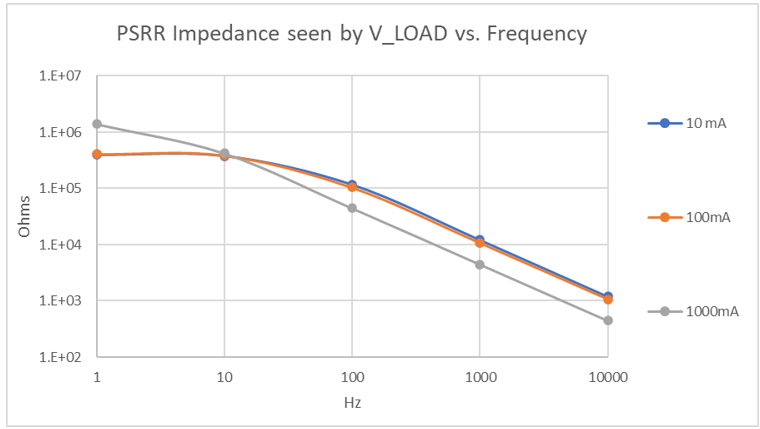

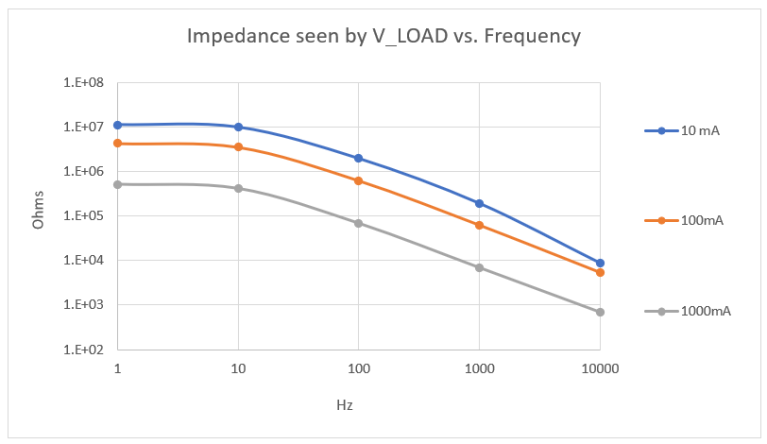

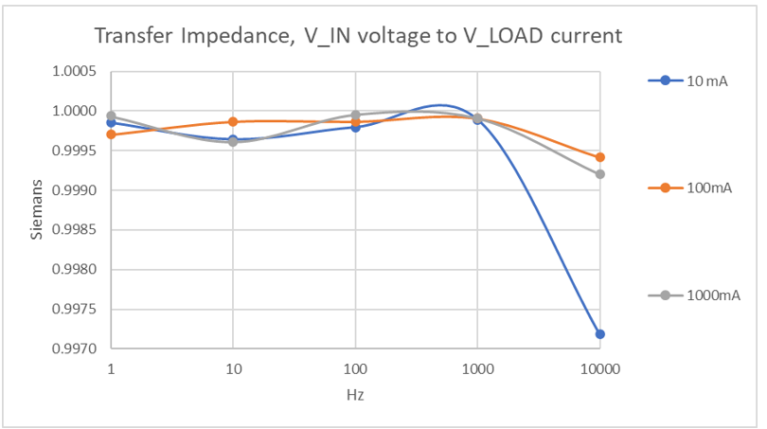

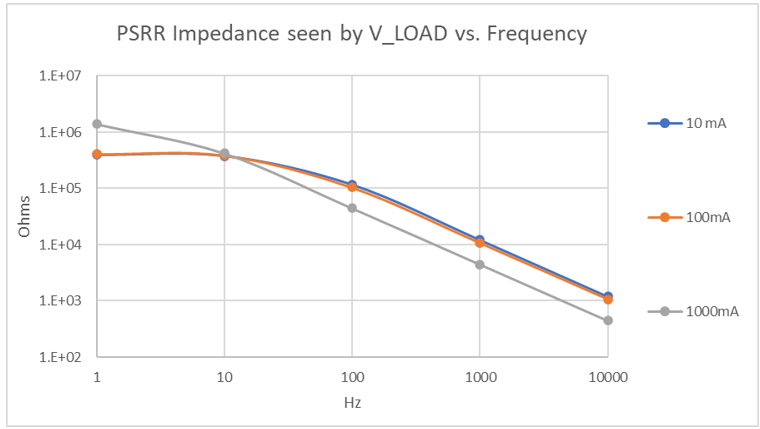

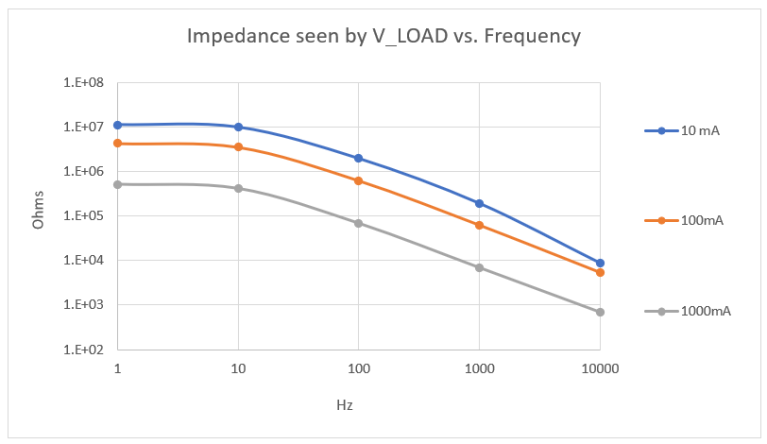

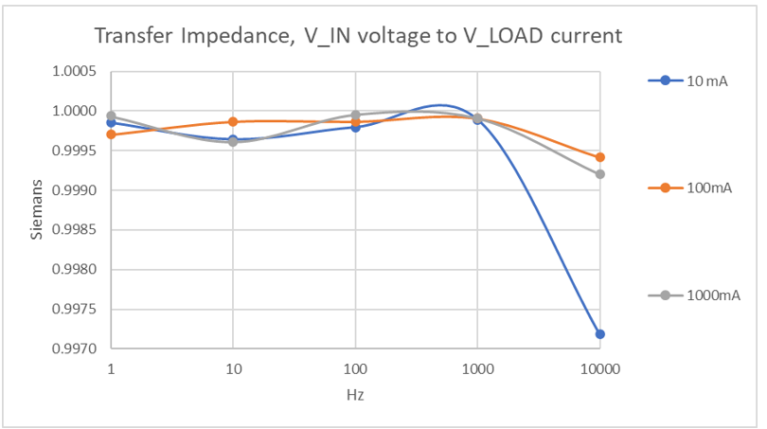

在图2中,v_supply在12 VDC处提供功率。 V_IN采用10、100和1000 mV的直流电压,以产生10、100和1000 mA的直流电流通过V_负载。示意图中的每个电压源以1、10、100、1000或10000 Hz的频率产生一个正弦波,以测试PSRR(图3),输出阻抗(图4)和信号传递(图5);但是只有一个正弦源活跃。 当活动为1-V峰时,V_LOAD和V_SUPPLY的正弦振幅,而对于V_IN为1 mV;因此,当用V_IN所采用的三个不同的直流电压总结时,净电压和电流将保持正值。所有仿真测量均通过V_load进行电流。表1列出了流过该负载的模拟经文所需的直流电流。

图3欧姆经文中的PSRR阻抗频率如V_load所示,对于三种不同的DC电流。更高的阻抗与更理想的当前来源有关。 (曲线上的点表示模拟测量。)

图4 V_负载在三种不同的DC电流下看到的欧姆阻抗。更高的阻抗与更理想的当前来源有关。曲线上的点表示模拟测量。

图5欧姆经文中的阻抗从v_in到v_load。设计目标的值为1.0000。曲线上的点表示模拟测量