微控制器、微处理器和现场可编程门阵列 (FPGA) 等数字 IC 的可用性不断增加,使开发人员能够使用复杂的数字处理技术,而不是模拟信号调理。因此,模数转换器 (ADC) 已成为混合信号电路中广泛使用的组件。

ADC 有多种类型:逐次逼近 ADC、ΣΔ (ΣΔ) ADC、直接转换 ADC、基于

电容器充电/放电的 ADC、具有电压频率转换器的 ADC 等。所有这些 ADC 都提供不同的精度特性、采样率限制和成本点。

本文概述了选择 ΣΔ ADC 时的三个主要设计注意事项。

Σ-Δ ADC 基础知识

一阶 ΣΔ ADC 的主要组件是:

积分器

比较器

1 位数模转换器 (DAC)

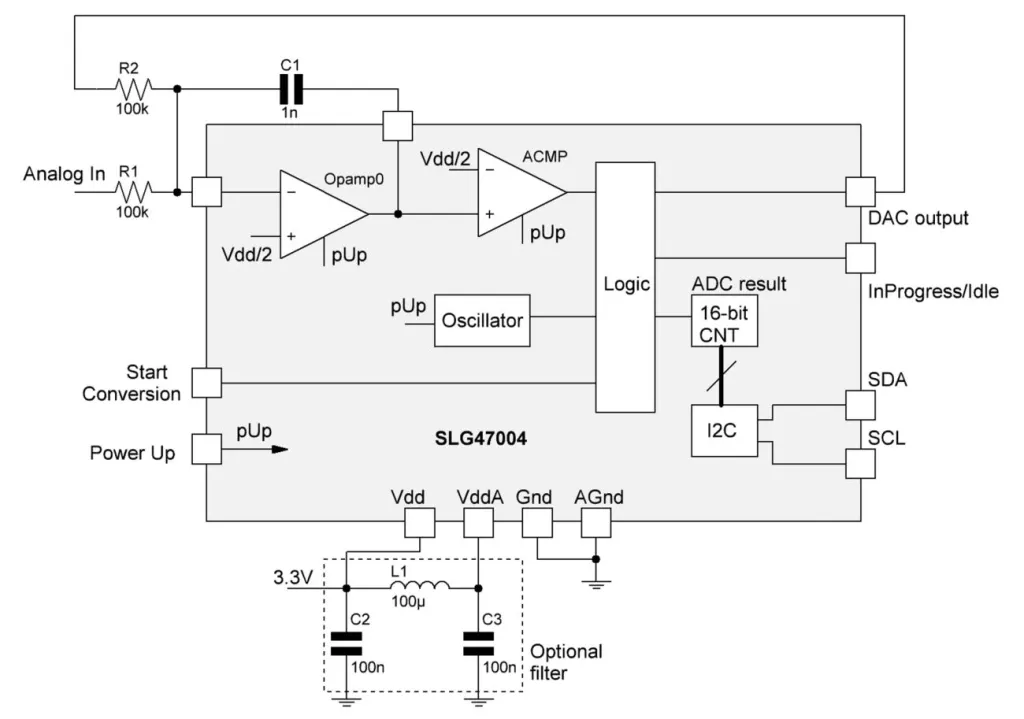

数字滤波器 一阶 ΣΔ ADC 的简化原理图如图 1所示。

图 1该原理图显示了 ΣΔ ADC 的基本构建模块。资料瑞萨

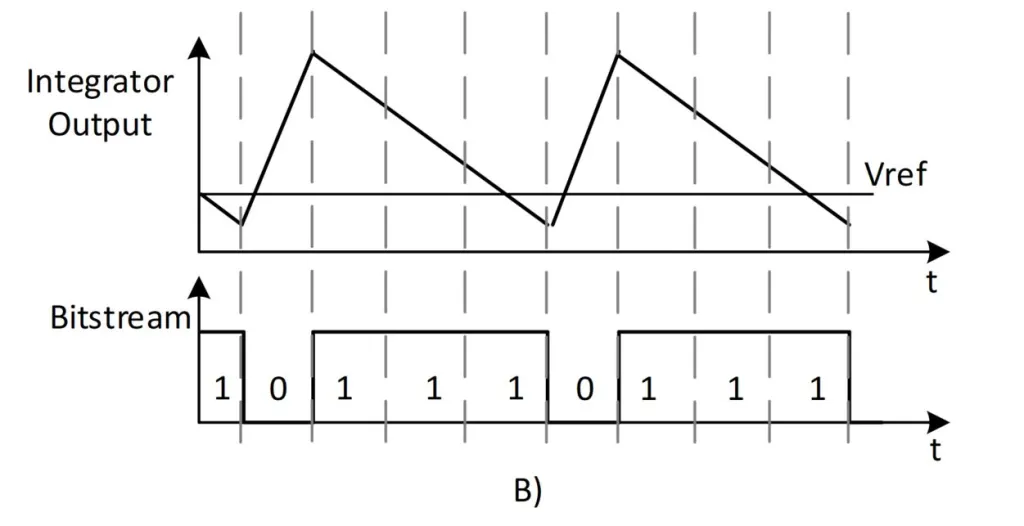

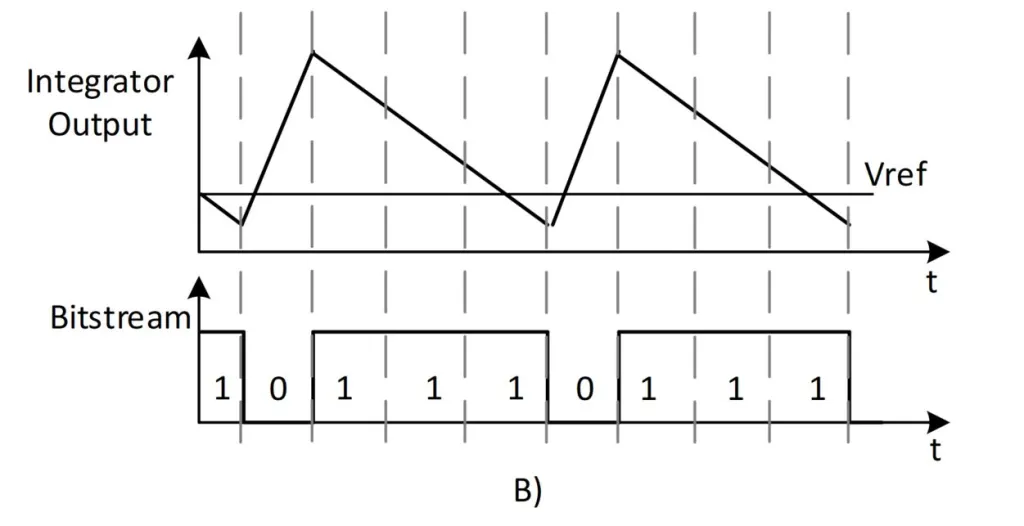

电子 ΣΔ ADC 的工作原理基于积分器电容器电荷的周期性平衡。积分器线性改变其输出,直到超过阈值。当超过阈值时,比较器将 1 位 DAC 的状态更改为相反状态。这迫使积分器沿相反方向改变其输出——向上或向下,具体取决于 DAC 输出。然后重复该过程。比较器必须使用外部时钟脉冲同步改变 DAC 状态(图 2)。

图 2 (A) 的 ΣΔ ADC 波形等于 V in = V dd /2,(B) V in = V dd *3/4。资料瑞萨电子

在一个积分器周期内,ΣΔ ADC 可被视为低分辨率 ADC。为了获得高分辨率的结果,必须对多个时期的数据进行平均。这种固有的过采样和平均功能使 ΣΔ ADC 能够极大地降低噪声并获得高分辨率数据——现代 ΣΔ ADC 多可提供 24 个无噪声位。

比特流(同步比较器的输出)被输入到数字滤波器。典型的滤波器是移动平均低通 sinc1、sinc3 或 sinc5 滤波器。

ΣΔ ADC 结构

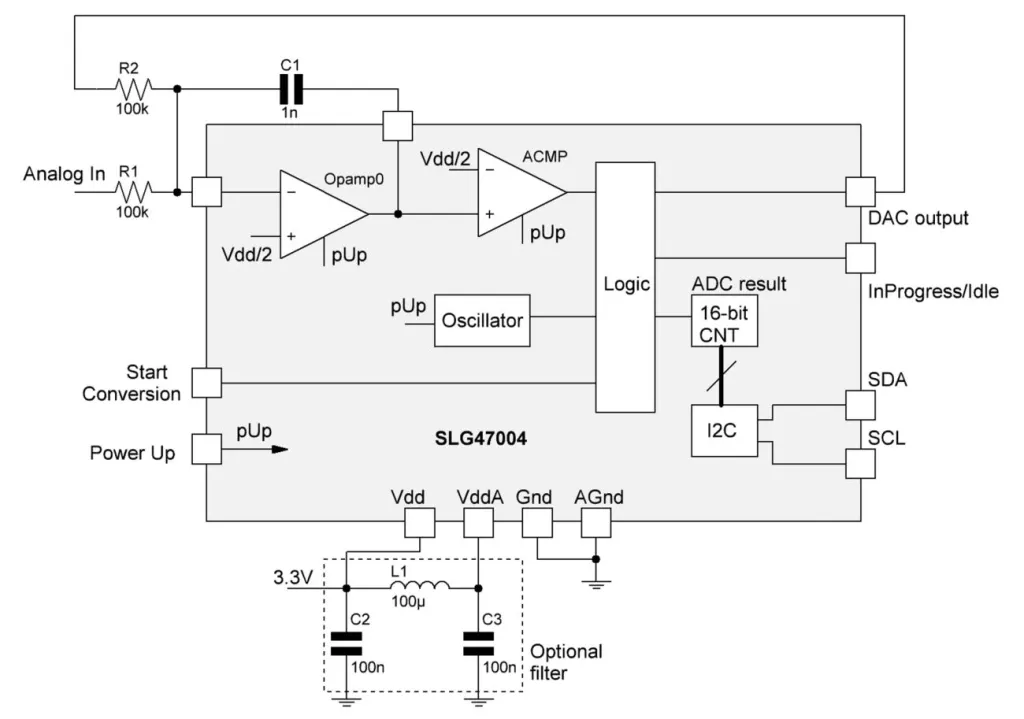

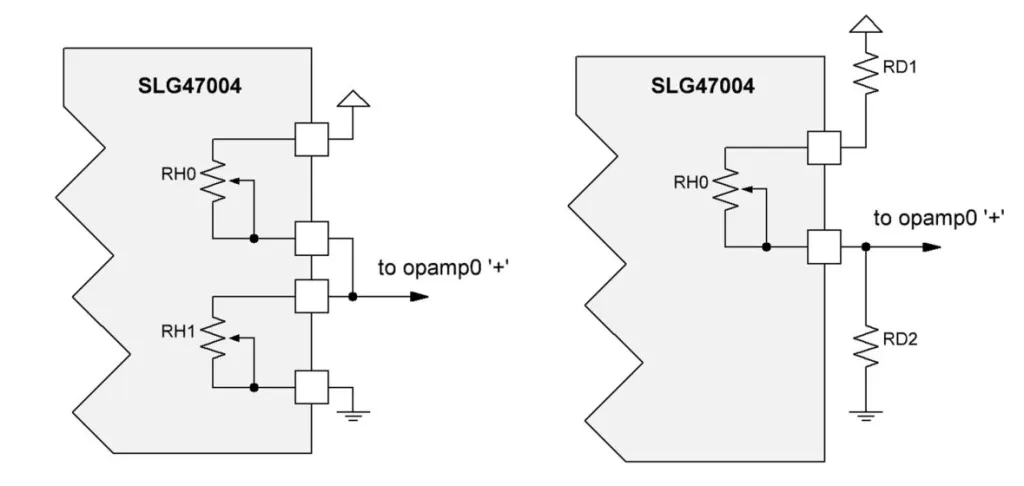

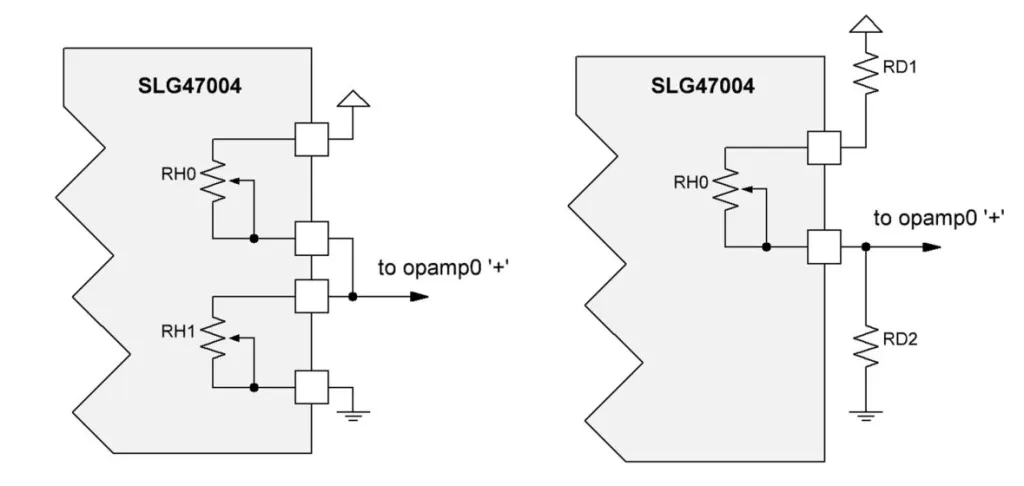

可配置混合信号 IC 的简化结构如图 3所示。基于 Opamp0 的积分器将输入信号和来自 1 位 DAC 的信号相加。积分器和比较器的参考电压为V dd /2。请注意,可以使用数字变阻器分压器代替内部 V dd A/2 基准来补偿 Opamp0 的偏移(图 4)。 ADC 参考电压为 ADC_V ref =V dd =V dd A。

图 3 ΣΔ ADC 的简化结构基于 SLG47004 可配置混合信号 IC。资料瑞萨电子

1 位 DAC 是配置为 1x 推挽输出引脚的 GPIO。 16 位计数器用作累加器,对模拟比较器 (ACMP) 输出为高电平的时钟脉冲数进行计数。 16位计数器的计数周期为

振荡器的65536个脉冲。低电平上电信号会关闭 Opamp0、ACMP 和振荡器。当不使用 ADC 时,这可显着降低SLG47004的功耗。

图4数字变阻器的可选连接调整Opamp0的参考电压。资料瑞萨电子

ADC 结果存储在 16 位 CNT0 的当前计数值寄存器(寄存器字节 CBh、CCh)中。结果可以通过 I 2 C 接口读取。 如果加电输入为高电平,则开始转换输入的上升沿将启动采样过程。可以监视进行中/空闲输出以定义转换的结束。要开始新的采样过程,应将上升沿重新应用于开始转换输入。 ADC 的采样率为每秒 1.95 个样本。

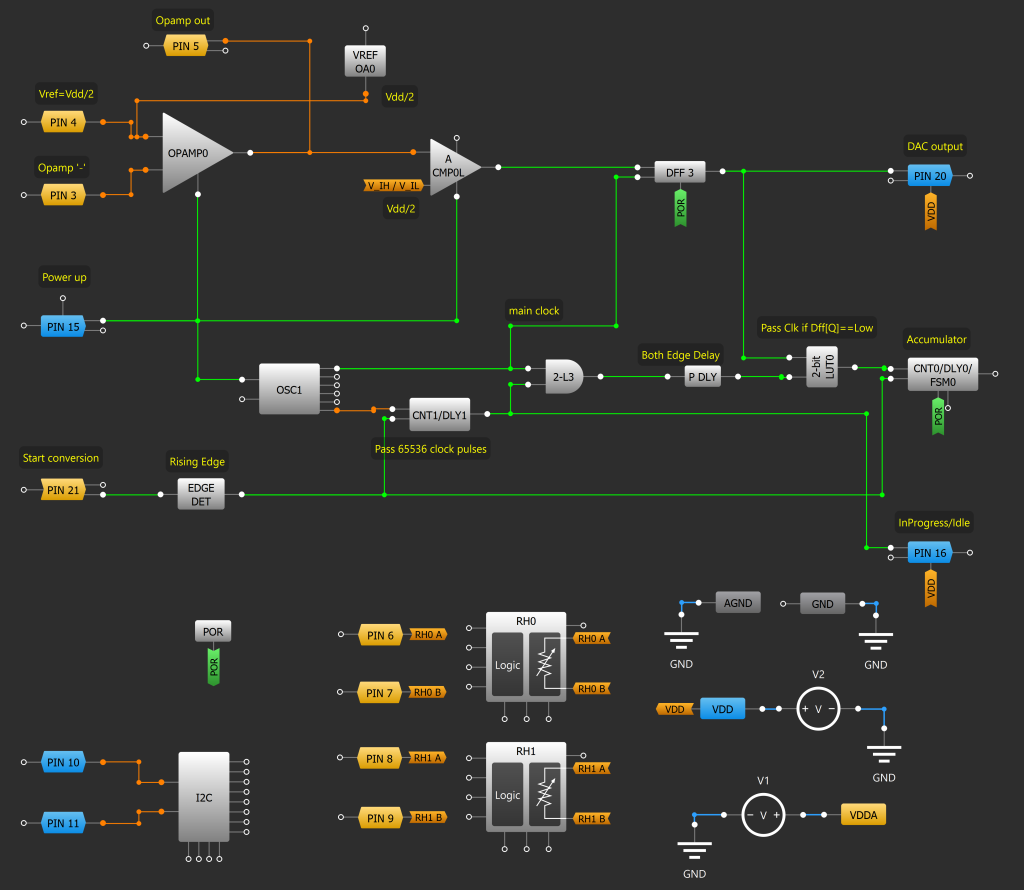

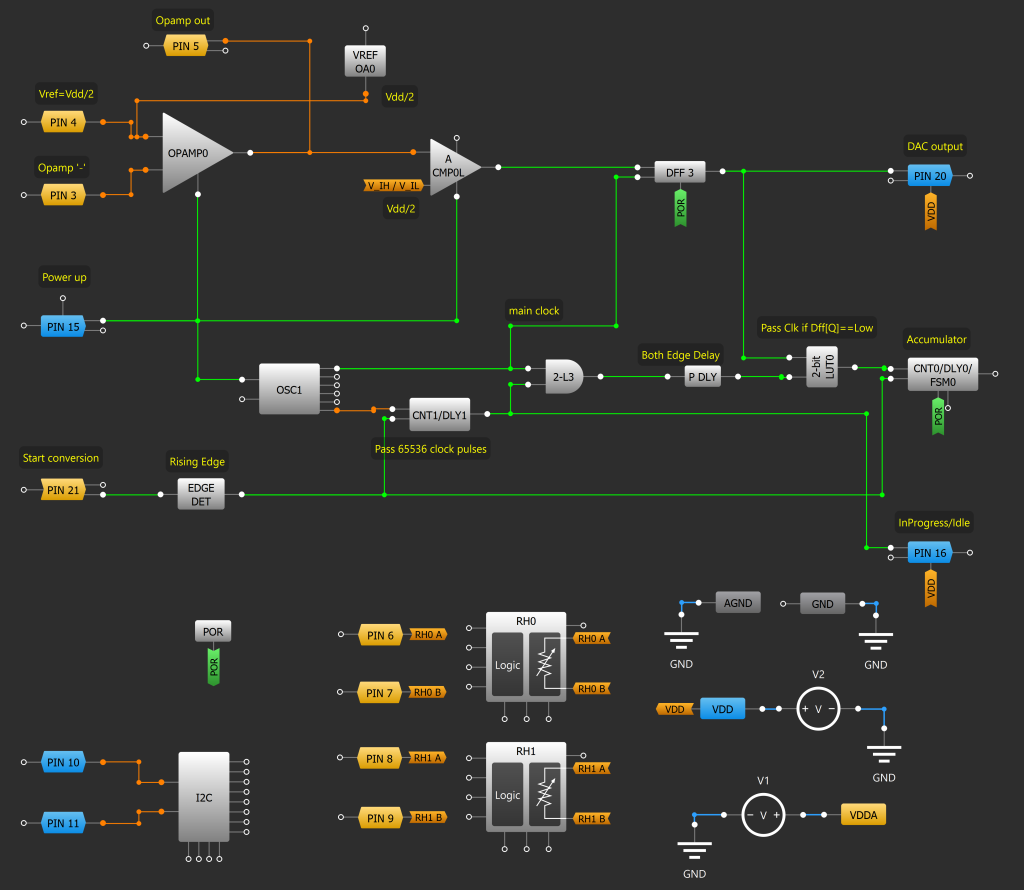

图 5显示了围绕 ΣΔ ADC 构建的GreenPAK Designer 软件项目的视图。

图 5 GreenPAK Designer 项目中的 ΣΔ ADC 基于 SLG47004 可配置混合信号 IC。资料瑞萨电子

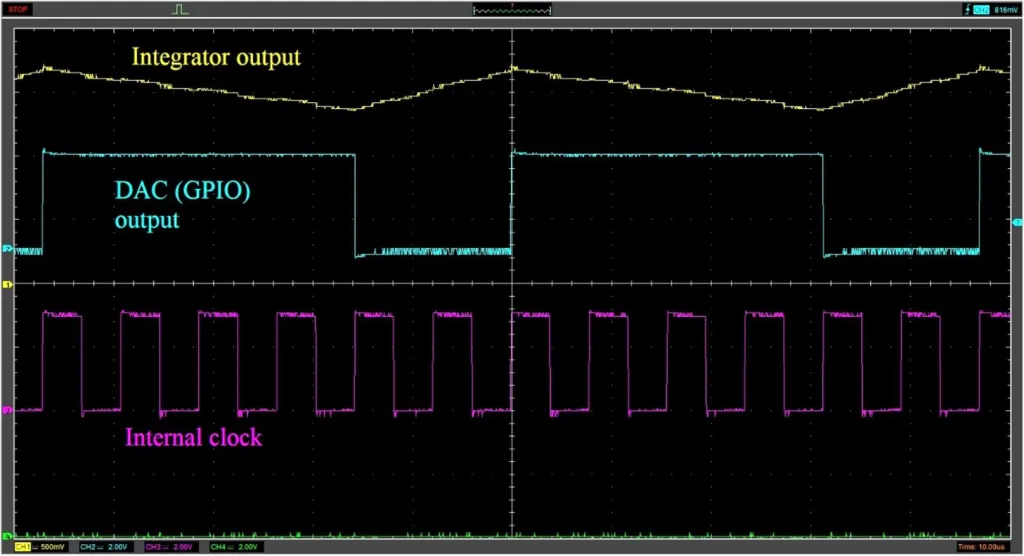

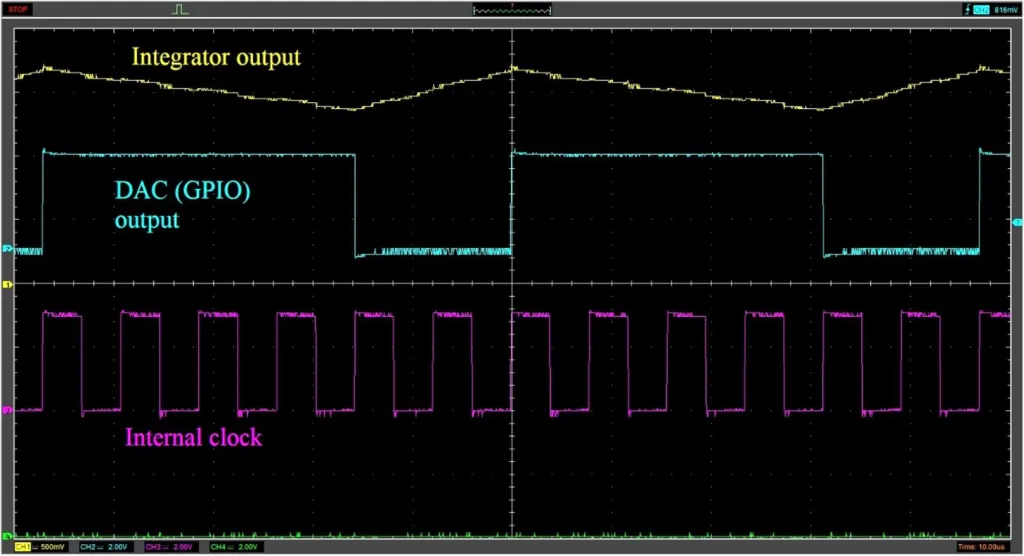

硬件原型波形如图6所示。

图 6 V in =1.0 V 相当于 ADC_V ref =V dd =3.0 V的硬件原型波形。Renesas

精度特性

为了估计 ADC 的精度特性,使用了外部 24 位 ΣΔ ADC。外部 ADC 配置为以 1 ksps 的速度在 16 位模式下运行,平均采样 128 个样本。 SLG47004 和外部 ADC 使用相同的 3V 电压参考。对于 SLG47004,V dd =V dd A=ADC_Vref。 SLG47004 使用变阻器分压器为 Opamp0 提供参考。两个数字变阻器的代码都是 1023。

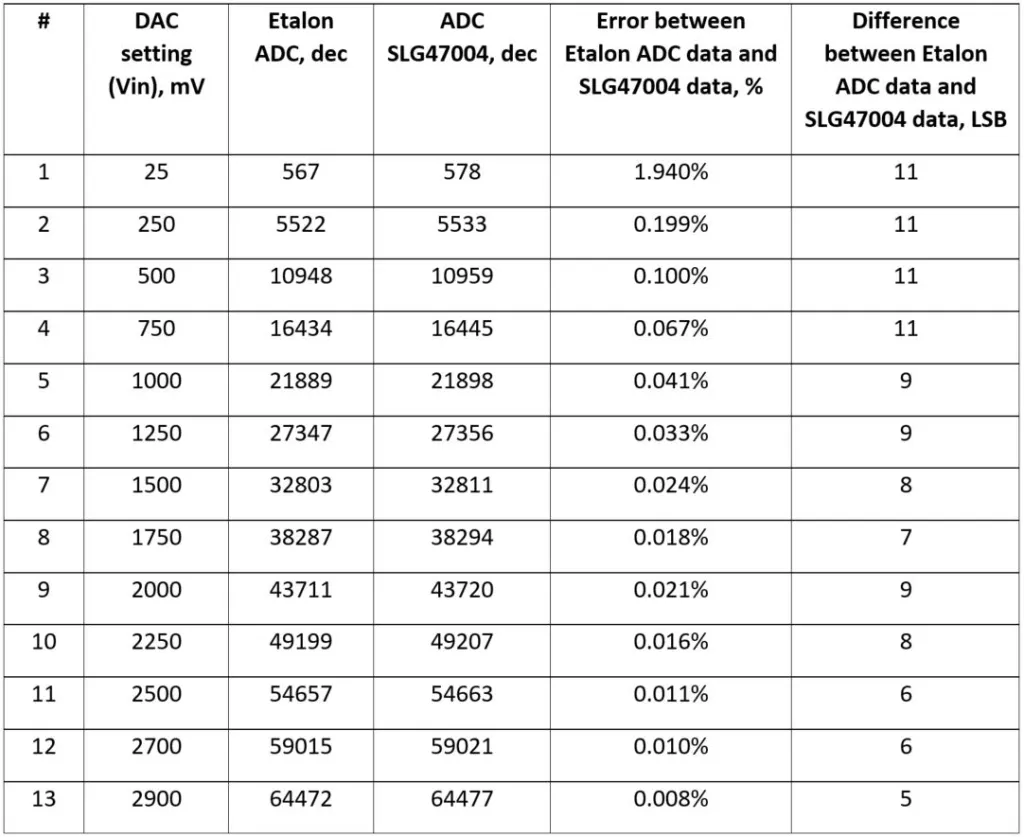

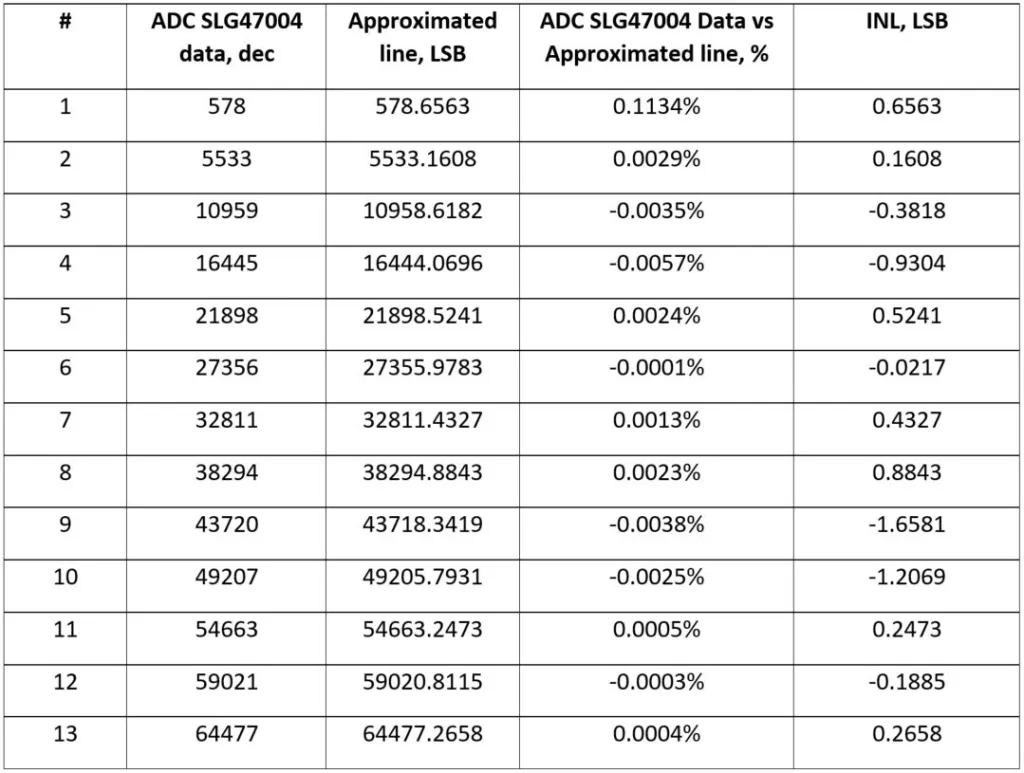

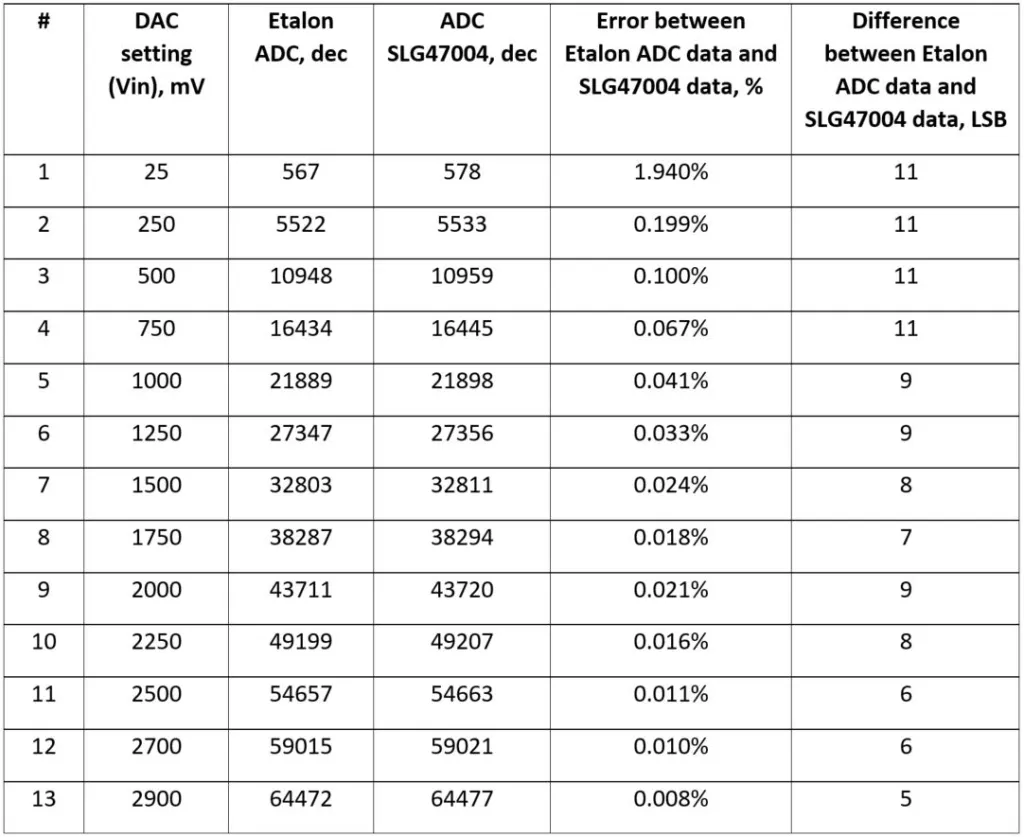

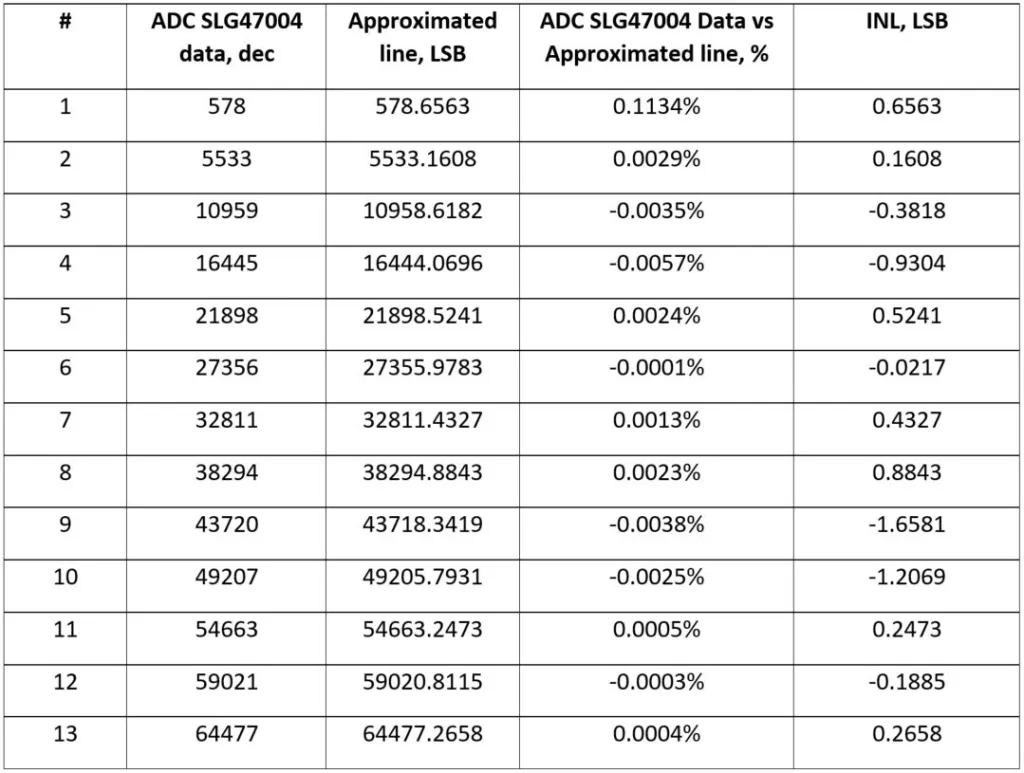

表1、表2和图7显示了比较结果。

表 1数据显示了外部 Etalon ADC 和基于 SLG47004 的 ΣΔ ADC 的结果比较。资料瑞萨电子

查看 Σ-Δ ADC 器件的三种方法

表 2数据突出显示了基于 SLG47004 的 ΣΔ ADC 的线性评估。资料瑞萨电子

图 7该图突出显示了 Etalon ADC 与基于 SLG47004 的 ΣΔ ADC 的比较。资料瑞萨电子

基于 SLG47004 的 ΣΔ ADC 具有稳健的线性度(值 1.7 LSB)、良好的噪声容限(一系列样本的结果偏差为 2 LSB)以及较小的增益误差(满量程的 0.009%)和偏移误差(0.5 mV) 。值得注意的是,基于 SLG47004 的 ADC 未经过校准,因此 ADC 的性能可能因芯片而异,并且可能比上面显示的更差。为了提高性能,可以使用变阻器分压器(Opamp0 V参考源)(图 4)。校准过程是调整 Opamp0 的 V ref分压器输出,以在输入电压 V in = ADC_V ref /2 时化 SLG47004 数据和 Etalon ADC 数据之间的差异。

拟议的 ΣΔ ADC 可用作独立的 16 位 ADC,或与 SLG47004 混合信号 IC 内的其他模拟设计结合使用。实现 ADC 所需的内部资源包括 1 个

运算放大器、1 个 ACMP、1 个 GPIO 以及一些由振荡器提供时钟的逻辑组件。所提出的 ΣΔ ADC 具有低采样率 (1.95 sps),但具有良好的精度特性(0.5 mV 偏移误差、0.009% 增益误差和 2 LSB INL)以及良好的抗噪性。

图 3 ΣΔ ADC 的简化结构基于 SLG47004 可配置混合信号 IC。资料瑞萨电子

图 3 ΣΔ ADC 的简化结构基于 SLG47004 可配置混合信号 IC。资料瑞萨电子 图4数字变阻器的可选连接调整Opamp0的参考电压。资料瑞萨电子

图4数字变阻器的可选连接调整Opamp0的参考电压。资料瑞萨电子

图 6 V in =1.0 V 相当于 ADC_V ref =V dd =3.0 V的硬件原型波形。Renesas

图 6 V in =1.0 V 相当于 ADC_V ref =V dd =3.0 V的硬件原型波形。Renesas

图 7该图突出显示了 Etalon ADC 与基于 SLG47004 的 ΣΔ ADC 的比较。资料瑞萨电子

图 7该图突出显示了 Etalon ADC 与基于 SLG47004 的 ΣΔ ADC 的比较。资料瑞萨电子