它采用普通 PWM 信号与其交流耦合逆信号的无源求和,从而显着衰减不需要的交流(纹波)分量,而不影响所需的直流分量。

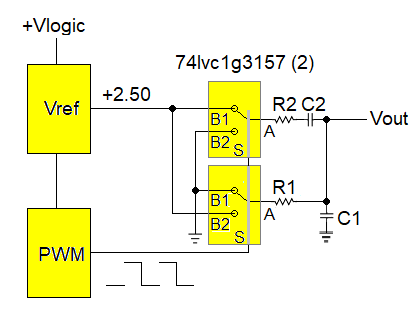

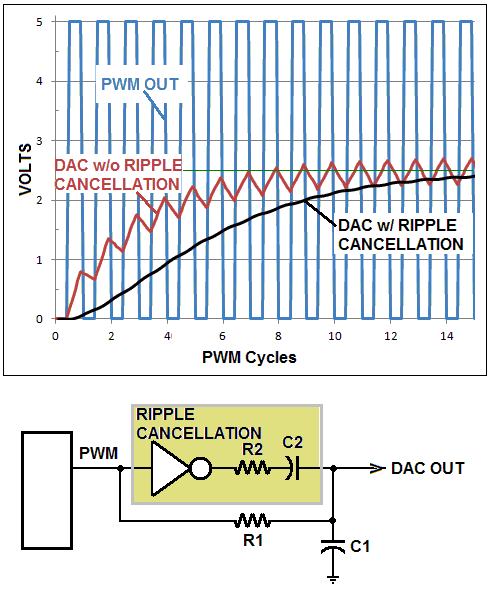

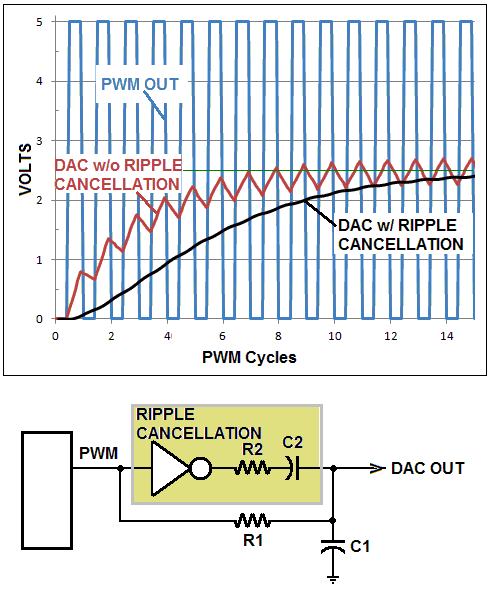

几年前,我发表了一个设计理念(参见图 1:“通过模拟减法消除 PWM DAC 纹波”, 2017 年 11 月 28 日),展示了消除 PWM 输出纹波的简单技巧。它采用普通 PWM 信号与其交流耦合逆信号的无源求和,从而显着衰减不需要的交流(纹波)分量,而不影响所需的直流分量。

图 1通过模拟减法消除 PWM DAC 纹波。 其中一项TAoE改进解决了这样一个事实:PWM DAC 精度往往受到对数字逻辑

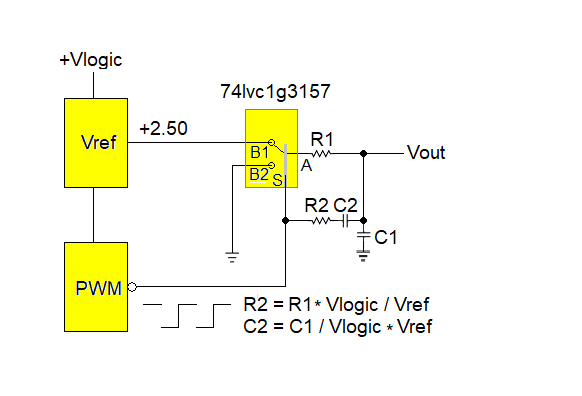

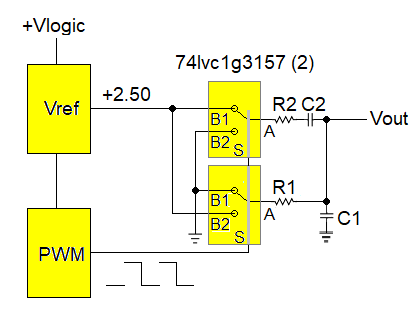

电源的依赖的限制,正如 H&H 恰当地指出的那样,数字逻辑电源“非常不准确”。他们巧妙的解决方案(参见图 2)是在常用的 PWM 拓扑中添加精密模拟

开关和的电压基准,从而将 DAC 输出与逻辑电源不准确的情况隔离开来。一个开关生成普通 PWM 波形的版本,而另一个开关则生成其相反波形。将后者的交流耦合分量添加到前者的直流分量中,执行纹波消除模拟减法,如我 2015 年设计理念 (DI) 中所述。

图2 TAoE PWM精度提升概念示意图

这当然是解决 PWM 精度问题的一种优雅、完美可行且有效的解决方案。

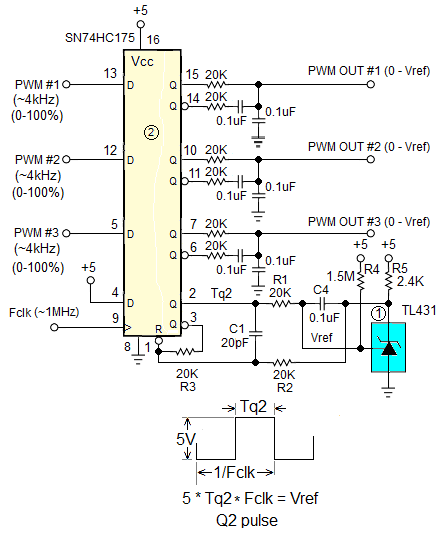

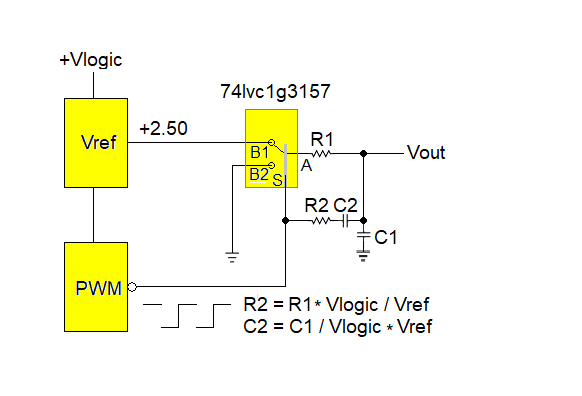

然而,由于每个 DAC 需要两个模拟开关封装,如果需要多个通道的 PWM DA 转换,封装数量可能会变得非常大。此外,随着通道数量的增加,Vref 上的总负载也会增加,这取决于所使用的参考器件,终可能会降低参考电压的精度。 因此,图 3中显示了图 2 的一个简单变体,其中 PWM 逻辑控制信号用于导出纹波消除信号,从而节省了模拟开关并减少了一半的 Vref 负载。这需要按系数 X = Vlogic/Vref 缩放 R2C2 纹波减去组件,当然,只有当 X 稳定时,该系数才能工作。另请注意,PWM 设置点必须为 1 补码 (VCC = -V – 1),这可以在软件中轻松完成。

图3 PWM逻辑信号用于纹波消除,从而节省了一个开关。

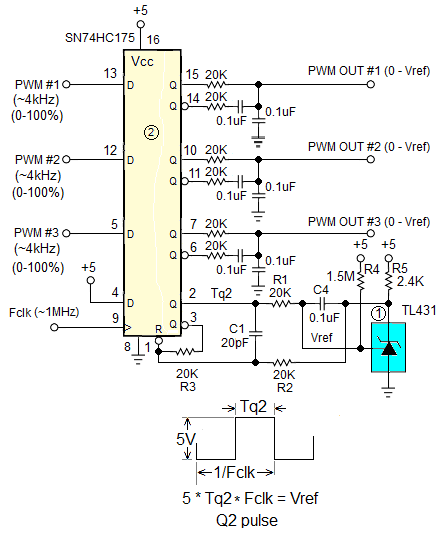

如果 Vlogic 不够稳定,图 3 无法正常工作,图 4显示了TAoE精度提升概念的另一种不同实现方式,它利用伺服脉冲面积(幅度 x 持续时间 x 频率)到参考电压的方法,如VFC 模数转换背景下近的另一个 DI所示。 图 4 Q2 脉冲区域伺服至参考电压。

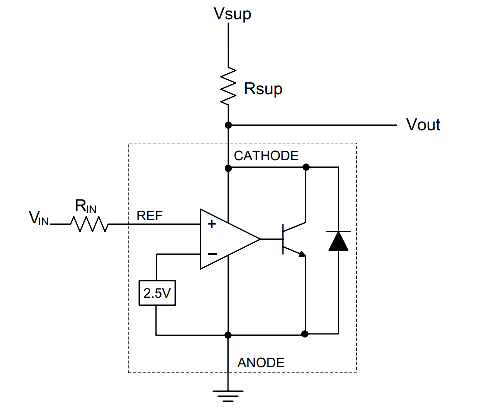

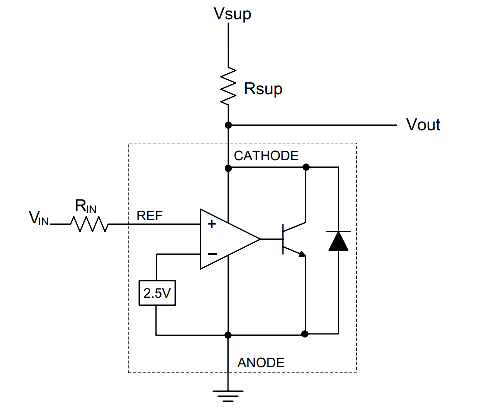

图 4 依赖于 TL431 等可调电压基准的能力来充当具有内置阈值的模拟比较器/积分器,如图5所示。

图 5 LT431 作为具有内置 Vref 的精密比较器/差分

放大器(来自 LT431 数据表)。

LT431 (U1) 将 U2 引脚 2 的平均差值与其内部 2.50V 参考电压进行积分,并通过在 Fclk x 脉冲持续时间 x 5V = 脉冲面积小于 2.5V 时增加 Q2 脉冲持续时间强制相等,并在大于 2.5V 时减少 Q2 脉冲持续时间。 R1C4 设置积分的时间常数,R4 为 U1 的输入偏置电流 (~1.8μA) 提供补偿,R5 为 U1 的输出提供上拉。

U2 固有的内部器件匹配(传播和转换时间等)使其他三位能够准确跟踪 U2 反馈环路内的触发器,从而为所有三个 PWM 通道提供准确的校准。关联的 RC 网络实现纹波消除,如果所有三个网络均已填充,则只需两个器件封装即可提供三个的 DAC。

几年前,我发表了一个设计理念(参见图 1:“通过模拟减法消除 PWM DAC 纹波”, 2017 年 11 月 28 日),展示了消除 PWM 输出纹波的简单技巧。它采用普通 PWM 信号与其交流耦合逆信号的无源求和,从而显着衰减不需要的交流(纹波)分量,而不影响所需的直流分量。

几年前,我发表了一个设计理念(参见图 1:“通过模拟减法消除 PWM DAC 纹波”, 2017 年 11 月 28 日),展示了消除 PWM 输出纹波的简单技巧。它采用普通 PWM 信号与其交流耦合逆信号的无源求和,从而显着衰减不需要的交流(纹波)分量,而不影响所需的直流分量。