与大多数数字和许多模拟过程的亚微米几何形状相关的小人尺寸导致电路运行速度更快。随着 IC 加速,大多数脉冲和函数

发生器的上升和下降时间(通常为 5 纳秒)不足以测量低于 20 纳秒的时间间隔。您可以使用模拟比较器或 CMOS 逻辑门来克服这一限制,从而创建更快的数字边缘。它们的上升和下降时间足够快,但信号电平仅包括地和 V CC。

设计人员也将高速数字电路使用的亚微米工艺应用于模拟

开关,因此这些开关的开启和关闭时间也会产生快速的上升和下降时间。此外,SPDT(单刀双掷)开关可以产生高电平和低电平可编程的脉冲。 模拟开关阻碍其用作脉冲发生器的一个特性是固有的内置延迟(先断后合时间),该延迟可保证 SPDT 开关在转换期间不会将两个开关

端子短路在一起。不幸的是,这种延迟和开关的有限开启时间也延长了上升和下降时间。您可以通过向电路添加动态上拉和动态下拉来避免这种影响(图 1)。足够低的上拉和下拉阻抗可以极大地改善相应的上升和下降时间。

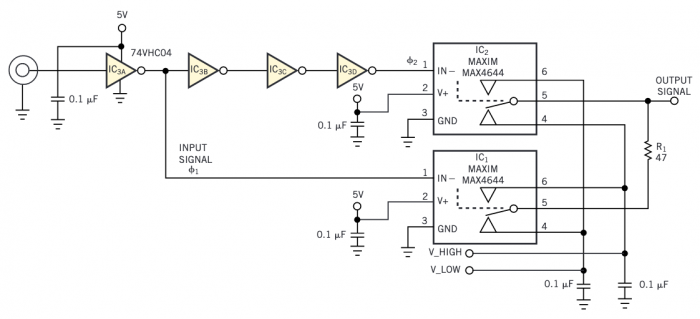

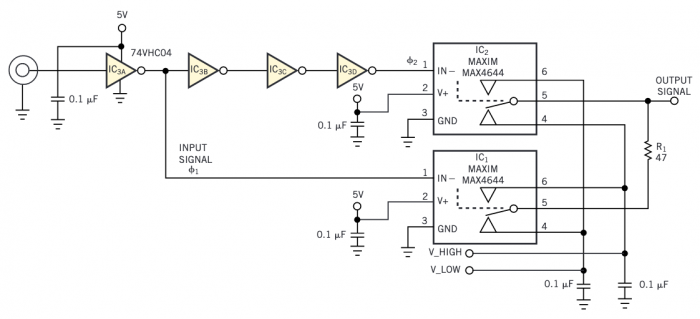

输入时钟信号 F 1控制 SPDT 模拟开关 IC 1,电路将其配置为上拉/下拉

驱动器。输入时钟信号还驱动高速CMOS反相器IC 3以产生延迟时钟信号F 2。延迟时钟驱动 SPDT 模拟开关 IC 2,电路将其配置为输出驱动器。

考虑稳态条件,其中 F 1较低且 F 2高。 IC 1的COM 引脚和IC 2的COM 引脚连接到V_LOW,F 1的上升沿导致IC 1将输出信号拉高。由于串联电阻R 1相对于MAX4644的导通电阻较大,即47W与2.5W典型值相比,因此对输出电压的直接影响很小。然而,当 F 1传播通过反相器串时,F 2的下降沿导致 IC 2从 V_LOW 转变为 V_HIGH。低阻抗上拉电阻 R 1的存在为信号转换提供驱动,随后 IC 2很快闭合。

C55输入信号为 5V 逻辑,输出摆幅为 1 至 2V(图 2)。您可以将 V_LOW 和 V_HIGH 设置为 IC 1和 IC 2

电源范围内的任意电平。该电路的静态电流基本上为零,仅在输出转换期间出现短暂的峰值。输出的上升和下降时间约为 4 纳秒,输出阻抗为 2.5W。