由于 GaN 的高

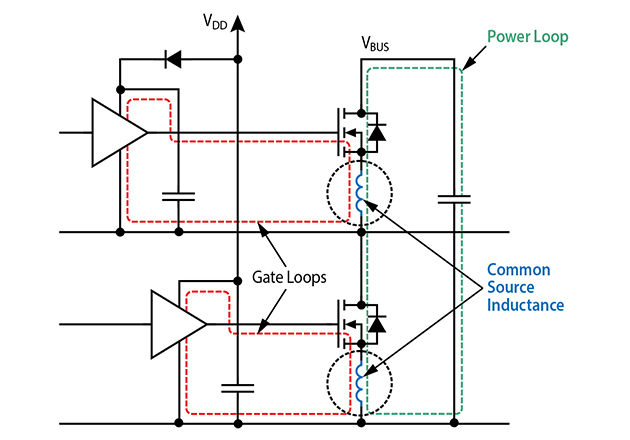

开关速度而导致的寄生电感 在比老化功率 MOSFET 更高的频率下使用 GaN,使功率转换电路中寄生电感的退化效应成为焦点 [1]。这种电感阻碍了 GaN 超快速开关能力的全部优势,减少了 EMI 的产生。对于大约 80% 的功率转换器中使用的半桥配置,寄生电感的两个主要来源是;(1) 由两个功率开关器件与高频母线

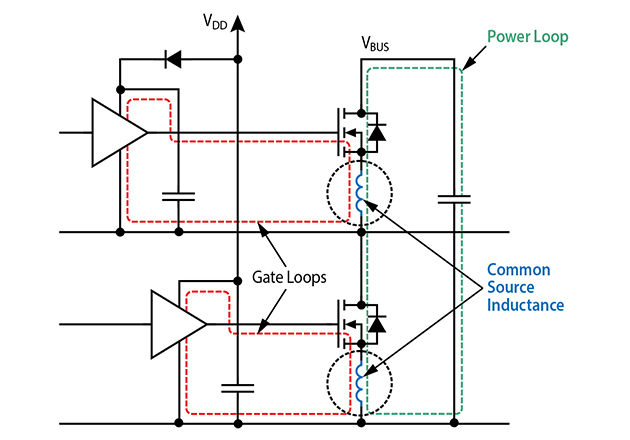

电容器形成的高频功率环路,以及 (2) 由栅极驱动器、功率器件和高频栅极驱动电容器形成的栅极驱动回路。共源极电感 (CSI) 由栅极环路和功率环路共用的环路电感部分定义。它由图 1 中的箭头表示。

半桥功率级原理图,显示功率和栅极驱动环路,公共源极电感以虚线圆圈显示

图 1:半桥功率级示意图,显示功率和栅极驱动回路,公共源极电感以虚线圆圈显示

化寄生电感

在考虑高速功率器件的布局时,化所有寄生电感至关重要。不可能平等地减少电感的所有分量,因此,必须按重要性顺序解决它们,从共源极电感开始,然后是功率回路电感,是栅极回路电感。

对于高压 PQFN(功率四方扁平无引线)MOSFET 封装,需要一个单独的栅极返回源极引脚是众所周知的,高压 GaN PQFN 结构也实现了这种引脚 [2,3]。当这些单独的引脚可用时,栅极驱动回路和电源回路在封装内是分开的,必须格外小心它们的外部连接方式。

共源极电感的降低是以牺牲被推到栅极环路之外的外部源极电感为代价的。一旦去除公共源极电感,这种外部电感会导致接地反弹增加,因为器件的速度会提高 [4]。

增强型 GaN

晶体管采用晶圆级芯片级封装 (WLCSP),

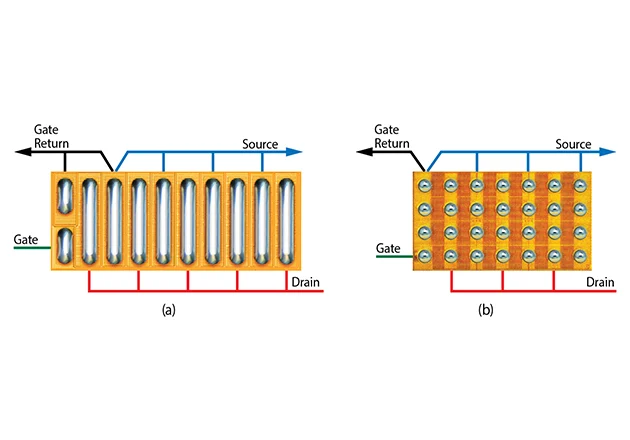

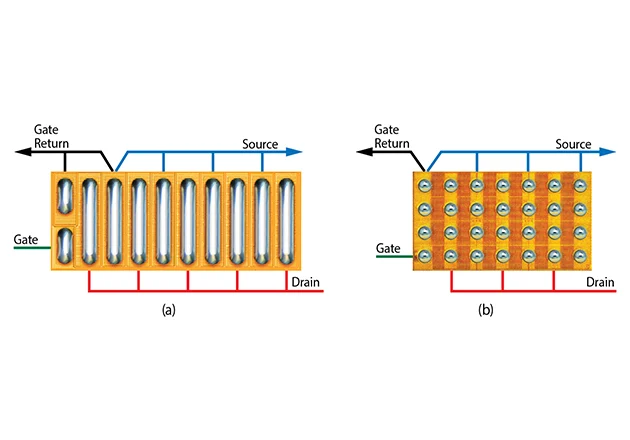

端子采用基板栅格阵列 (LGA) 或球栅阵列 (BGA) 格式。其中一些器件不提供单独的栅极返回源极引脚,而是提供许多非常低的电感连接,如图 2 所示。这些封装的总封装电感通常小于 100 pH 值。这大大减少了电感的所有元件,从而减少了所有与电感相关的问题。这些 LGA 和 BGA 封装可以像提供专用栅极返回引脚或栅条的封装一样处理,方法是将靠近栅极的源焊盘分配为栅极环路和电源环路的“星形”连接点。然后,通过让电流沿相反或正交方向流动来分离栅极和功率环路的布局,如图 2 所示。 LGA (a) 和 BGA (b) 格式的 GaN 晶体管,显示器件电流的方向,使共源电感

图 2:LGA (a) 和 BGA (b) 格式的 GaN 晶体管,显示了使共源电感化的器件电流方向

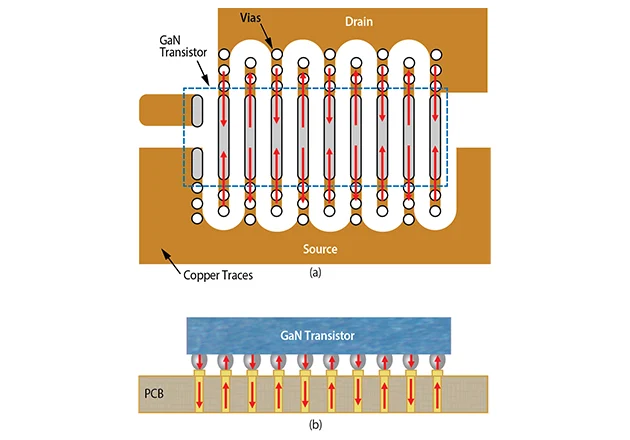

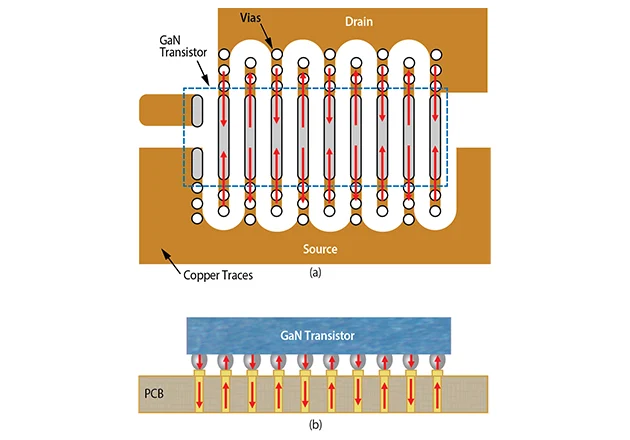

虽然化构成环路的各个元件(即电容器 ESL、器件引线电感和 PCB 互连电感)的电感很重要,但设计人员还必须专注于化总环路电感。由于环路的电感由内部存储的磁能决定,因此可以通过利用相邻导体之间的耦合来感应磁场自抵消,从而进一步降低整体环路电感。 通过将漏极和源极交错在器件的一侧,会产生许多电流相反的小回路,这些回路将通过磁场自抵消来降低总电感。这不仅适用于图 3(a) 所示的 PCB 走线,也适用于图 3(b) 所示的垂直焊接连接和层间连接通孔。随着多个小磁场抵消环的形成,总磁能和电感显着降低 [5]。

安装在 PCB 上的 LGA GaN 晶体管,显示交流电流 (a) 俯视图 (b) 侧视图

图 3:安装在 PCB 上的 LGA GaN 晶体管,显示交流电流 (a) 顶视图 (b) 侧视图

通过将器件两侧的漏极电流和源电流从中心线引出并复制磁场抵消效应,可以进一步降低部分环路电感。其工作原理是减少每个导体中的电流,从而进一步减少存储的能量,并且较短的电流路径会产生较低的电感。

传统功率环路设计

为了了解如何在实际布局中实现功率环路电感化,提出了两种传统的功率环路方法进行比较。这两种方法将分别称为 “横向” 和 “垂直”。

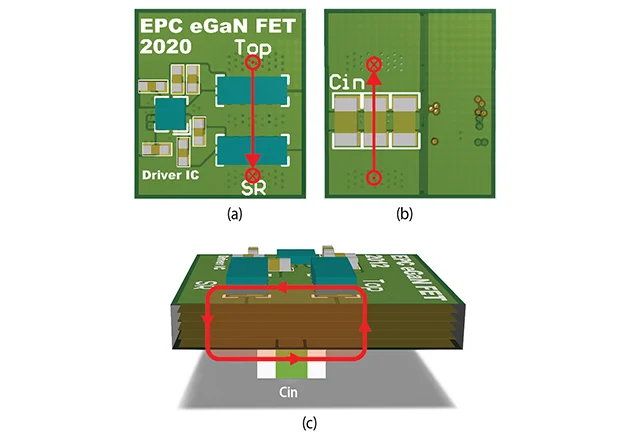

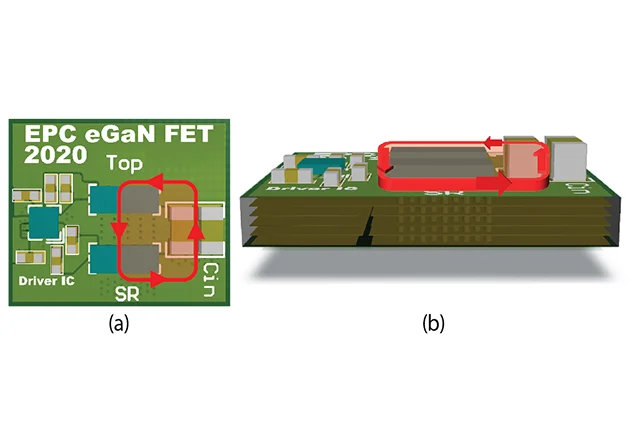

横向电源回路设计 横向布局将输入电容器和器件放置在 PCB 的同一侧,以限度地减少高频电源环路的面积。此设计的高频环路包含在 PCB 的同一侧,被视为横向电源环路,因为电源环路在单个 PCB 层上横向流动。图 4 显示了使用 LGA 晶体管设计的横向布局示例。此图中突出显示了高频 loop。

基于 LGA GaN 晶体管的转换器的传统横向功率环路:(a) 顶视图 (b) 侧视图

图 4:基于 LGA GaN 晶体管的转换器的传统横向电源环路:(a) 顶视图 (b) 侧视图

虽然化环路的物理尺寸对于降低寄生电感很重要,但内层的设计也至关重要。对于横向电源环路设计,个内层用作“屏蔽层”。该层在屏蔽内部电路免受高频功率环路产生的磁场的影响方面起着关键作用。电源环路产生一个磁场,在屏蔽层中感应出电流,该电流沿与电源环路相反的方向流动。屏蔽层中的电流产生磁场以抵消原始电源回路的磁场。终结果是磁场的抵消,转化为寄生功率环路电感的降低。

在功率环路附近有一个完整的屏蔽层,可为横向布局产生的功率环路电感。这种方法在很大程度上取决于从电源回路到内层中包含的屏蔽层的距离 [6]。只要顶部两层非常接近,高频环路电感对电路板总厚度的依赖性就很小。

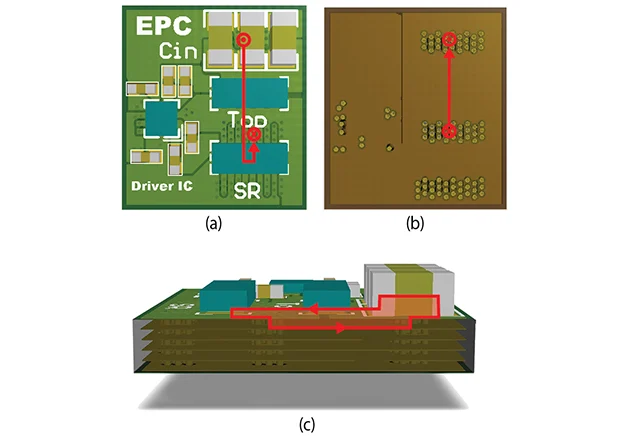

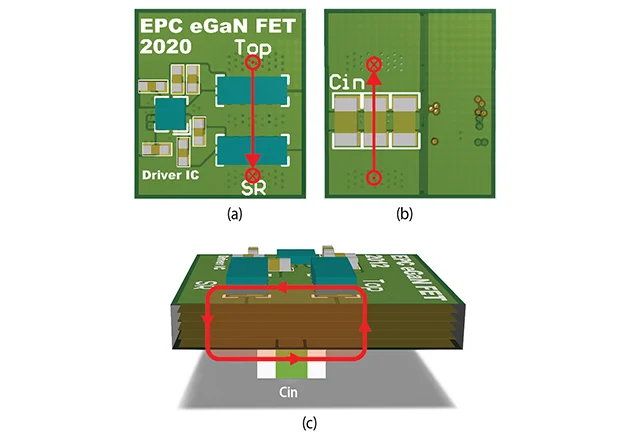

垂直电源回路设计 第二种传统布局如图 5 所示,将输入电容和晶体管放在 PCB 的相对两侧,电容位于器件正下方,以限度地减小物理环路尺寸。这称为垂直电源回路,因为回路使用过孔通过 PCB 垂直连接。图 5 的 LGA 晶体管设计突出显示了垂直功率环路。

基于 LGA 晶体管的转换器的传统垂直电源回路:(a) 顶视图 (b) 底视图 (c) 侧视图

图 5:基于 LGA 晶体管的转换器的传统垂直电源回路:(a) 顶视图 (b) 底视图 (c) 侧视图

对于此设计,由于其垂直结构,没有屏蔽层。垂直功率环路使用磁场自抵消方法(电流沿相反方向流动)来降低电感,而不是使用屏蔽层。

对于 PCB 布局,板厚通常比板顶部和底部走线的水平长度细得多。随着电路板厚度的减小,与横向电源环路相比,环路的面积显着缩小,并且顶层和底层沿相反方向流动的电流开始提供磁场自抵消。为了使垂直电源回路有效,必须尽量减少电路板厚度。

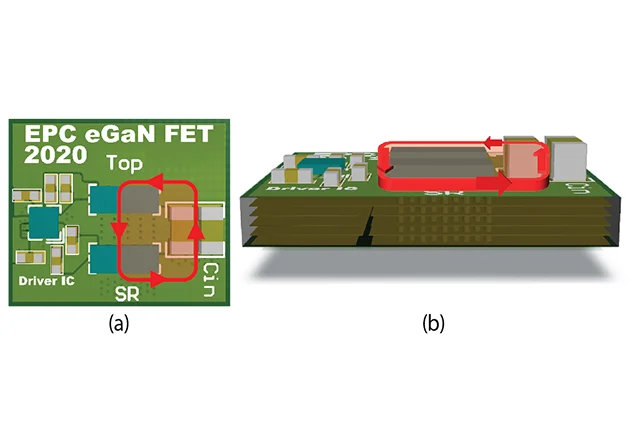

图 6 显示了一种改进的布局技术,该技术具有减小环路尺寸、具有磁场自抵消、电感与电路板厚度无关、单面元件 PCB 设计以及为多层结构提供高效率等优点。该设计利用图 6(b) 所示的内层作为功率环路返回路径。该返回路径位于顶层电源环路的正下方,如图 6(a) 所示。这种定位实现了的物理环路面积和磁场自抵消。侧视图如图 6(c) 所示,说明了在多层 PCB 结构中创建薄型磁场自抵消回路的概念。 基于 LGA 晶体管的转换器的功率环路:(a) 顶视图 (b) 内层 1 的顶视图 (c) 侧视图

图 6:基于 LGA 晶体管的转换器的功率环路:(a) 顶视图 (b) 内层 1 的顶视图 (c) 侧视图

这种改进的布局将输入电容器放置在靠近顶部器件的位置,正输入电压端子位于顶部晶体管的漏极连接旁边。GaN 器件位于横向和垂直功率环路外壳的布置中。交错式电感节点和接地通孔在同步整流器晶体管的底部重复。

这些交错过孔具有三个优点: ? 通孔与反向流动的电流交错减少了磁能存储,并有助于产生磁场抵消。这减少了涡流和邻近效应,从而降低了交流传导损耗。? 位于下部晶体管下方的通孔可降低晶体管续流期间的电阻和伴随的导通损耗。? 通孔降低了热扩散电阻,从而提高了效率和功率处理能力。

表 1 比较了传统设计和设计的特性。横向回路 垂直回路 回路 单面PCB能力 是 否 是 磁场自抵消 否 是 电感与电路板厚度无关 是 否 是否需要屏蔽层 是 否 否 表1:传统和功率回路设计的特性

集成对寄生参数的影响

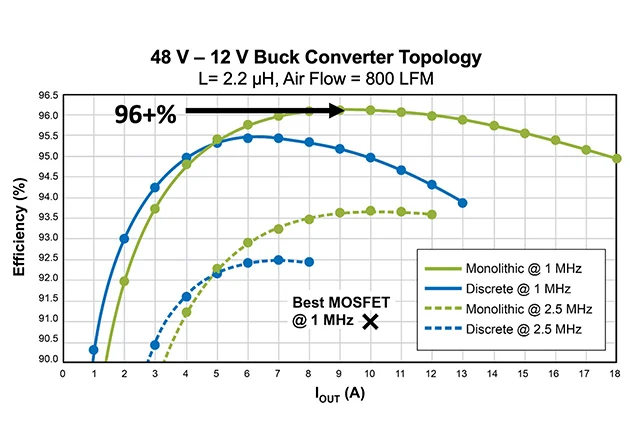

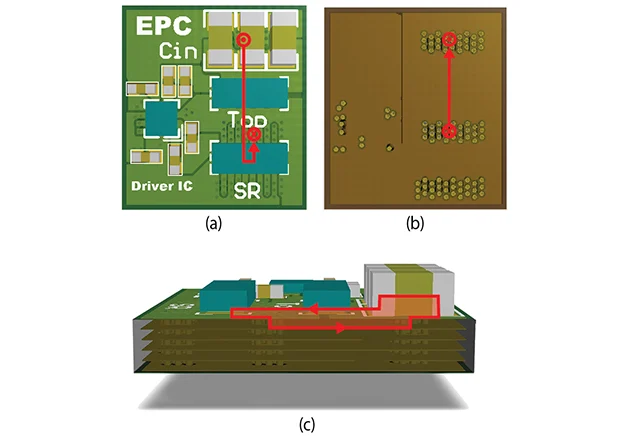

为了进一步降低基于 GaN 晶体管的设计的寄生电感,可以使用单片 GaN 功率级

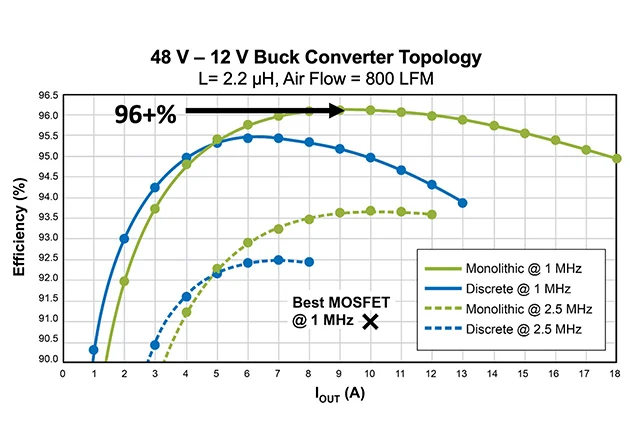

集成电路 [7]。在图 7 中,显示了单片功率级 GaN IC 的框图和实际芯片照片。将这种单片集成电路(如图 8 所示)的实验测量效率与使用具有相同导通电阻的 eGaN? 晶体管的分立电路进行了比较,并由 uPI Semiconductor uP1966 Si 半桥驱动器 IC [7] 在布局中驱动。GaN IC 中降低功率环路和栅极环路电感的优势变得显而易见,因为在标准降压转换器中,在 1 MHz 时,集成的整体效率增益非常明显。 单片功率级框图 (a) 和芯片照片 (b)

图 7:单片功率级框图 (a) 和芯片照片 (b) 在 48 V – 12 V 降压转换器中,在 1 MHz(实线)和 2.5 MHz(虚线)下,单片 GaN 功率级(绿色)和外部驱动的等效分立 GaN 晶体管(蓝色)解决方案之间的效率比较。黑色“X”是 1 MHz 时的 MOSFET 性能。

图 8:在 1 MHz(实线)和 2.5 MHz(虚线)下,48 V – 12 V 降压转换器中单片 GaN 功率级(绿色)和外部驱动的等效分立 GaN 晶体管(蓝色)解决方案的效率比较。黑色“X”是 1 MHz 时的 MOSFET 性能。

总结

高效的电路布局将限度地减少 PCB 面积,减少由于受寄生电感限制的较慢开关速度而导致的浪费性功率耗散,并通过减少电压过冲来提高系统可靠性。讨论了使用 GaN 晶体管时很重要的布局寄生效应;即共源电感、高频功率环路电感和栅极环路电感。