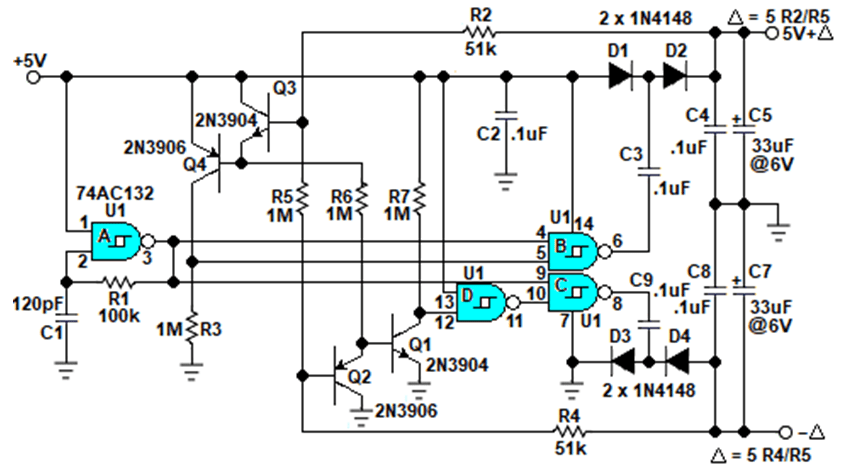

图 1 U1 是一个多极(例如,74AC04 六反相器)PMW 开关,其中运算放大器 A1 强制开关零状态以准确跟踪 0 = 零伏,运算放大器 A2 完成 1 = Vdd 的工作。

U1 引脚 5 与引脚 14 的连接会将引脚 6 驱动至逻辑 0,由 A1 引脚 6 感测。A1 引脚 7 与 U1 引脚 7 的连接会强制引脚 6 电压为零伏,从而当相关开关处于逻辑 0 时,强制任何 U1 输出为相同的零电平。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。