差分

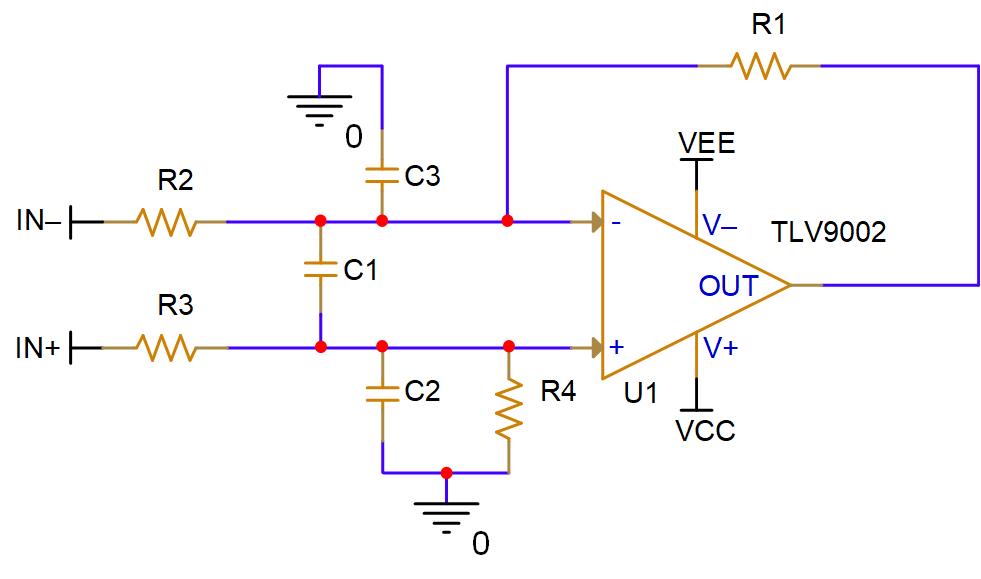

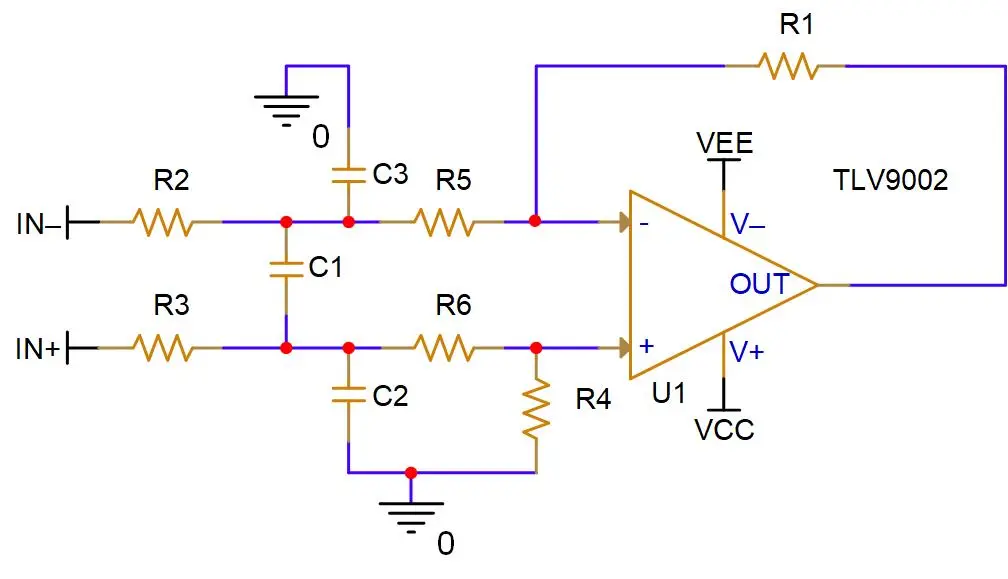

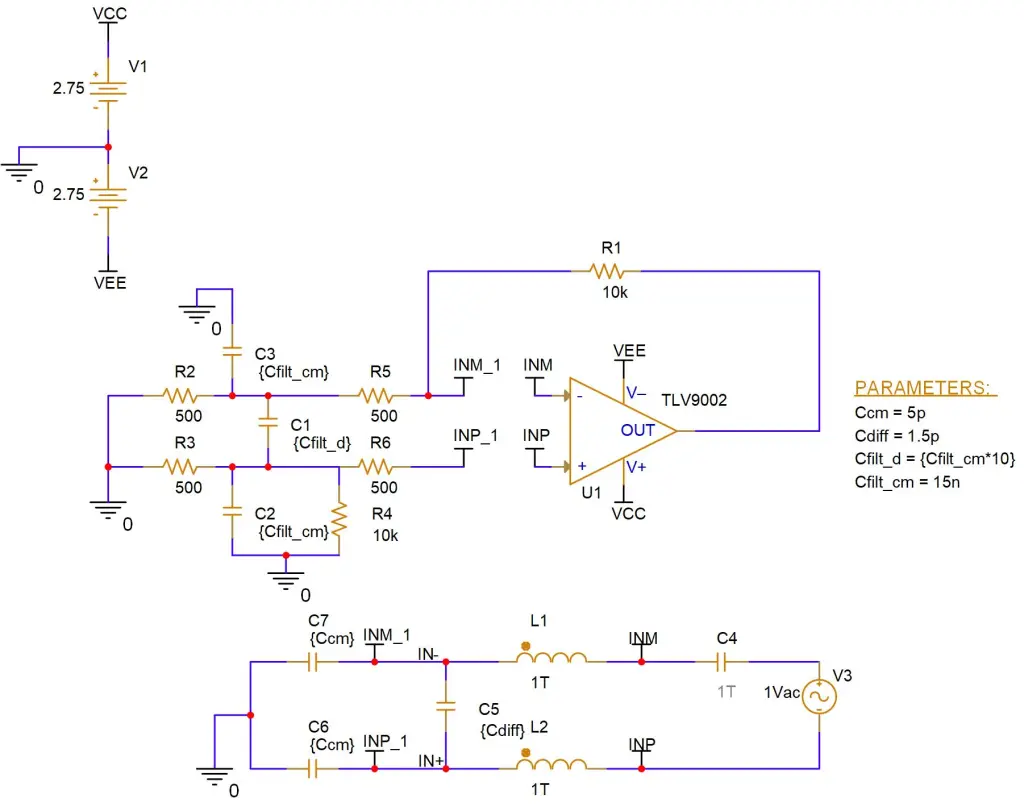

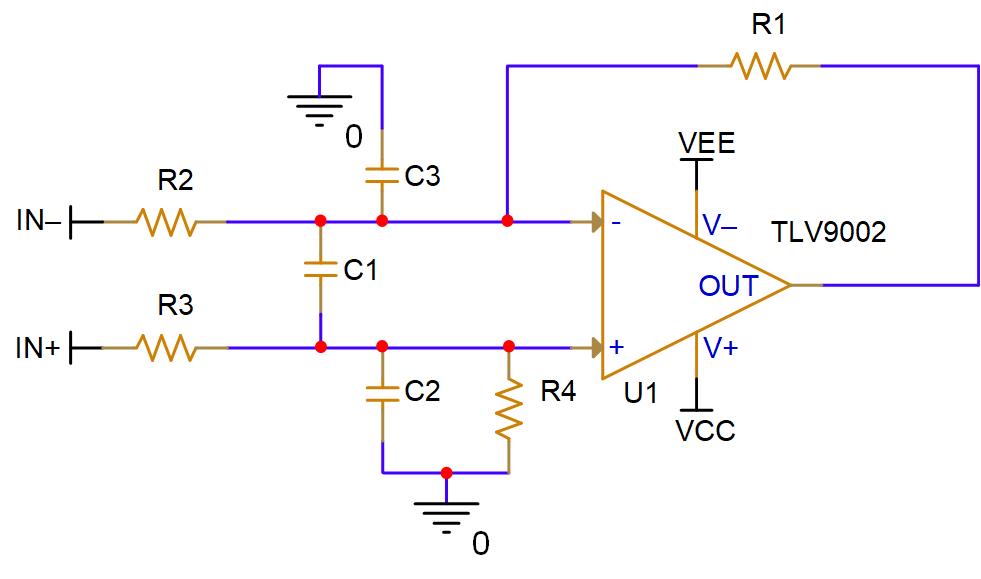

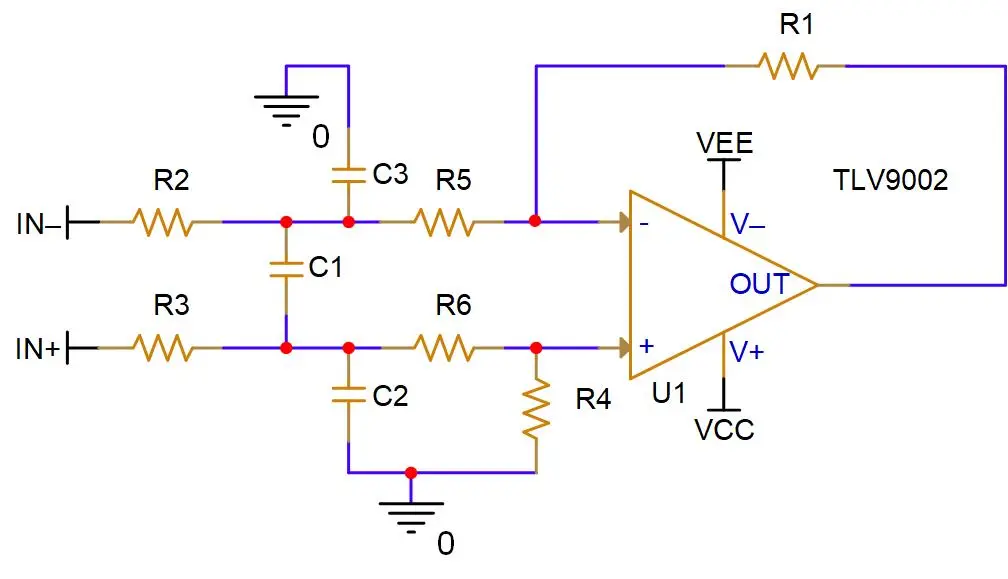

放大器是一种常见且有用的电路,广泛用于从工厂自动化到电动汽车系统等各种应用。这主要是因为它有助于在嘈杂环境中的设计中添加共模和差分滤波。 本文将比较两种离散差动放大器的滤波方法。如图1所示,实施方案 A 在传统系统中很常见,但可能存在一些设计缺陷。如图2所示,实施方案 B 进行了改进,可降低实施方案 A 中常见的放大器电路错误可能性。但为什么需要进行这种改进?如图 2 所示,所做的更改如何改善电路?

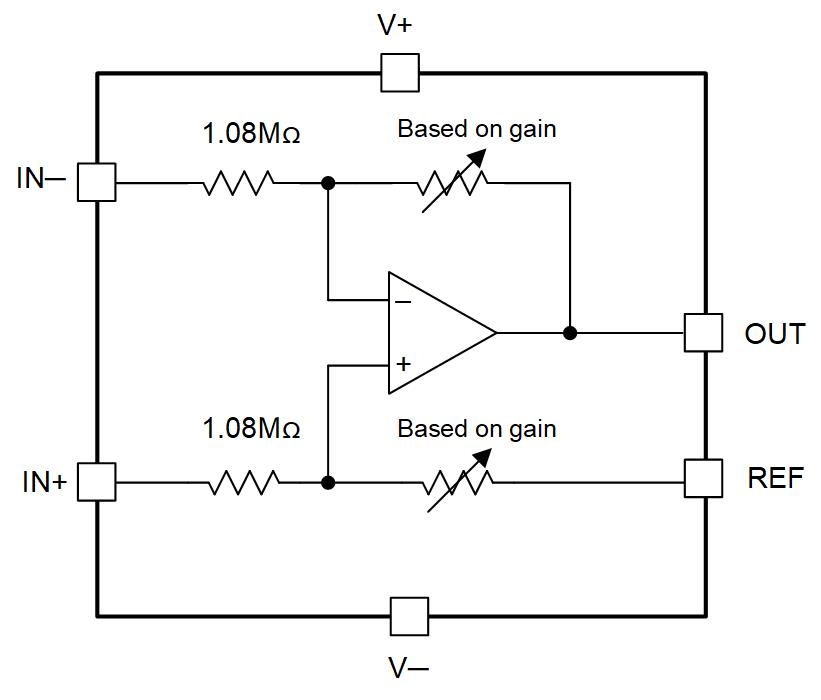

进一步了解分立差动放大器的实现 图 1

差分放大器实现 A 在传统系统中很常见。德州仪器进一步了解分立差动放大器的实现

图 2差分放大器实施方案 B 降低了实施方案 A 中出现错误的可能性。德州仪器首先,让我们快速回顾一下环路稳定性以及导致放大器电路不稳定的原因。影响运算放大器稳定性的主要因素有三个:

固有相移

外部相移

前两次转变的随机变化与工艺、温度和元件公差有关相位裕度表示在将随机和不可预测的变化应用于系统时设计的强度。本质上,放大器的反相反馈存在 180 度的相移,而放大器开环增益的主极点存在 90 度的相移。高频或非主极点会引入大约 20 到 40 度的相移,但根据设计的不同,可能会引入更多或更少的相移。

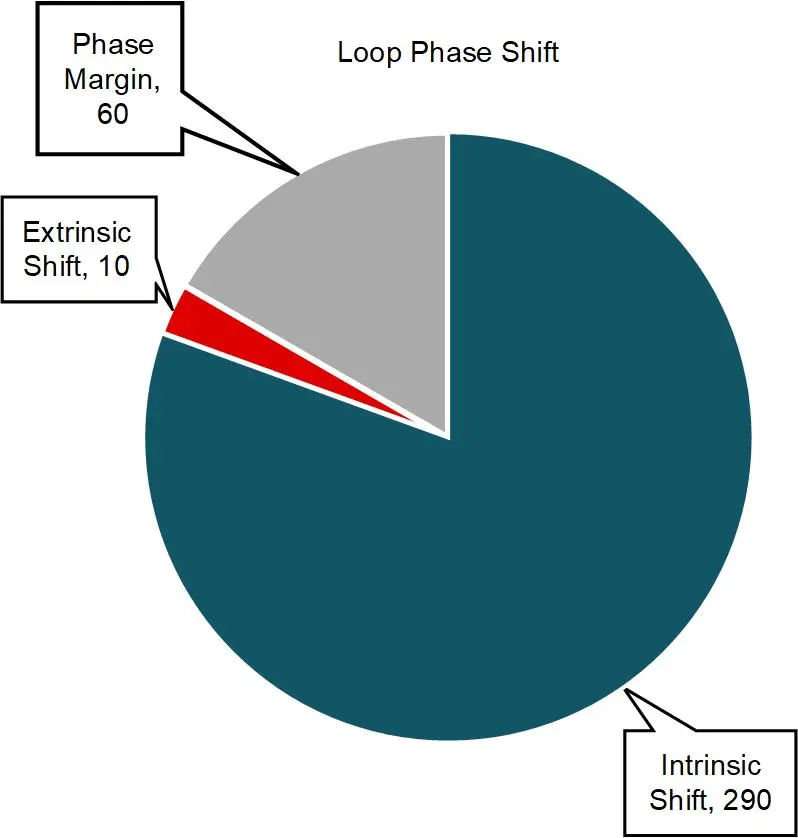

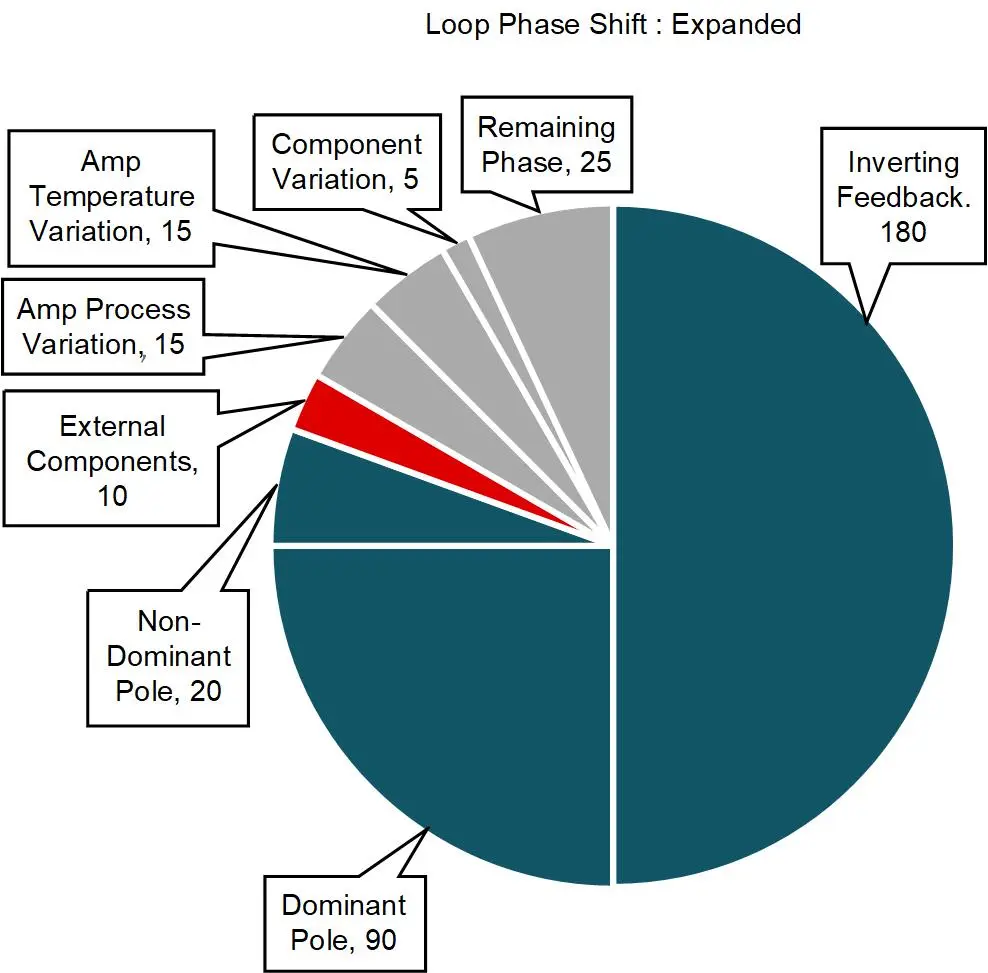

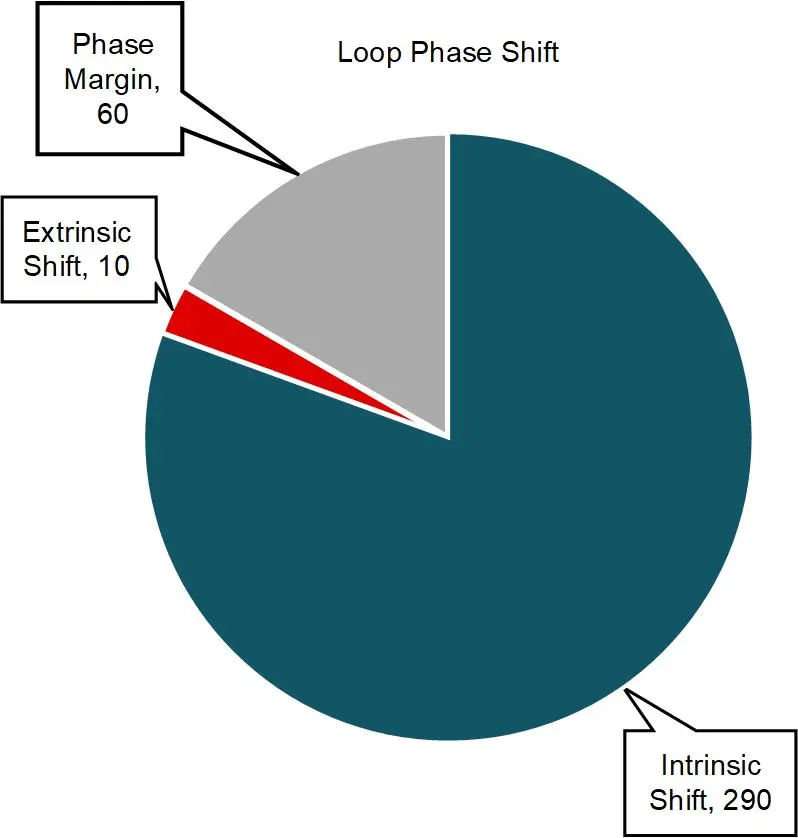

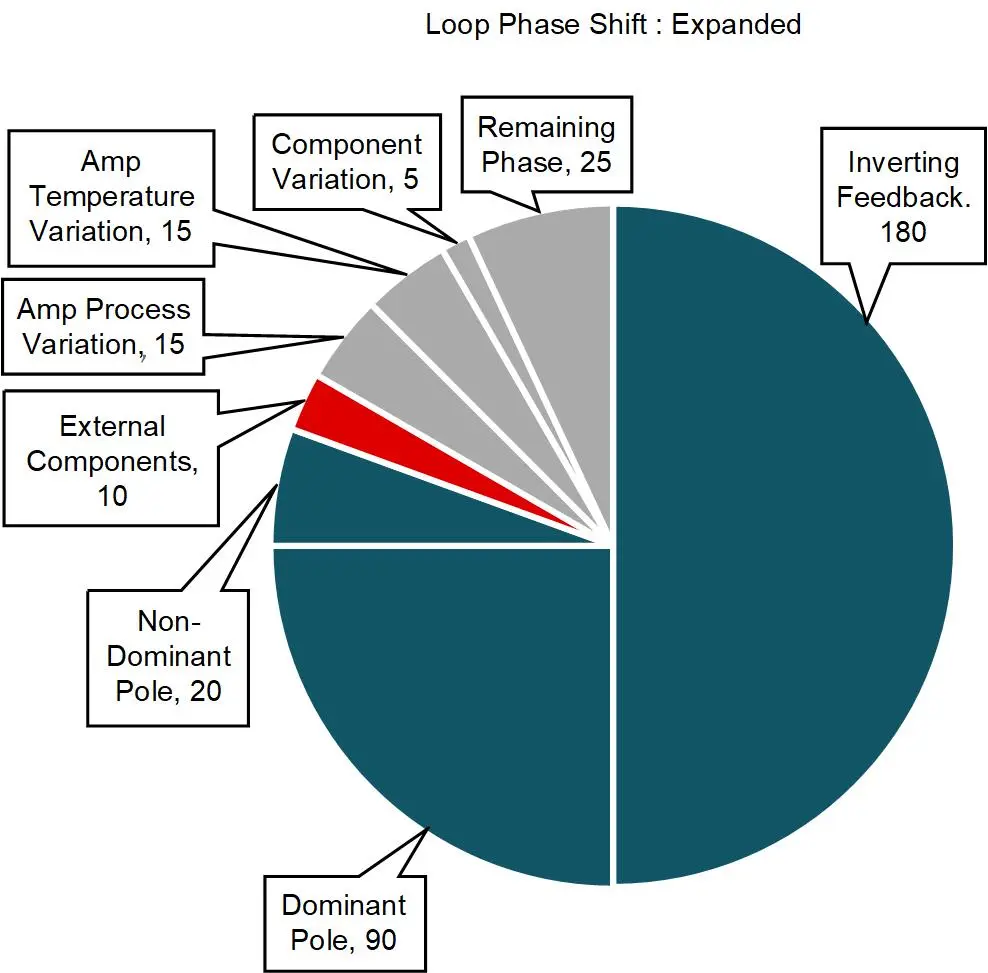

外部相移是反馈回路中的外部元件引入的相位滞后。 在工艺、温度和元件容差方面,非主极点和外部元件可能会引入不同程度的相移,这会使相位裕度不足的设计变得不稳定。图 3从高层次说明了环路稳定性的这种变化,而图 4则更详细地说明了这一点。

进一步了解分立差动放大器的实现 图 3环路相移显示高水平的稳定性。德州仪器进一步了解分立差动放大器的实现

图 4这是环路相移的扩展版本。德州仪器单位增益稳定放大器单位增益稳定放大器设计为在噪声增益(或非反相增益)为 1 的情况下用作缓冲器时保持稳定,并且随着增益的增加,相位裕度会更大。尽管差分放大器的额外增益可以增加相位裕度,但在反馈环路中添加更多外部电容负载可能会使放大器变得边缘稳定或完全不稳定。

在运算放大器的数据表中(图 5显示了一个示例),您可以看到有一个相位裕度的规范,但它是针对指定的负载电容器和负载电阻的。

进一步了解分立差动放大器的实现

图 5数据表显示了 LM2904B 运算放大器的相位裕度规格。德州仪器如果这些条件发生变化,相位裕度也会发生变化。随着电容负载的增加,负载电容与放大器的内部输出阻抗相互作用,在反馈环路中引入一个极点,从而引入相位滞后。

在方案 A 中,放大器的内部输出阻抗与反馈电阻串联,然后在反馈环路中形成电阻-电容 (RC) 延迟。与简单的输出电容负载相比,这会给反馈环路带来更大的相位滞后。 即使在实施 A 中只放置差分电容器 C1,您也可以看到小信号等效电路,该电路显示了增加的相位滞后。图 6是一个简单的近似值,但简化有助于理解一般行为。在这种情况下,由于非反相输入是直流值(在小信号分析中为接地),C1 现在成为接地到反馈环路的电容器,并且仍会通过引入相位滞后来降低环路稳定性。

进一步了解分立差动放大器的实现

图 6运算放大器的简单近似有助于理解一般行为。德州仪器以这种方式分析电路可以发现方案 A 的潜在危害之一。集成仪表放大器和集成差分放大器的差分和共模滤波的标准做法是方案 A。那么为什么添加这些电容不会对这些设备产生负面影响呢?原因是电容未放置在反馈环路中,因此不会给环路带来相位滞后。 三放大器仪表设备只有非反相输入端外部连接,因此在非反相输入端增加电容不会降低相位裕度。图 7显示了仪表放大器的内部原理图,从中可以看出在 +IN 或 –IN 上增加电容不会影响反馈环路。

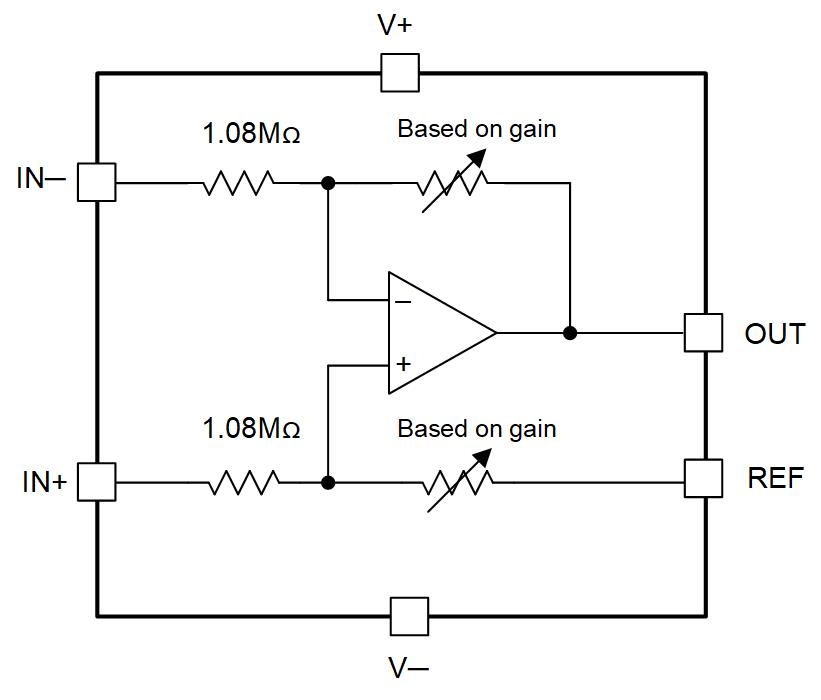

进一步了解分立差动放大器的实现 图 7简化的内部原理图展示了仪表放大器。德州仪器图 8显示了集成差分放大器的内部原理图。该集成差分放大器在输入电容和放大器的反相输入之间有一个电阻 (R IN ),用于将放大器(以及随后的反馈环路)与滤波电容引入的相位滞后隔离开来。

进一步了解分立差动放大器的实现

图 8简化的内部原理图展示了集成差分放大器。德州仪器同样的原理说明了实现 B 如何改进实现 A,如图 1 所示。

图 1 中的 R5 将反相输入与 C1 和 C3 引入的相位滞后隔离开来。即使这些电容值发生变化,该电阻也有助于保持环路的稳定性。如果 C1、C2 和 C3 的值足够小,则实现 A 不会总是变得不稳定。事实上,运算放大器中已经存在与这些相同的电容器。

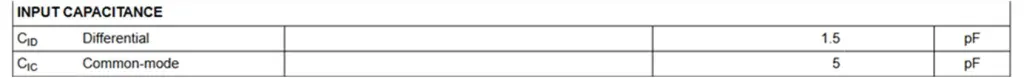

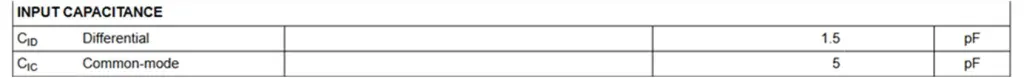

查看图 9中的 TLV9002 运算放大器的数据表,可以看到有一个 5 pF 差分电容和一个 1.5 pF 共模电容。这些不是故意放置的;然而,它们是存在于输入差分对栅极上的寄生电容。 进一步了解分立差动放大器的实现

图 9数据表显示了差分和共模电容的规格。资料德州仪器在运算放大器的输入端直接添加外部滤波电容,会增加与现有寄生电容并联的电容,并使其增大。这不一定会导致电路不稳定,但仍会对相位裕度产生负面影响。

滤波电容作用

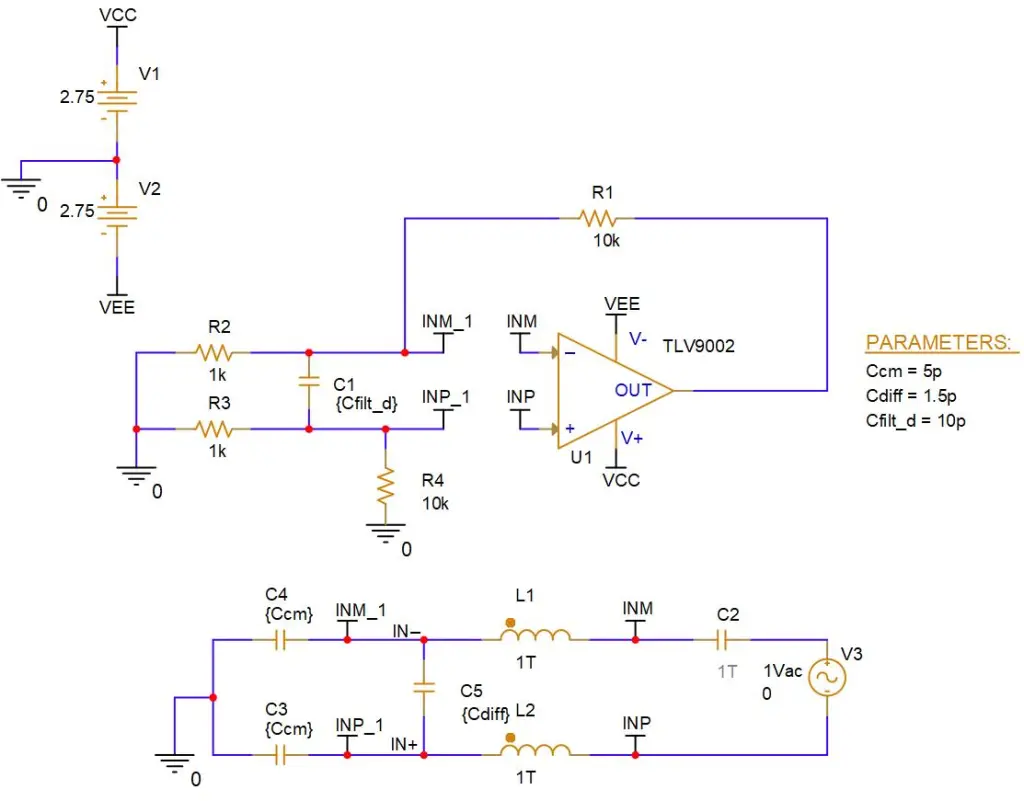

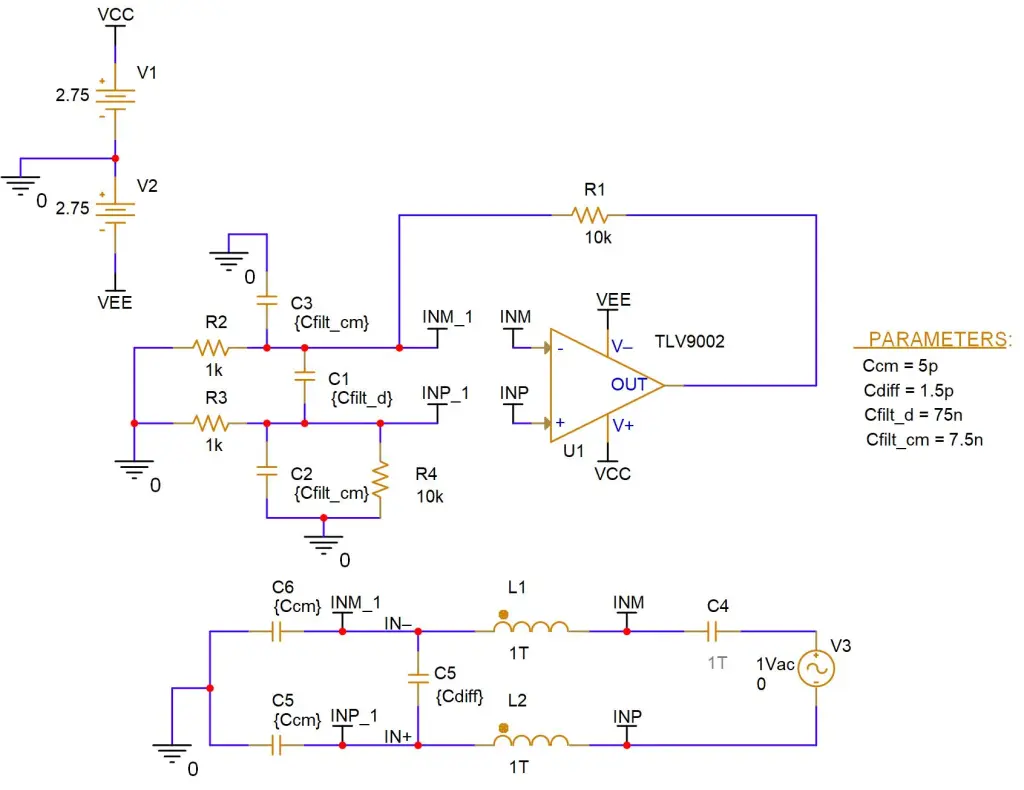

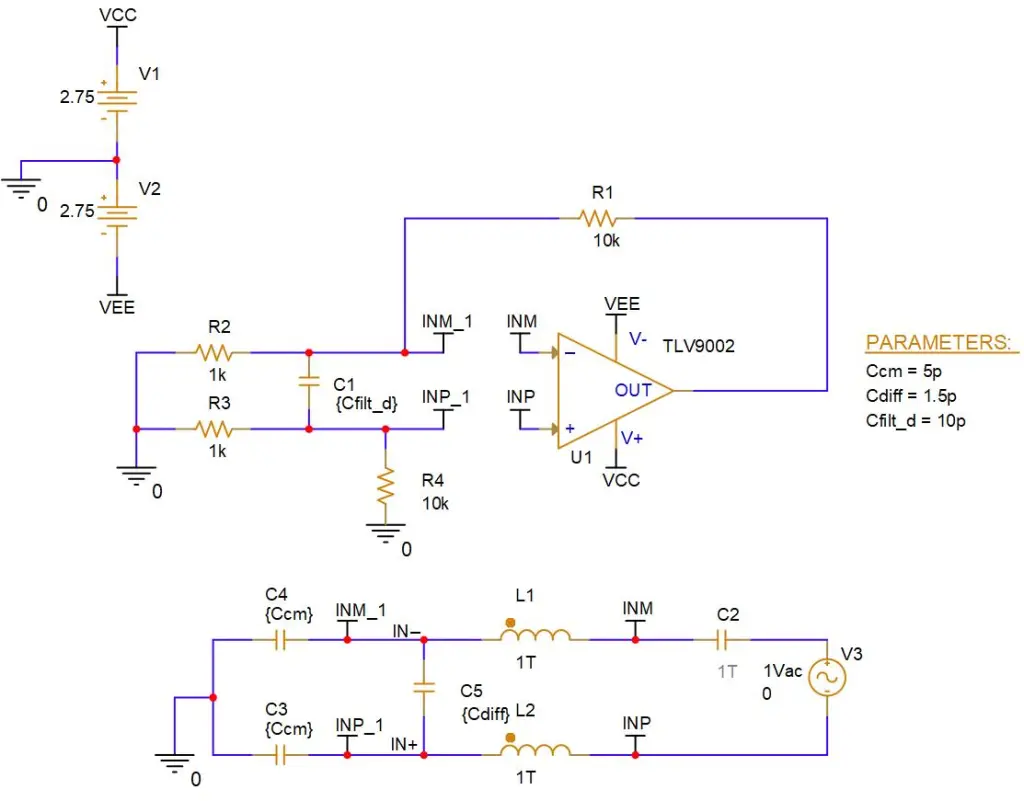

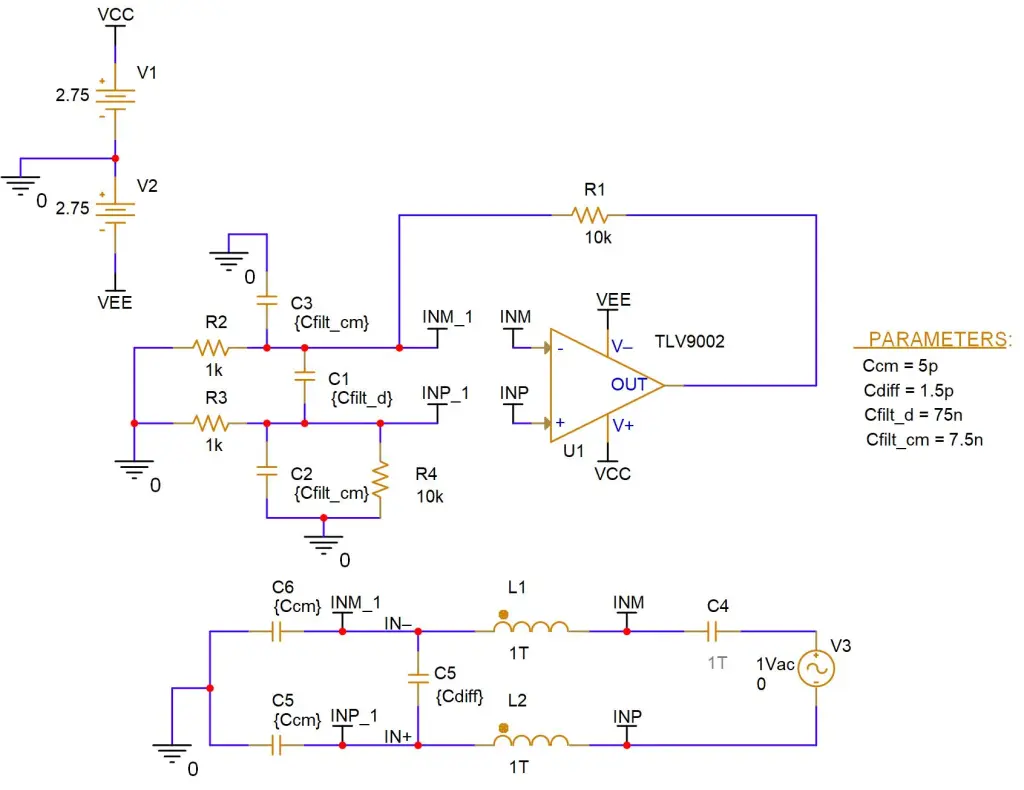

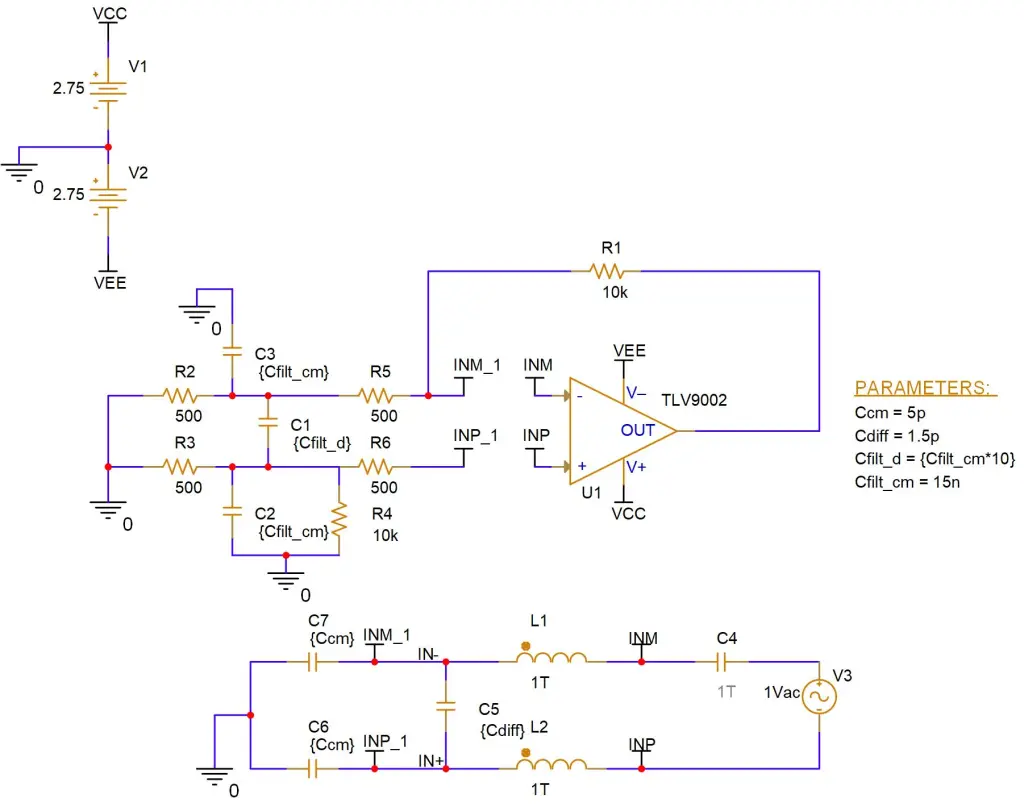

现在让我们检查滤波电容在多种实现中对电路相位裕度的影响。图 10显示了模拟电路。模拟是在 PSpice 中执行的。该项目可以帮助模拟许多不同放大器实现中的稳定性。 进一步了解分立差动放大器的实现

图 10 TI 的 PSpice 对差分输入电容器进行交流分析电路。德州仪器使用 PSpice for TI 中的 PARAM 块可以轻松为组件分配变量值。具有变量值的组件用花括号 {} 表示,并在 PARAMETERS: 语句下分配。

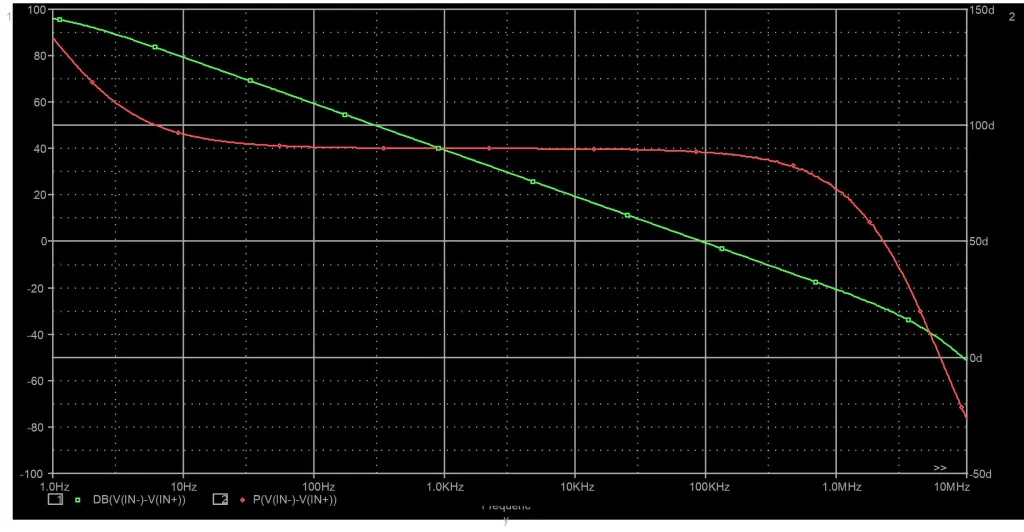

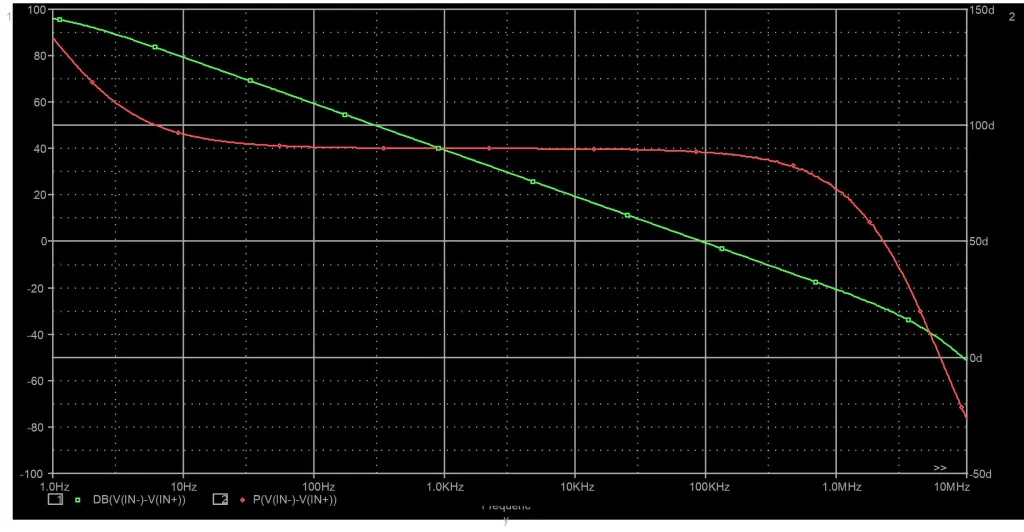

图 11和图 12显示了放大器反馈环路的波特图和反馈环路的相位裕度。当 Cfilt_d 较小(10 pF)时,该电路的相位裕度为 88 度,高于建议的 45 度相位裕度。换句话说,该电路是稳定的。

进一步了解分立差动放大器的实现 图 11显示了 10 pF 差分电容电路 (Cfilt_d = 10pF) 的波特图。德州仪器进一步了解分立差动放大器的实现.

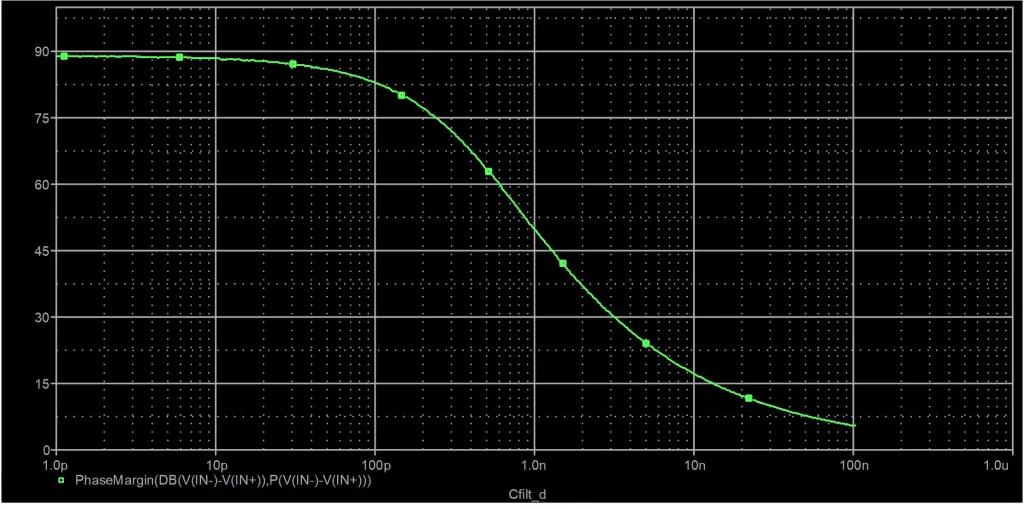

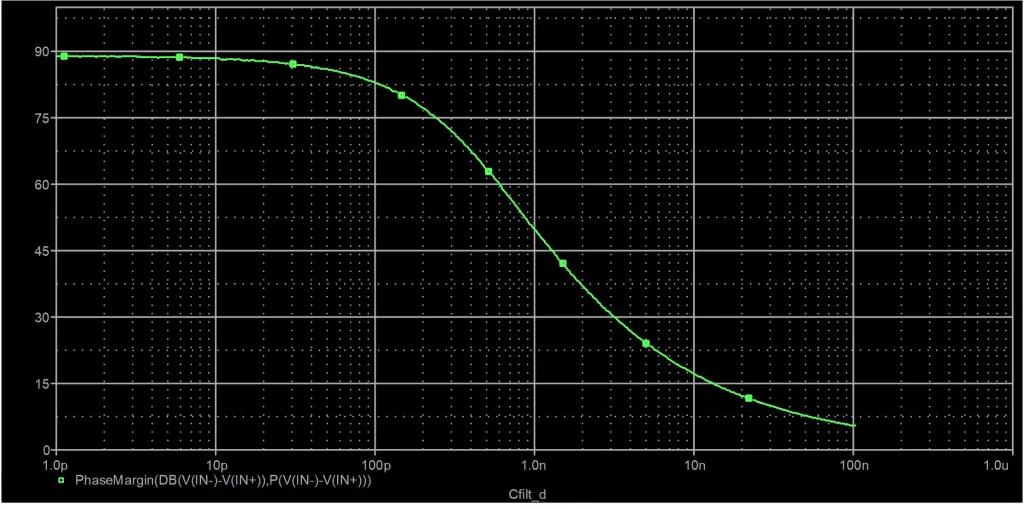

图 12这是图 10 所示电路的计算相位裕度。德州仪器图 13显示了当 Cfilt_d 从 1 pF 增加到 100 nF 时该电路的相位裕度。相位裕度大幅下降并渐近于 0。当输入端之间的电容约为 1 nF 时,该电路的相位裕度小于 45 度。

进一步了解分立差动放大器的实现

图 13曲线标记了差分滤波电容增加时相位裕度的参数分析。德州仪器伯德图和相位裕度现在,让我们分析一下图 14中配置的用于开环交流分析的实施方案 A,并测量得到的相位裕度。

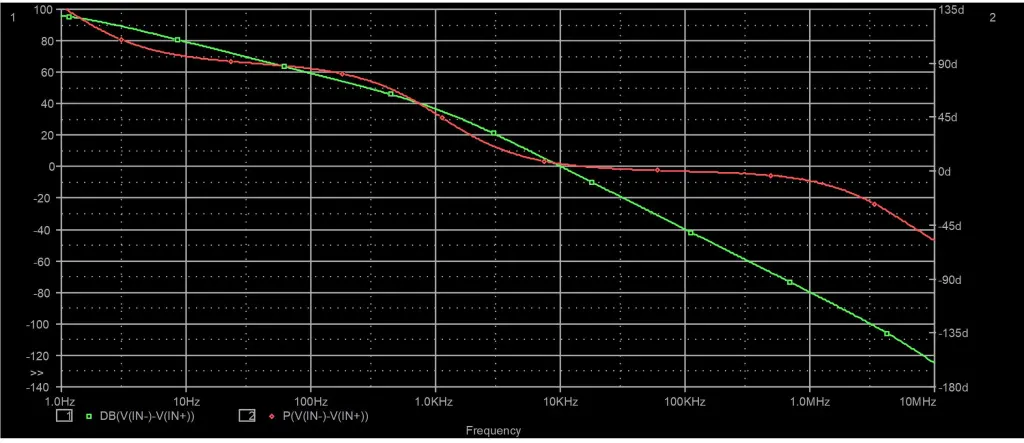

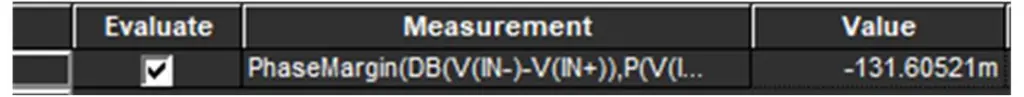

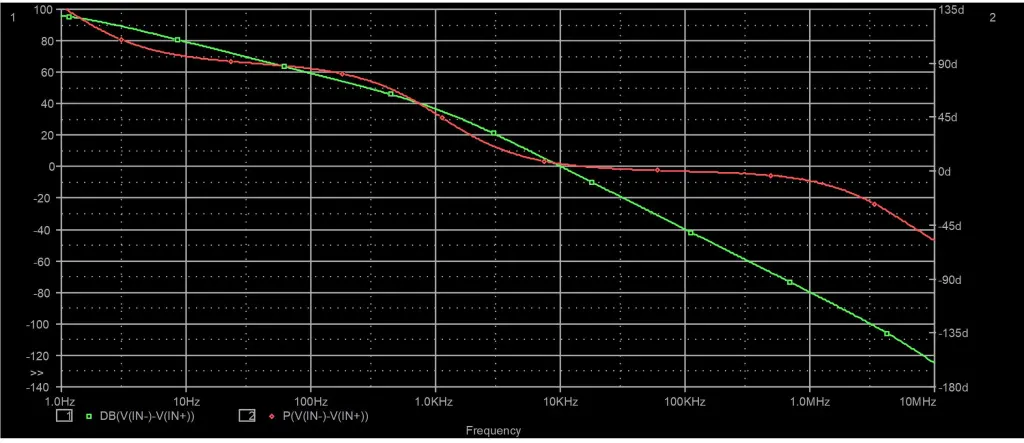

进一步了解分立差动放大器的实现 图 14显示了差分放大器实现 A 的 PSpice 原理图。德州仪器图 15和图 16显示了反馈环路的波特图和计算出的相位裕度。

进一步了解分立差动放大器的实现

图 15显示了图 14 的 Bode 图。德州仪器进一步了解分立差动放大器的实现

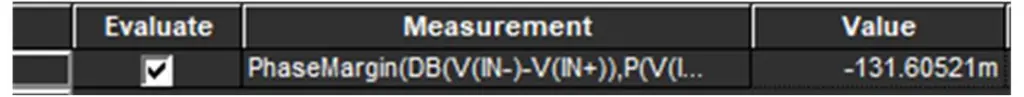

图 16计算出的相位裕度如图 15 中的波特图所示。德州仪器方案 A 具有 75 nF 差分电容和 7.5 nF 共模电容,相位裕度为 –0.131 度,不稳定。若要在方案 B 中创建等效电路,必须将 R2 和 R3 分成两半(分成 R2 和 R8,以及 R3 和 R9),并将 Cfilt_cm 和 Cfilt_d 加倍。将电阻值减半并将电容加倍可保持电路增益,同时将滤波器截止频率保持在相同频率。

图 17使用实现 B 来保留实现 A 的功能。

进一步了解分立差动放大器的实现

图 17显示了差分放大器实现 B 的 PSpice for TI 原理图。德州仪器实施方案 B 具有一个 15 nF 的共模滤波电容和一个比共模电容大 10 倍(即 150 nF)的差分滤波电容。该电路的功能与实施方案 A 相同。将 Cfilt_d 设置为等于 Cfilt_cm 的 10 倍,只需扫描一个变量并保持 Cfilt_d 和 Cfilt_cm 的相对大小,即可更轻松地进行参数分析。

为了模拟滤波器频率的移动,Cfilt_cm 的参数范围从 1 pF 到 100 nF(Cfilt_d 的参数范围从 10 pf 到 1 F)。在坏情况下,相位裕度永远不会低于 70 度,即 300 pF。请注意,R8 必须足够大,才能将反馈环路与滤波器电容隔离。 进一步了解分立差动放大器的实现

图 18随着共模滤波电容的增加,相位裕度的参数分析结果。德州仪器可以通过参数分析 R8 的可接受尺寸。保持输入滤波器 RC 恒定,扫描 R8 和 R9 时的增益将获得相等的比较,确保 R2 和 R8 的总和等于 1kΩ,并且 R2 和 C3 的乘积保持在 7.5e-6。这些规则保留了图 17 中电路的相对尺寸。图 19显示了 R8 和 R9 越来越小的情况下相位裕度的图表。

进一步了解分立差动放大器的实现

图 19随着 RIN2 的减小,相位裕度的参数分析结果显示。德州仪器对于此设计,任何小于 75 Ω 的 R8 值都会产生小于 45 度的相位裕度,这可视为边缘稳定。这表明实施 A 存在潜在缺陷,而实施 B 有助于解决这一缺陷。

两个设计考虑

在比较分立差动放大器的滤波方法时,设计工程师可以降低放大器电路常见实现中出现错误的可能性。在为放大器电路添加输入滤波时,请考虑这两点。

首先,避免将输入滤波电容直接放在 IN– 上,包括输入之间的电容或直接接地的电容。其次,确保 IN– 和滤波电容之间的电阻足够大,以将滤波器的电容负载与反馈环路隔离。