BLDC 驱动器的换向单元分析

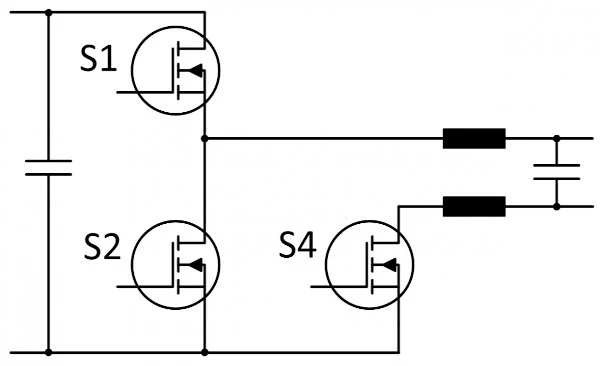

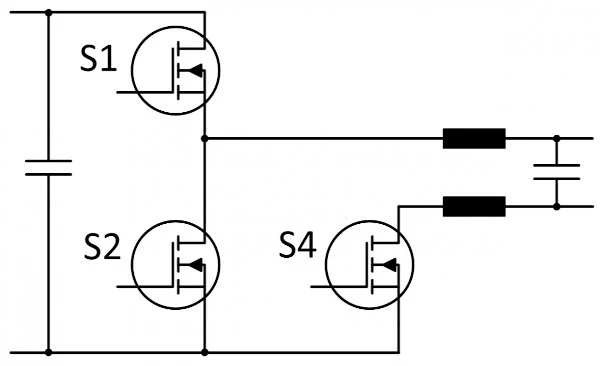

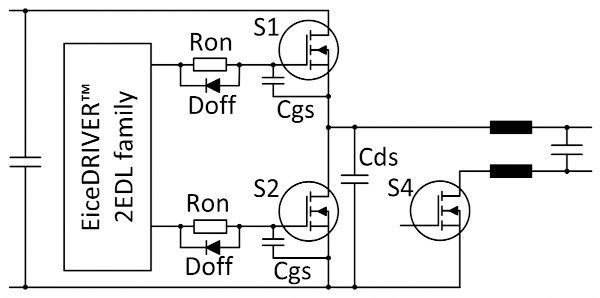

如图 1 所示,半桥单元足以研究所有 FET 的

开关行为。S1 和 S2 以降压配置切换;S4 持续打开以提供返回电流路径。S1 是有源开关,当 S1 打开时,电感电流上升。S2 是整流器开关 — 当 S1 关闭且电感电流下降时,其体

二极管承载电感电流。此操作模式发生在电机周期的三分之一,然后相同的操作移至下一个半桥。MOSFET的开关模式操作会导致高 dv/dt 和 di/dt。 开关单元

图 1:开关单元 MOSFET 的寄生元件、封装、布局和驱动器

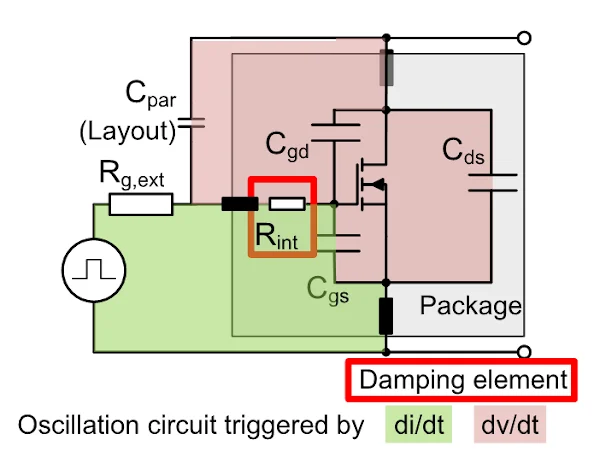

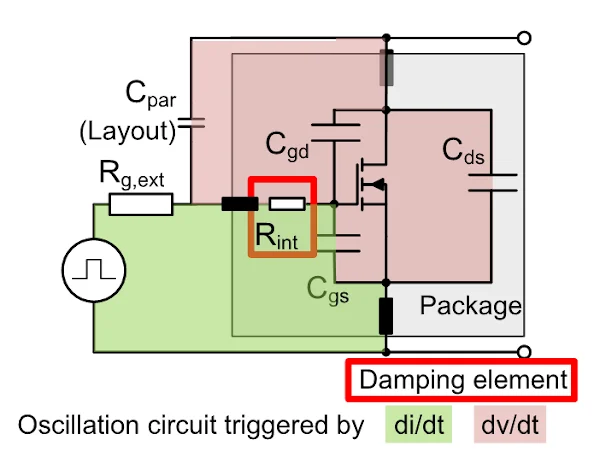

图 2:MOSFET 的寄生元件、封装、布局和驱动器

高 dv/dt 的风险

高 dv/dt 的主要风险是 S1 开启时,S2 两端产生的 dv/dt 耦合到其栅极,并出现电压尖峰。如果耦合尖峰高到足以达到 FET 的栅极阈值电压,则桥中的两个 FET 都会在短时间内开启,从而导致分流电阻或

电解电容器等元件发生故障。

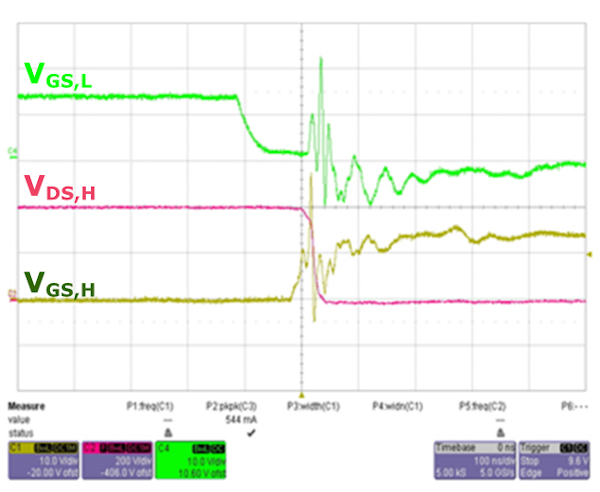

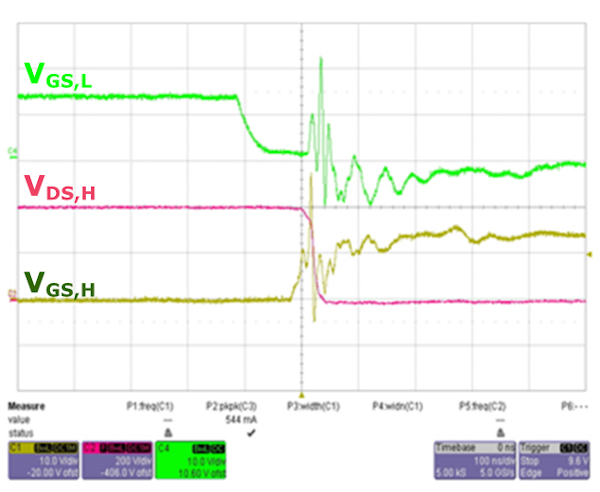

另一个风险是栅极振荡,它可能在导通时触发。高 di/dt 会导致 FET 封装和布局的源极电感两端出现电压降。该电压对驱动电压形成负反馈,导致 FET 栅极产生谐振,如图 3 所示。

此外,关断时的高 dv/dt 可以通过漏极-栅极电容耦合到栅极,从而引起振荡。

这些问题与 FET 的参数、封装和布局寄生效应有关,如图 2 所示。这些问题必须通过栅极驱动器设计来解决。 MOSFET 导通时产生强烈振荡

图 3:MOSFET 导通期间的强烈振荡

dv/dt 的起源和应用效果

dv/dt 发生在反向电容 Crss 的充电期间,如图 2 所示,以电荷 Qgd 表示。因此,Crss 值和充电电流水平是影响 dv/dt 的两个因素。较高的栅极电阻 Rg 值意味着用较低的电流对 Crss 进行充电,从而延长了米勒平台时间并降低了 dv/dt。

MOSFET 体二极管反向恢复期间的电流变化率 dIrec/dt 会在寄生源电感上产生电压,这是对驱动电压的正反馈。它会导致 Crss 充电更快,dv/dt 更高。具有快速恢复行为的二极管会导致更高的 dv/dt。此外,快速恢复行为会增加 S2 上的电压过冲,这是由环路电感引起的。

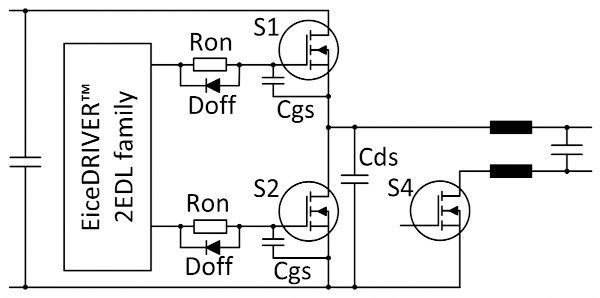

在关断期间,CoolMOSTM CFD2 等超级结 FET 中的非线性电容Coss和高电压 Vds 下的低 Coss 值会导致 dv/dt 增加。这提供了低开关损耗和快速电压转换,但也需要仔细的布局和栅极驱动器设计技术,将更高的 dv/dt 考虑在内。 CoolMOSTM CFD2 建议的门电路设计 图 4 显示了使用 CoolMOSTM IPD65R420CFD 的建议原理图。值得注意的是,在每个桥的开关节点上添加电容 Cds=0.47nF,以限制和线性化 dv/dt。这是防止击穿和共振问题的可靠方法。在电机驱动应用中,典型的开关频率较低,因此添加的电容 Cds 对开关损耗的影响很小。选择其他驱动参数时要考虑:

Ron=1000 Ω:开启速度较慢,稳定期较长,dv/dt 减小。

Roff=0 Ω:关闭时对 GND 的阻抗较低,电压耦合尖峰较低。

Cgs=0.47nF:降低 Crss/Ciss 比率,降低漏极-栅极或米勒耦合增益。

Cds=0.47nF:导通时控制/线性化 dv/dt,这有利于消除栅极振荡并降低 EMI。 使用 EiceDRIVER 2EDL 系列的 CoolMOSTM CFD2 建议门电路原理图

图 4:采用 EiceDRIVER 2EDL 系列的 CoolMOSTM CFD2 建议门电路原理图

该电路由 2EDL05N06PF EiceDRIVER IC 驱动。它基于英飞凌的 SOI 技术,具有出色的抗负瞬态电压能力 [3]。集成自举二极管的优异性能可满足高功率密度和性价比的要求。

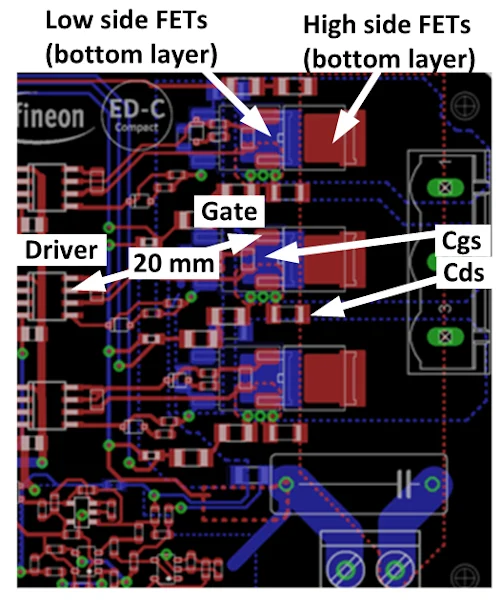

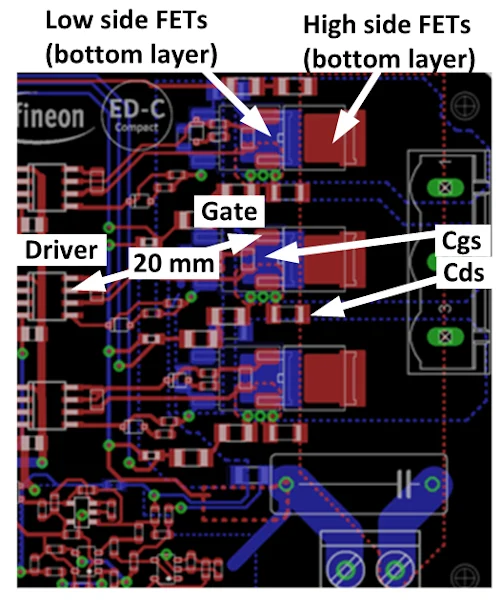

布局建议 通过双面组装化杂散电感的布局示例

图 5:通过双面组装化杂散电感的布局示例

图 5 描绘了一种布局,由于高端源极端子和低端漏极端子之间的距离较短,杂散电感。底层的低端

晶体管相对于顶层的高端晶体管移到了左侧。这导致两个晶体管的热解耦。此外,低端晶体管甚至更靠近各自的栅极电阻。

这种移位还允许低压侧晶体管的漏极端子直接移动到源极端子下方,这样适当数量的通孔就可以提供与高压侧源极端子的紧密连接。因此,环路电感被化。当将低压侧晶体管适当地放置在顶层上时,可以避免双面组装。当然,这会导致更高的面积消耗。

一般而言,建议遵循这些布局指南来降低栅极驱动环路中的噪声和共振:

栅极驱动器尽可能靠近栅极。

外部栅极至漏极电容。

通过适当选择栅极电阻 Rg 来减慢 dv/dt。

将电源地与栅极驱动器地分开。

Rg 尽可能靠近栅极引脚。

在栅极驱动器和栅极之间使用粗走线。

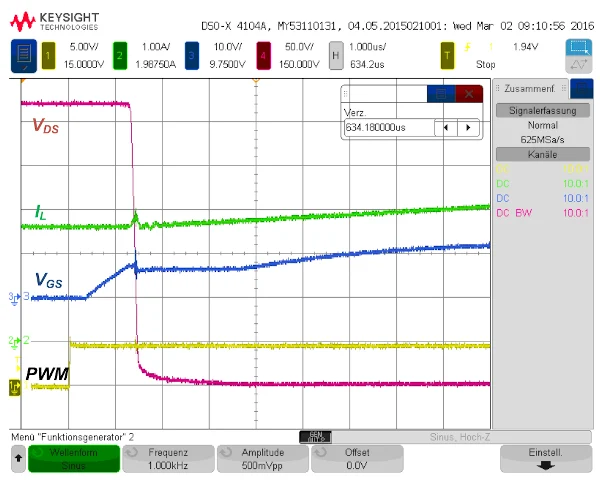

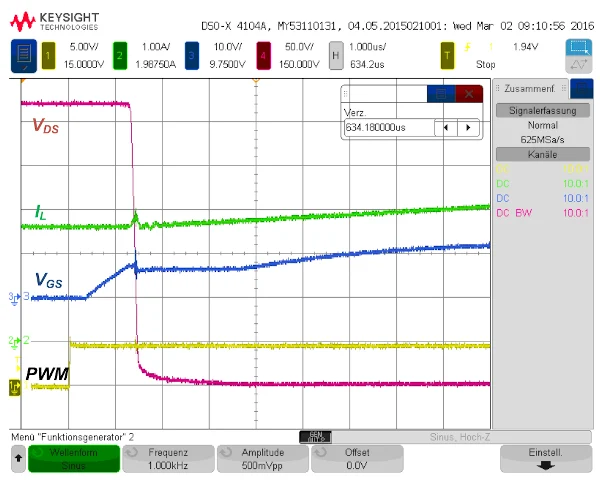

由于栅极设计简单,栅极电阻与栅极端子物理上接近,再加上杂散电感减少,CoolMOS 晶体管的性能得到改善,开关行为也更出色。图 6 给出了建议的驱动电路设计的导通波形。它显示了干净的栅极信号,没有振荡,漏源电压也在米勒平台区缓慢下降至 0V。 直流母线电压 VDC = 320 V 和负载电流 IL = 2.5 A 时的导通波形。VDS(红色,50 V/div)、IL(绿色,1 A/div)、VGS(蓝色,10 V/div)、PWM(黄色,5 V/div)、时间尺度 1 s/div]

图 6:直流母线电压 VDC = 320 V 和负载电流 IL = 2.5 A 时的导通波形。VDS(红色,50 V/div)、IL(绿色,1 A/div)、VGS(蓝色,10 V/div)、PWM(黄色,5 V/div)、时间尺度 1 ?s/div]

如果布局和驱动电路相同,则可以预期另外两个开关桥会有相同的行为。