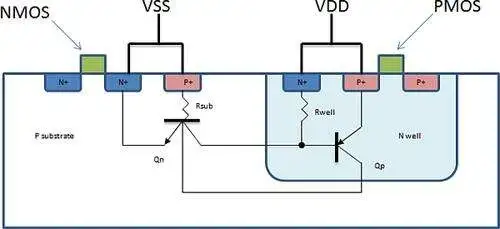

什么原因导致CMOS中的闩锁现象? 要了解为什么会发生闩锁,请考虑图 1 中的简单

逆变器。

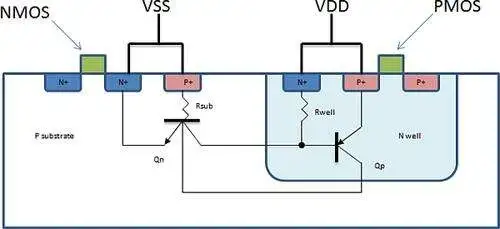

典型的 CMOS 反相器横截面,显示寄生器件。 反相器由两个 MOS

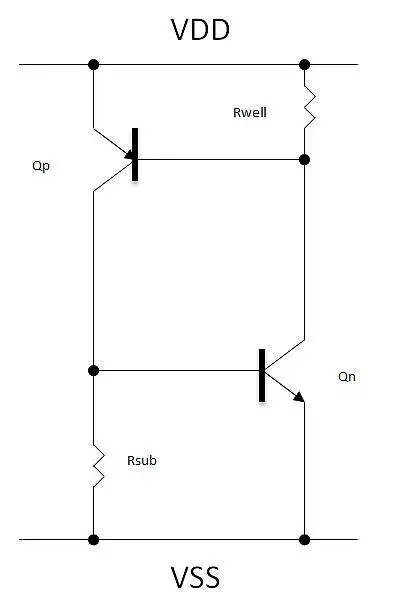

晶体管组成。还放置了阱和衬底抽头,用于将阱偏置到 VDD,将衬底偏置到 VSS,并将阱偏置到 VSS。还有寄生双极管:由 P+/N 阱/P 衬底结形成的垂直 PNP 器件,以及由横向 N+/P 衬底/N 阱结形成的水平 NPN 器件。 图 2 显示了寄生元件的简化示意图。

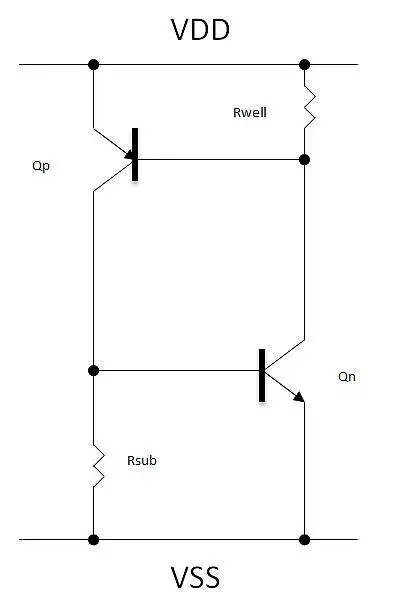

分流电阻 Rwell 和 Rsub 表示从阱抽头到 PNP 基极以及从基底抽头到 NPN 基极的有效电阻。

为了使电路闩锁,必须满足几个条件1。

Qn 和 Qp 的晶体管电流增益乘积必须大于 1,以使结构保持锁存状态。

Qn 和 Qp 的发射极-基极结都必须正向偏置才能启动和维持闩锁。

电源必须能够维持锁存时所吸收的电源电流(保持电流)和电源电压(保持电压)。

上述 CMOS 反相器布局中的寄生器件的简化示意图。

已证明保持电流2强烈依赖于 Rwell 和 Rsub。物理原因很明显:较低的 Rwell 或 Rsub 意味着必须流过更高的电流才能保持基极-发射极结上的正向偏置。请注意,图 1 表示“强”布局,因为衬底和阱抽头位于器件之间;如果它们位于器件的另一侧,则 Rwell 和 Rsub 将增加,电路将变得更加敏感。

如何避免 CMOS 中的闩锁效应

有几种方法可以减少闩锁的可能性:

降低寄生器件的 beta 值。实际上,这可以通过增加器件之间的间距来实现,从而增加横向器件的宽度。然而,这种增加的间距会降低封装密度。

增加阱和衬底掺杂浓度以降低 Rwell 和 Rsub。例如使用逆向掺杂阱。

提供替代的(或更好的)少数载流子收集器。例如在设备周围使用保护环。 实际上,可以采用多种工艺技术和布局技术,例如适当提供阱/

基板抽头和/或保护环。

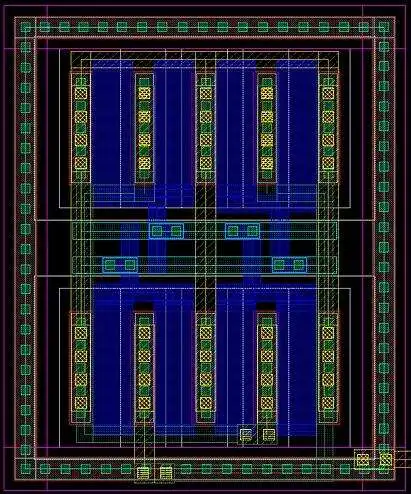

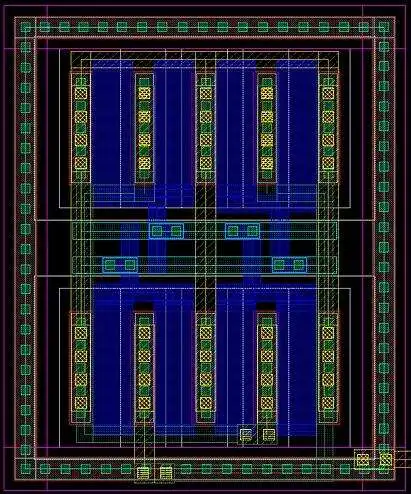

通过自动布局生成工具实现的保护环实现。

图 3 显示了围绕公共质心设备的典型保护环实现。使用约束自动生成保护环可以快速可靠地生成保护环。

典型的 CMOS 反相器横截面,显示寄生器件。 反相器由两个 MOS 晶体管组成。还放置了阱和衬底抽头,用于将阱偏置到 VDD,将衬底偏置到 VSS,并将阱偏置到 VSS。还有寄生双极管:由 P+/N 阱/P 衬底结形成的垂直 PNP 器件,以及由横向 N+/P 衬底/N 阱结形成的水平 NPN 器件。 图 2 显示了寄生元件的简化示意图。分流电阻 Rwell 和 Rsub 表示从阱抽头到 PNP 基极以及从基底抽头到 NPN 基极的有效电阻。

典型的 CMOS 反相器横截面,显示寄生器件。 反相器由两个 MOS 晶体管组成。还放置了阱和衬底抽头,用于将阱偏置到 VDD,将衬底偏置到 VSS,并将阱偏置到 VSS。还有寄生双极管:由 P+/N 阱/P 衬底结形成的垂直 PNP 器件,以及由横向 N+/P 衬底/N 阱结形成的水平 NPN 器件。 图 2 显示了寄生元件的简化示意图。分流电阻 Rwell 和 Rsub 表示从阱抽头到 PNP 基极以及从基底抽头到 NPN 基极的有效电阻。 上述 CMOS 反相器布局中的寄生器件的简化示意图。

上述 CMOS 反相器布局中的寄生器件的简化示意图。 通过自动布局生成工具实现的保护环实现。

通过自动布局生成工具实现的保护环实现。