I 2 C 是一种流行的双向串行通信总线,具有时钟和数据线。两条线路的

驱动器均由开漏接地参考 N 沟道 MOSFET 组成,该 MOSFET 具有连接到 1.8 V 至 5 V

电源的上拉电阻。上拉电阻必须足够小,以便在存在大量总线电容的情况下满足某些时序要求,但足够大,以至于不会超过令人惊讶的弱有源驱动器(指定在标准模式下在 3 mA 时下降小于 0.4 V,在快速模式速度下在 6 mA 时下降小于 0.6 V)电流并且满足逻辑低电平。满足这两种需求可能是一个挑战。

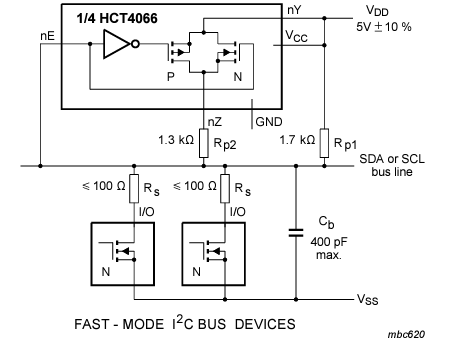

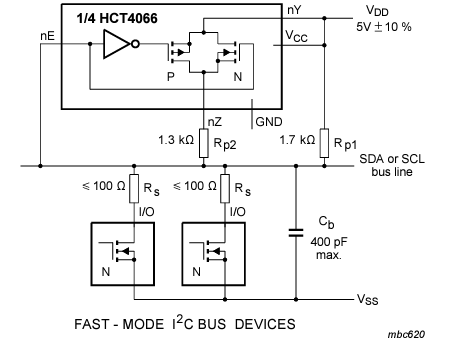

UM10204 I2C 总线规范和用户手册第 7.24 节中的图 44介绍了一种改进方法(图 1)。

图 1:

开关上拉电路,其中模拟开关仅在高总线电压下激活,并与标准上拉电阻并联一个附加电阻。恩智浦

模拟开关仅在较高总线电压下激活,并与标准上拉电阻并联一个附加电阻。这减少了上升时间,而无需提高驱动器可实现的逻辑低电平。但是,当驱动器被激活时,改进的程度受到较高电压下附加电阻的存在的限制——附加上拉太小,并且将超过允许的驱动器电流,并且将无法满足所需的逻辑低电平。更好的方法是仅在信号上升时(即驱动器关闭时)连接附加电阻。这样,驾驶员就不会与额外的上拉力作斗争,因此可以将其做得非常小。这是以下电路所采用的方法。 在图 2中,比较器 U1 和 U2 设置为在典型 1.8VI 2 C 总线的逻辑低阈值和逻辑高阈值处进行切换。

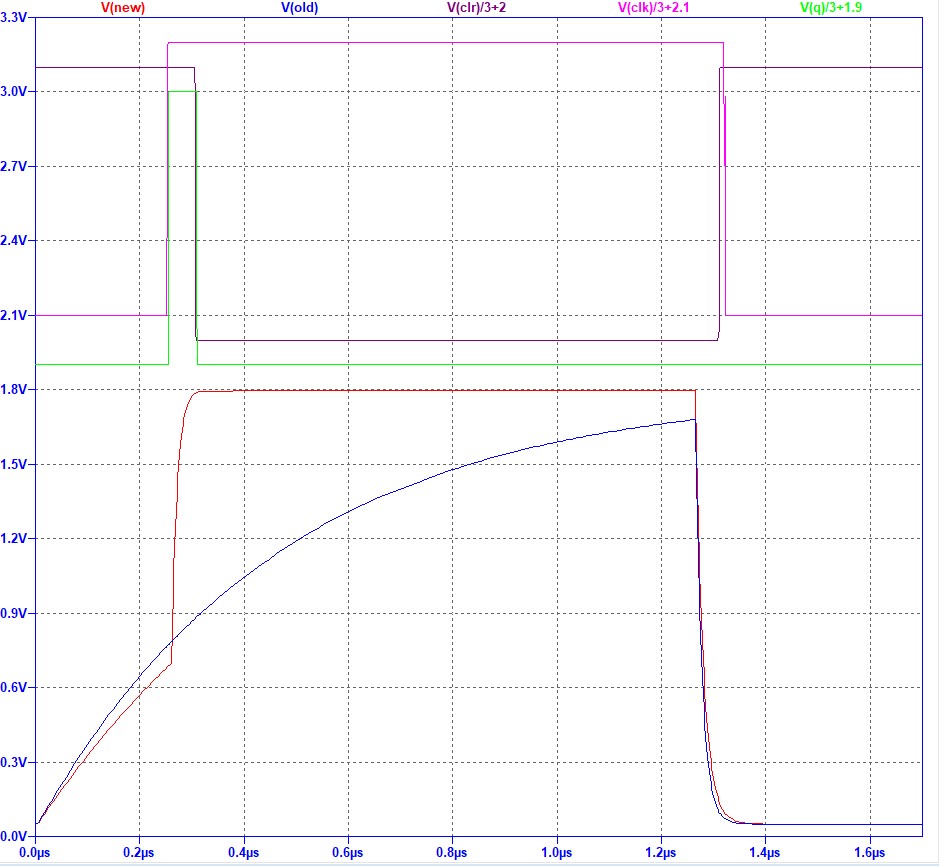

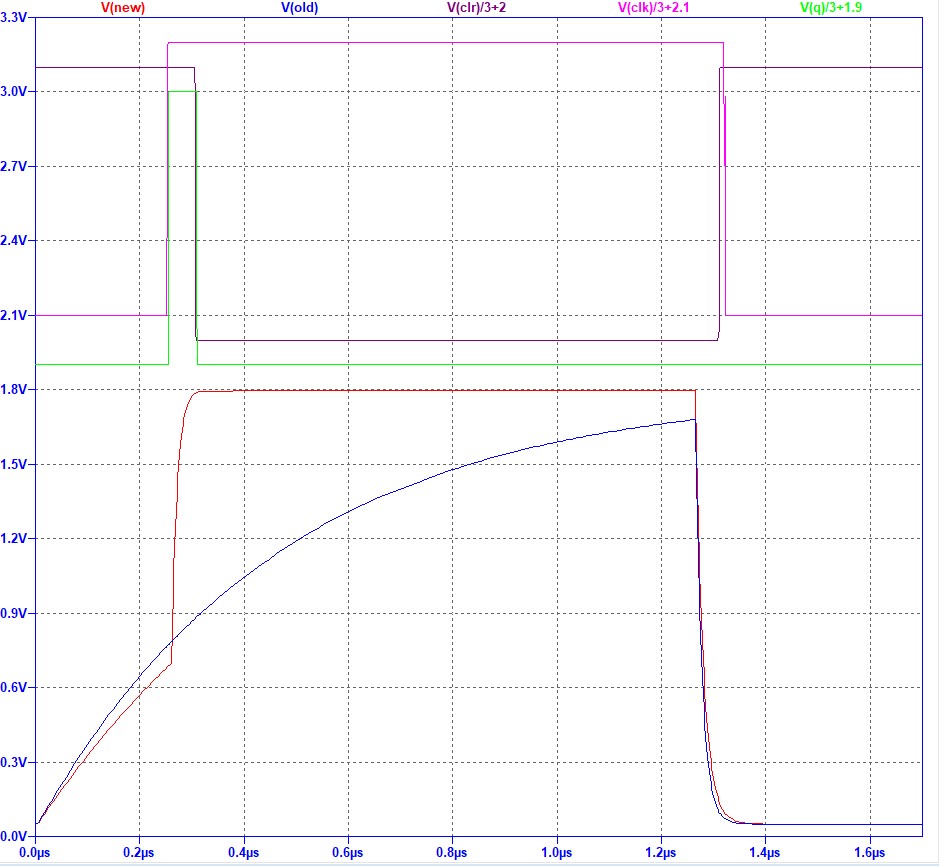

图 2模拟 I 2 C 驱动器、上拉电阻和总线电容的示意图,不带(旧)和带(新)连接到自主非线性上拉电路。 当驱动器关闭并从逻辑低电平释放“新”信号时,该信号将上升至低阈值。U1 存在可接受的传播延迟正输出转换,它将 D 触发器 U3 的 1Q 输出计时为逻辑高电平。这会激活 U4,将 R5 与标准上拉电阻 R6 并联开关,从而大大缩短上升时间。当信号上升到逻辑高电平时,U2 的输出转换为逻辑低电平,清除 U3 的 1Q 输出,停用 U4 并断开 R5。(在这种情况下,传播延迟是值得欢迎的。U2 的延迟允许信号时间达到 1.8V,这得益于额外的上拉电阻。)电路现在已准备好驱动器的下激活,而无需与 R5 进行对抗。在激活之前,电路消耗的电流可以忽略不计。图3显示了与“旧”电路相比,“新”电路的上升时间缩短了,两者都具有相同的总线电容和相同的标准上拉。100 pF 仅是 I 2 C 操作指定值的 25% 。

图 3标准(旧)和增强(新)I 2 C 总线信号的性能比较。为了清楚起见,信号 CLR、CLK 和 Q 在地和 +3.3 V 之间摆动,按比例显示。

尽管 1.8V 是一种流行的总线电压(尤其是对于智能

电池 IC),但我无法找到可以从此电压供电的速度足够快、电源电流足够低的比较器。幸运的是,具有 1.8 V 总线的产品通常提供 3.3 V 电压,并且模拟开关可以很好地弥补两个电源之间的差距。如果总线以 3.3V 运行,则模拟开关可以替换为 PNP

晶体管,其发射极连接到总线电源,其基极通过 3.3k 电阻驱动。万一出现 5 V 总线的情况,5V 可以连接到 PNP 的发射极,但需要找到一个支持 5 V 电源的 D 触发器来替换 U3。