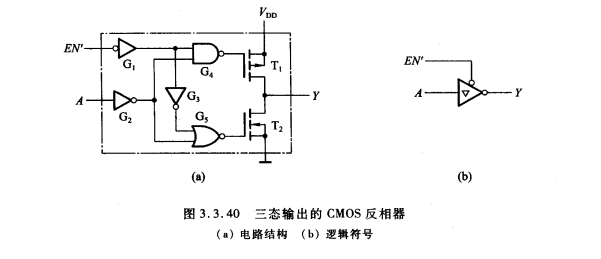

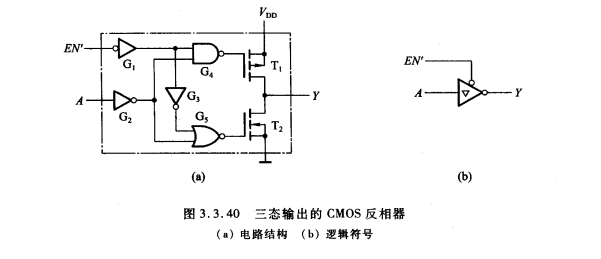

三态输出门电路的输出除了有高、低电平这两个状态以外,还有第三个状态——高阻态。图3.3.40(a)是三态输出反相器的电路结构图。因为这种电路结构总是接在集成电路的输出端,所以也将这种电路称为输出缓冲器(OutputBuffer)。

从这个电路图中可以看到,为了实现三态控制,除了原有的输入端A 以外,又增加了一个三态控制端。EN′。当EN′=0时,若A=1,则G,G的输出同为高电平,T截止、T导通,Y=0;若A=0,则、G、G的输出同为低电平,T导通、T截止,。Y=1。因此,Y=A′,反相器处于正常工作状态。而当EN′=1时,不管A 的状态如何,(G输出高电平而G输出低电平,T和T同时截止,输出呈现高阻态。

图3.3.40(b)是三态输出反相器的逻辑符号。反相器符号内的三角形记号表示三态输出结构,EN′输入端处的小圆圈表示EN′为低电平有效信号,即只有在EN′为低电平时,电路方处于正常工作状态。如果EN′为高电平有效,则没有这个小圆圈。这种三态输出结构有时也用于其他逻辑功能C

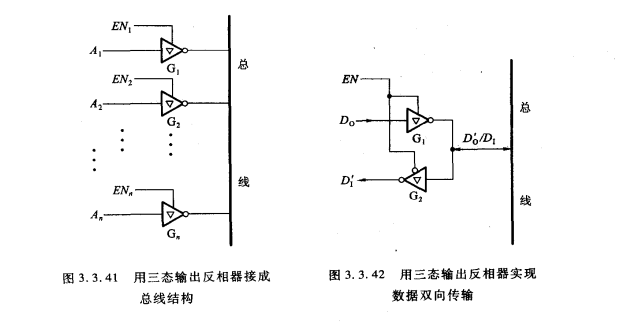

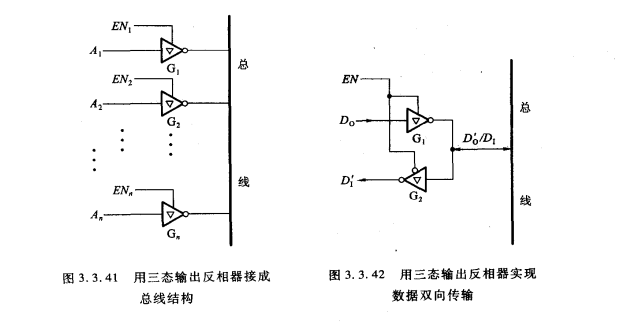

MOS集成电路的输出端。 在一些比较复杂的数字系统(例如微型计算机)当中,为了减少各个单元之间的连线数目,希望能用同一条

导线分时传递若干个门电路的输出信号。这时可采用图3.3.41 所示的连接方式。图中的、G1、G2,.G,均为三态输出反相器,只要工作过程中控制各个反相器的 EN 端轮流等于1,而且任何时候仅有一个等于1,就可以轮流地把各个反相器的输出信号送到公共的传输线——

总线上,而互不干扰。这种连接方式称为总线结构。

利用三态输出结构的门电路还能实现数据的双向传输。图3.3.42 是数据双向传输电路的结构图。当EN=1时,G工作而(G为高阻态,数据D经过G反相后送到总线上去。当.EN=0时,G工作而G为高阻态,来自总线的数据D经过(G反相后送入电路内部。