当谈到不合逻辑的逻辑电路时,我不得不说,当谈到边沿触发的 D 型触发器时,我总是摸不着头脑。这些是当今计算机和数字电子产品中常见的逻辑块之一。这有点像说晶体管是现代常见的元件……

当谈到不合逻辑的逻辑电路时,我必须说,当谈到边沿触发的 D 型触发器时,我总是摸不着头脑。这些是当今计算机和数字电子产品中常见的逻辑块之一。这有点像说晶体管是现代电子产品中常见的组件,但我们中有多少人了解 D 型器件的工作原理

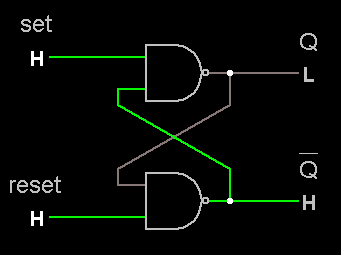

为了开始介绍边沿触发的 D 型触发器,我们将从其内部使用的通用元件开始:SR 触发器。

这是容易理解的触发器,因为它只包含两个逻辑门和与非门。这也是数字电子产品中容易看到的常见问题,即“竞争条件”或故障。当电路的逻辑输出在几微秒内未定义时,就会出现这些状态。我们必须记住,逻辑门毕竟是充满晶体管的模拟电路。这些电路需要时间来使 FET 等器件上的电荷上升或下降。这意味着电压阈值不明确,晶体管可能会或可能不会导通。在门内,这意味着尚未做出有关输出水平的明确决定 - 因此未定义。在输入更改期间也会发生这种情况,因为门需要时间做出反应并生成新的输出(如果需要)。

因此,在我们的 SR 触发器中,在门通电并尝试计算出其输出状态的开关开启时存在竞争条件。当输出反馈到输入时,这变得更加复杂。这意味着输出正在影响输入,从而影响决策,进而影响输出本身。使困惑?嗯,这就是门的感觉。然而,几微秒后,栅极稳定下来并保持稳定状态。

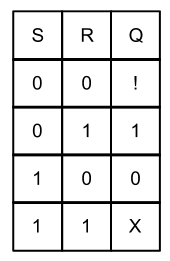

因此,SR 触发器的真值表如下:

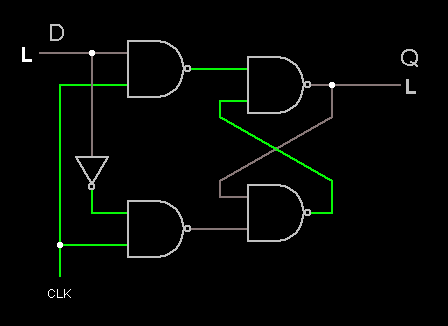

有趣的状态是“设置”和“重置”状态以及“不执行任何操作”状态,因此请记住这些状态以供稍后使用。接下来要添加的是时钟输入,这是通过在 SR 电路的前端添加两个 NAND 门来完成的。这成为门控 SR 触发器。设置和重置仍然像以前一样工作,但顾名思义,它是门控的,因此输出仅在时钟输入为高电平时的特定时间发生。这一切都很好,但是,电路有可能在时钟高电平期间多次改变其输出,这根本不是我们想要的。它还不是D型。然而,通过在 S 和 R 输入之间添加一个 NOT 门并将 S 输入重命名为 D,这个问题很容易解决。

我们的新型 D 型器件的工作原理与 SR 触发器类似,因为可以在时钟期间多次处于高电平时更改输出。我们需要一个仅在时钟沿上升时锁存 D 信号的电路。

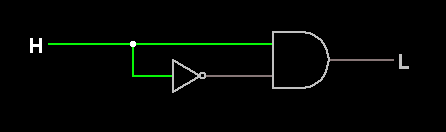

为了简化这一点,首先让我们考虑一下生成竞争条件的能力——或者在本例中是一个故障。如果只有一种方法可以使时钟脉冲在正持续时间内变得非常小,那么就没有足够的时间切换回来。

该电路利用了门开关需要时间的想法。我们假设输入为低电平。与门的一侧根据输入设置为低电平,另一侧设置为逻辑高电平,因为非门已反转输入。在完美的世界中,如果输入发生变化,非门将立即发生变化,与门的输入将交换,而输出不受影响。然而,由于“非”门需要时间来反应并驱动输出,因此实际上,“与”门的两个输入都处于高电平的时间很短。这会引发栅极中的连锁反应,将输出从低电平驱动到高电平。片刻之后,非门输出改变状态,与门对新的刺激做出反应。然而,

这可能看起来不错,但它不是一个定义的时间段——其他门甚至可能对此反应不够快,而我们依赖于门的模拟副作用。所以我们需要的是一个稳定版本的故障发生器。例如,我们可以在某个地方运行一个速度更快的时钟来帮助我们处理信号,但这也需要更高速度的时钟……

然而,答案就在我们初的 SR 触发器中。当应用输入更改时,它们仅对输入更改做出反应。当两个输入均处于低电平时,其中一个输入上的高信号会产生快速反应,并在需要时锁存新的输出。有趣的效果是“什么都不做”条件,其中将两个输入设置为高电平不会改变输出。将输入更改为低电平将设置或重置 SR 锁存器。然而,根据我们的需要上下驱动信号不会影响输出。如果我们将时钟输入连接到该电路,则仅在时钟的下降沿设置或重置锁存器。我们现在已经很接近了,但还没有完全实现。我们有一个响应时钟边沿(错误边沿)的电路,但我们只能连接该电路以使其设置或重置。我们两者都需要。

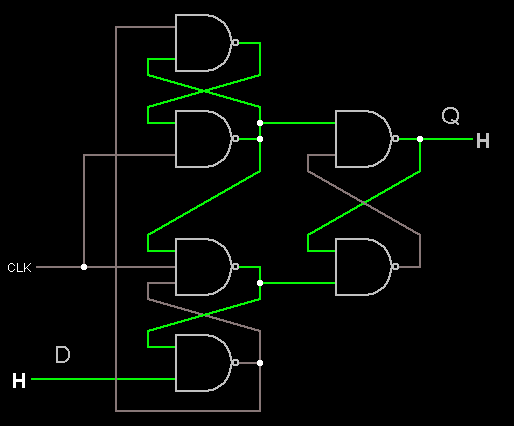

为了同时拥有这两个功能,您需要两个 SR 触发器来充当置位和复位电路。通过以相反的模式连接这些电路,就可以使用数据输入来决定哪一个锁存并保持以及哪一个随时钟输入来回翻转。

首先要注意的是,通过在其中一个 SR 触发器(在本例中为底部触发器)上使用 NOT Q 输出,可以简化 SR 上用于将其转换为 D 类型的 NOT 门。该下部触发器生成该 NOT 信号作为顶部触发器的反馈或输入,而顶部触发器又生成返回到个触发器的 NOT 信号。这会导致两个 SR 触发器以相反的模式锁存。

时钟信号也被馈送到两个 SR 触发器,因此下部触发器需要具有三输入 NAND 门。总体效果是这两个触发器生成非常有用的信号。正如我所说,一个将锁存,另一个将随时钟输入翻转。然后,这两个信号可用于驱动第三个 SR 触发器,该触发器的功能与之前一样,在“不做任何事”条件下,仅在 D 信号发生变化且看到时钟边沿时才更改其输出,在这种情况下,在上升沿。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。