数字电路通常工作在有噪声和电磁干扰的环境中。此外,将现代系统的工作频率提高到 30MHz 以上会导致射频 (RF) 范围内的现象,将数字电路转换为高噪声源。这种噪声通过传输线上的耦合产生,并降低数字信号的质量,从而导致操作错误。

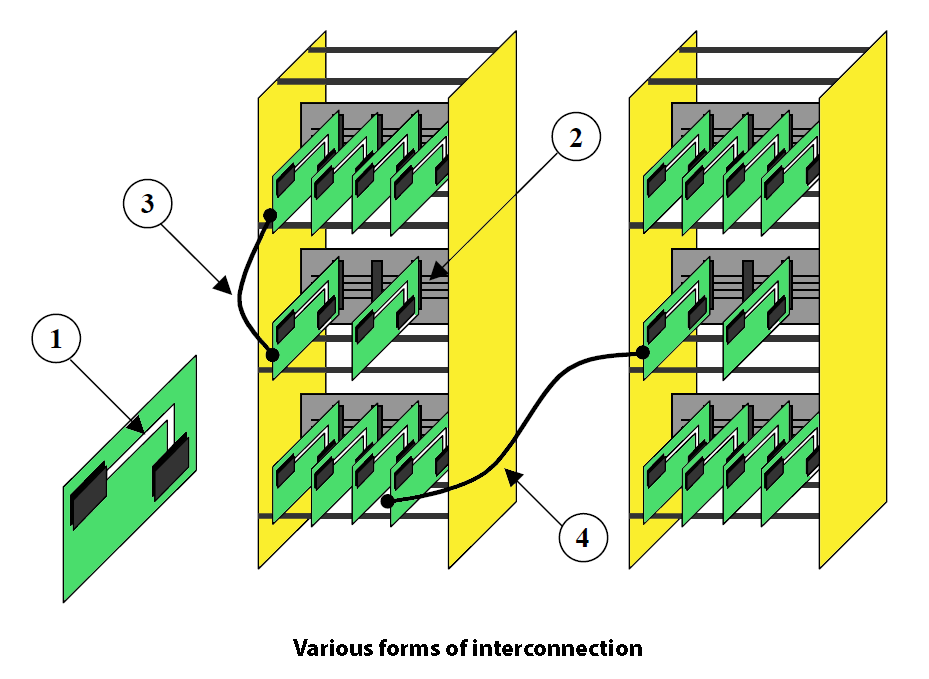

数字信号在同一印刷电路 (1) 上的不同集成电路之间、子系统与基板 (2) 之间、同一系统的子系统 (3) 之间以及不同系统之间的传输过程中(图 5.1)容易受到噪声的影响(4). 为了覆盖更长的距离,数字信号使用调制方法通过网络传输。

多种形式互联

图 5-1

在传输过程中保持数字信号的完整性对于系统的安全运行至关重要。本章分析了现代数字电路中产生噪声的主要原因,并提出了解决这些问题的方法。

在集成电路间的信号传输中,合理电荷的变化所产生的噪声起着特殊的作用。这种噪声是由流向和流出驱动电路的电流引起的,并且会影响传输信号的电平。

随着数字电路速度的增加,在信号传输导体中出现“模拟”现象,如电压前沿反射。这些反射会导致逻辑信道的振荡和错误的信号接收。

在现代数字系统中,各种子系统通过公共通道进行逻辑互连所扮演的重要角色。用于驱动特定特性所需的数字电路的互连通道。

我们将研究相邻信号导体相互作用的影响。这种相互作用是由于寄生电容和电感耦合造成的,是产生噪声的主要原因。

,在一节中,我们将讨论通过一对相同但极性相反的信号进行差分传输的基本原理。差动传输抗噪能力强,适用于长管道。

噪音输出水平

在任何数字电路中,输出级(驱动)在后续电路中起着信号传输的主要作用。与集成电路内部逻辑的其余部分不同,输出级需要在极短的时间内具有特殊的供电或吸收功率的能力,才能成功引出与这些负载相关的负载。

随着现代数字电路速度的提高,输出电平中电流的切换速率也会增加。在高工作频率下,流经输出级的电流的突然变化会产生噪声印象。

在接下来的段落中,我们将看到产生 这种电流的原因 ,它会导致噪声机制和应对方法。

峰值图腾柱电流(交叉电流)

图 5.2 显示了一个典型的 CMOS 输出级。两个晶体管(pMOS 和 nMOS)连接电源线 (V + ) 或接地 (GND) 的输出作为输出值。几乎相同的情况发生在带有双极结型晶体管的输出级电路中。

图腾柱电流峰值

图 5-2

当将输出值从一种状态更改为另一种状态时,两个晶体管都会在短时间内导通。直接影响是直接从电源电压到地的泄漏电流峰值 (I S )的出现。该电流通常称为图腾柱电流,因为它是图腾柱配置中步进晶体管对的特征。

如图 5-2 所示,图腾柱电源的拾取大约发生在输出电压从一种逻辑状态转换到另一种逻辑状态的中间。

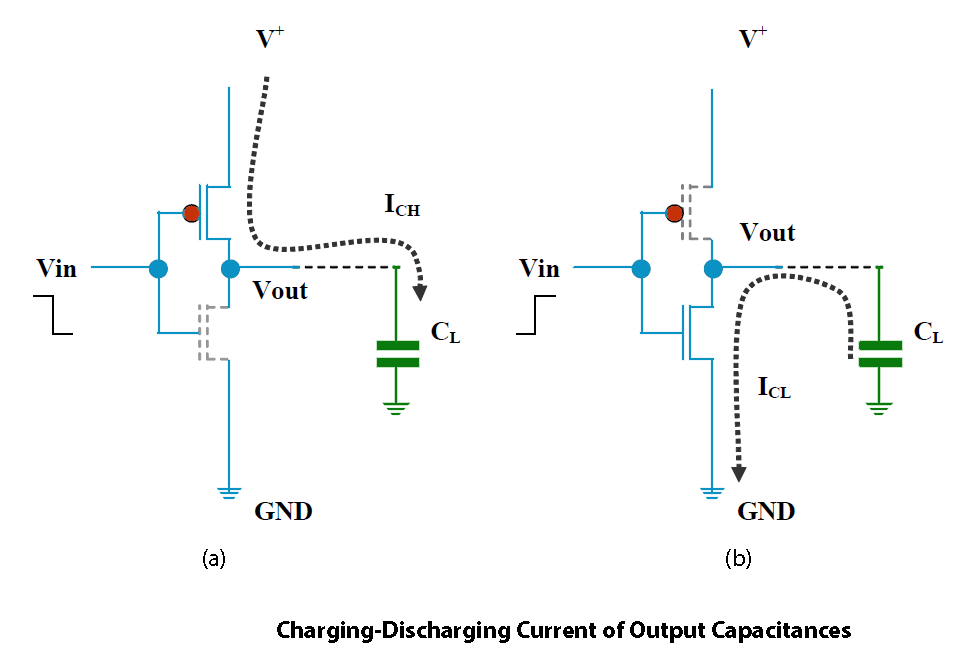

充电电流/放电容量输出

除了将输出从一种逻辑状态切换到另一种逻辑状态时的图腾柱电流峰值外,输出级还流过对内部和外部电容进行充电或放电的电流。内部电容在同一输出级中形成,而外部电容来自连接到输出级的驱动电路输入端的容性负载(每个数字输入呈现 2pF 至 10pF 的电容,具体取决于所使用的技术)。图 5-3 此容量象征性地表示为电容器 C L。

输出电容充放电电流

图 5-3

当将输出从逻辑低电平切换到逻辑高电平时(图 5-3a),电容 C L由电压 V +充电。在从高逻辑电平转换到低逻辑电平的情况下会发生相反的情况:电容 C L通过地放电。流经输出级的电流量由以下公式给出:

Ι CL = C L ( dV / dt )

其中 dV 是高逻辑电平和低逻辑电平之间的电压差。从这个关系可以看出,电容的充电/放电电流与逻辑高电平和低电平(电压摆幅)的差异以及输出电压的速度变化(dt 项化)成正比。

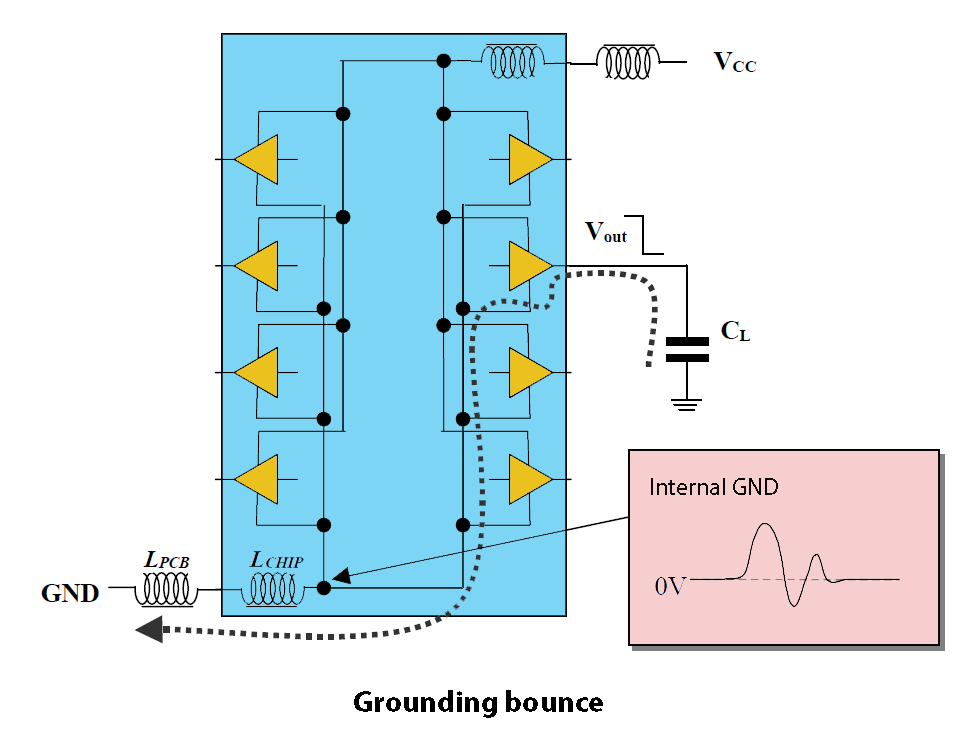

地弹

输出电容充电或放电所需的电流和图腾柱电流都流经接地和电源端子。这些端子,作为集成电路的所有输入和输出端子,在内部二氧化硅表面(裸片)和封装(封装)之间表现出寄生电感。硅表面的每个输入/输出都通过内部框架中的导体(电线)连接,而这又连接到外部端子。界面的每一部分,都呈现出一定的电感值。每种封装类型对每个端子的电感值不同,如表1.5所示:

包装

每个终端的电感

PDIP

13.7nH

PLCC

10nH

SOIC

8.5 毫微

质量标准作业程序

3.6nH

FC-BGA

1nH

表 5-1

寄生电感也出现在连接集成电路端子和中央电源的电路线 (PCB) 中。图4.5中内部电感表示为L CHIP,而电路的电感表示为L PCB。

接地反弹

图 5.4

在图 5-4 的示例中,随着逻辑输出从高电平变为低电平,电流量流向接地端 GND。根据以下公式,该电流流导致寄生电感 L CHIP和 L PCB产生电势 (V) :

V = L ( dI / dt)

该电势暂时将硅表面的内部电压 GND 增加到大于 0V 的水平。一旦电流减少,内部 GND 的波纹就会稳定下来。

这种现象称为地弹(ground bounce),会导致数字电路的运行出错。现代高速电路中的电位差可能超过 1V。

相应地,随着接地反弹的发生,内部电源电压 (V CC ) 会发生成比例的电压变化。但是因为大多数逻辑系列使用接地作为参考电压并且相对于逻辑高电平具有更大的容差,所以在这种情况下反弹 V CC被认为是次要的。

当同时改变同一集成电路的多个输出时,接地反弹特别强,因为它会成倍增加流向/流出接地/电源端子的电流幅度。由于这个原因,产生的噪声通常被称为(同步开关噪声 - SSN)。逻辑输出的同步变化是通过中央时钟脉冲计时的数字系统的主要特征。微控制器系统中同步输出切换的一个典型示例是存储器地址从 0FFFF(十六进制)到 10000(十六进制)的变化。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。