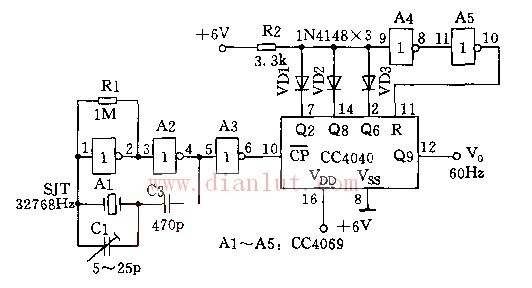

本电路主要用作数字钟的时基振荡源,时基输出频率为60Hz,适用于LED数字钟集成电路,如LM8361一LM8365等。工作原理:如图所示电路是由12位二进制串行计数器/分配器CC4040和六反相器CC4069等构成的数字钟晶振时基电路。

电路中,CC4069的门A1和门A2构成振蔼频串为32768Hz的晶体振荡器。其输出经CC4069的门A3整形后送至CC4040的面端。本电路中,12位二进制串行计数器1分频器集成电路CC4040的输出端只用了Q2、Q6、Q8 、Q9,其它输出端可悬空。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。