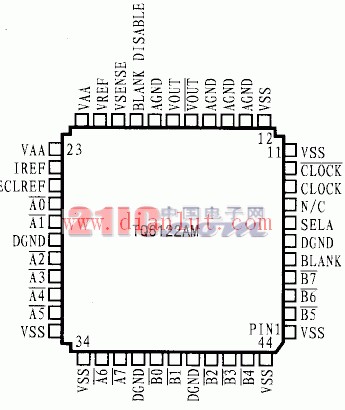

TQ6122的引脚功能

TQ6122的引脚排列图如图所示。各引脚的说明如下(括号中的数字为引脚号):

VSS(1、11、12、33、34、44):-5V数字电源输入端

VAA(22、23):-5V模拟电源输入端

DGND(6、28、37、40):数字地

AGND(13、14、15、18):模拟地。

BLANK(5):该端置高且下降延到达时,内部数据位都被置高。

SELA(7):置高时选择A端数据输入,置低时选择B端数据输入。

A0~A8(26、27等36):数字信号输入端,A7为数据位,A0为数据位。

B0、…… B7(38等):数字信号输入端,B7为数据位,B0为数据位。

CLOCK、 CLOCK(9、10):差分时钟输入端。

VOUT、VOUT(16、17):模拟信号输出端,为差分信号。

BLANK DISABLE(19):如果需要用BLANK端,则连到VAA端,若不需要,则连到AGND。

IREF(24):输入参考电流,直接连接到模拟地,是开关阵列的虚拟电流源。

VSENSE(20):输出判断电压,芯片正常工作时有输出,且VSENSE=-4.2V。

VREF(21):电压基准输入端,一般在其VREF=-4V时,输出的模拟信号峰值为1V。

ECLREF(25):可选的ECL电平参考电压,当数据和时钟为ECL电平时,该脚可不接,此时芯片内部产生电压为-1.3V。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。