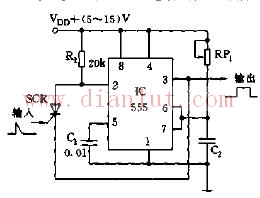

如图所示,555和R1、RP1、C2等组成触发延时电路。平时,由于R1接VDD,使555处于复位状态,即3脚呈低电平;当触发信号到来时,SCR导通,2脚有一低电平信号,使555翻转置位,输出高电平,暂稳宽度为τ=1.1RP1C2。触发后,SCR关断。这种电路可降低对触发脉冲的要求。若用CMOS型555(或556),还可减小触发电流。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。