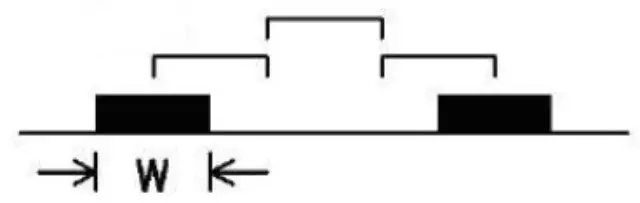

在 PCB 设计领域,3W 原则是一项广为人知的经验法则。它要求相邻信号线的中心间距至少为单根信号线宽度(W)的 3 倍。举例来说,若线宽为 6mil,那么间距就需≥18mil。这一原则的目标是减少信号间的串扰(Crosstalk),进而确保信号完整性(SI)和电磁兼容性(EMC)。

3W 原则是一种防止串扰的方法,但它仅仅作为一种参考,是帮助理解如何防止串扰的一种启发。在实际的 PCB 设计中,3W 原则并不能完全满足避免串扰的要求。根据实践经验,如果没有屏蔽地线,印制信号线之间大于 1cm 以上的距离才能很好地防止串扰。所以在 PCB 线路布线时,在噪声源信号(如时钟走线)与非噪声源信号线之间,以及受 EFTlB、ESD 等干扰的 “脏” 线与需要保护的 “干净” 线之间,不但要强制使用 3W 原则,而且还要进行屏蔽地线包地处理,以此防止串扰的发生。另外,并非所有 PCB 上的走线都必须遵照 3W 布线原则。在 PCB 布线前,决定哪些走线必须使用 3W 原则是十分重要的。

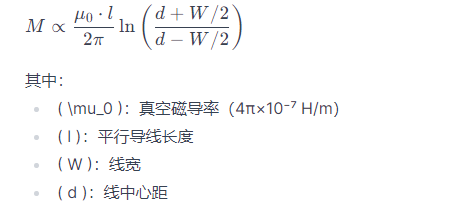

那么,为什么是 3W 呢?首先,从减少电场耦合方面来看,实验表明,当间距达到 3W 时,信号间约 70% 的电场耦合可被抑制,能显著降低串扰风险。为了减少线间串扰,应保证线间距足够大,如果线中心距不少于 3 倍线宽,可保持 70% 的线间电场不互相干扰,这就是 3W 规则。若要达到 98% 的电场不互相干扰,则可使用 10W 规则。其次,在磁场耦合控制方面,3W 间距能有效减小互感,抑制高频信号的磁场干扰。磁场耦合由信号回路间的互感引起,其强度与间距(d)、信号频率(f)、回路面积(A)等因素相关。导线中心距越大,互感越小;高频信号磁场耦合更显著;信号与返回路径形成的环路面积越大,互感越强。互感系数 M 有其简化公式。

,3W 这个数值源于工程实践与电磁场理论,它平衡了布线密度与信号质量的需求。例如,两条走线中间的印制线 3 有一个过孔,这个过孔通常与第三条走线相连,这条走线中可能通过一个易产生电磁破坏的信号,如复位线、音频或视频走线、模拟电路控制走线或者 I/O 接口线等,它将以电感或电容的形式感受额外的电磁能量干扰。为化走线对过孔的串扰,相邻走线的距离间隔必须包括过孔直径和间隙间隔,距离时钟线的 2W 范围内没有其他信号。对富含 RF 能量的走线的距离间隔也有同样的要求,这种走线上的能量可能会耦合到元件的引脚上。

在实际 PCB 的设计过程中,3W 在很多场景下是很难满足的。在实操时,首先要识别出需要走 3W 的信号,像一些高速信号就需要遵循,而一些 GPIO、I2C、UART 等信号其实不需要满足这么宽的间隔。只要不影响到产品正常工作的串扰都是可以接受的,这与产品的实际应用或要求有关。例如,USB3.0 规范中就定义了线缆的串扰,这个串扰还分为了 superspeed pairs 的串扰以及 superspeed 与 D+/D - 之间的串扰。对于一些更高速的总线或者要求更高的总线,串扰的要求会比较复杂,计算的是 ICN(Integrated crosstalk noise)。不过,很多工程师看到相关公式可能会感到困惑。其实,对于串扰而言,在没有特殊要求的情况下,可按照信号幅值或者电源电压大小的 5% 或者 - 26dB 计算,如果信号幅值或者电源电压比较小,则把要求再定紧一些,比如 1% 或者 - 40dB。但具体到实际项目时,还要考虑实际情况,因为串扰不仅与信号传输的结构有关,还与信号本身(激励源的上升时间、激励源与受干扰源的相位等)有关。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。