在众多电子电路中,系统晶振的时钟频率往往处于较高水平,由此产生的干扰谐波能量也较强。这些谐波不仅会通过输入与输出线路导出,还会以空间辐射的形式传播。若在 PCB(Printed Circuit Board,印刷电路板)设计中,对晶振的布局不够合理,极易引发严重的杂散辐射问题,而且一旦出现此类问题,后续很难通过其他手段有效解决。因此,在进行 PCB 板布局时,晶振以及 CLK(时钟)信号线的布局显得尤为重要。

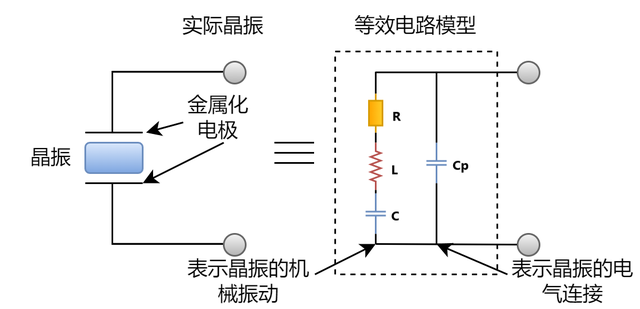

从本质上来说,晶振的作用类似于一个串联的 RLC(电阻 - 电感 - 电容)电路。其等效电路由一个串联的 RLC 电路和一个与之并联的电容组成。其中,串联的 RLC 电路用于表示晶振的机械振动特性,而并联的电容则代表晶振的电气连接特性。晶振振荡器正是基于串联谐振原理进行工作的。

图 1. 晶振等效电路

在这个等效电路中,R 代表 ESR(Equivalent Series Resistance,等效串联电阻),L 和 C 分别为等效电感和等效电容,Cp 则是寄生电容。这些参数共同决定了晶振的电气性能,对电路的稳定性和性能有着重要影响。

晶振在数字电路中扮演着角色,如同数字电路的 “心脏”,其性能直接影响着整个系统的稳定性。可以说,系统晶振的选择和布局合理与否,在很大程度上决定了数字电路设计的成败。

由于晶振内部包含石英晶体,这种晶体较为脆弱,一旦受到外部撞击等情况,很容易发生断裂,从而导致晶振无法正常起振。因此,在进行电路设计时,必须充分考虑晶振的可靠安装问题。一般而言,晶振的位置应尽量避免靠近板边、设备外壳等容易受到外力冲击的地方。在 PCB 对晶振进行布局时,通常需要注意以下几个关键要点:

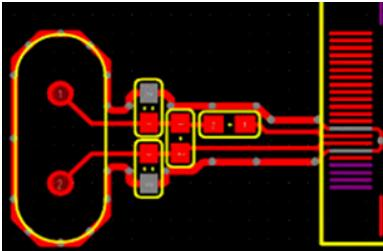

避免靠近板边并确保外壳接地:晶振不能距离板边过近,同时其外壳必须进行良好的接地处理。否则,晶振容易向外辐射杂讯,影响整个电路的正常运行。在板卡设计过程中,这一点尤其需要引起重视。外壳接地不仅可以有效避免晶振向外辐射杂讯,还能屏蔽外来信号对晶振的干扰。如果由于设计限制,必须将晶振布置在 PCB 边缘,那么可以在晶振印制线边上额外布置一根 GND(接地)线,并在包地线上间隔一定距离打过孔,将晶振包围起来,以此增强屏蔽效果。

图 2. 晶振布局靠近板边处理晶振下方避免布线:晶振下方应避免布置信号线,因为这样容易导致信号线耦合晶振的谐波杂讯,进而影响信号的质量和电路的性能。为了防止晶振对其他布线、元器件和层的性能产生干扰,晶振下方应保证完全铺地,并且在晶振的 300mil 范围内尽量不要进行布线操作。

合理布置滤波器件:滤波器件的布置方式会直接影响滤波器的滤波效果。如果滤波器件放置在晶振下方,且滤波电容与匹配电阻未按照信号流向进行合理排布,会使滤波器的滤波效果大打折扣。因此,耦合电容应尽量靠近晶振的电源引脚,并按照电源流入的方向,依照容值从大到小的顺序进行摆放。

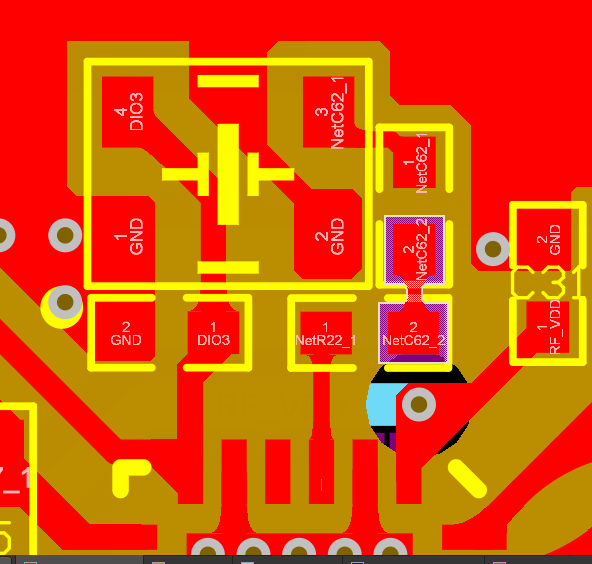

优化时钟信号走线:时钟信号的走线应尽量保持简短,线宽适当加宽。在布线过程中,需要在布线长度和远离发热源之间寻找平衡。以图 3 所示的布局为例,这种布局方式相对更为优化:

- 晶振的滤波电容与匹配电路应靠近 MCU(Microcontroller Unit,微控制器单元)芯片位置,同时远离板边,这样可以减少外界干扰对晶振和芯片的影响。

- 晶振的滤波电容与匹配电阻应按照信号流向进行排布,并且靠近晶振摆放整齐紧凑,以确保信号传输的稳定性。

- 晶振应靠近芯片处摆放,到芯片的走线尽量短而直,以降低信号传输过程中的损耗和失真。

在电路系统中,高速时钟信号线具有的优先级。时钟线是一种非常敏感的信号线路,其频率越高,对走线长度的要求就越严格。为了保证信号的失真度达到,时钟线的走线应尽量简短。

图 3. 晶振优化布局示例

综上所述,晶振在 PCB 板上的布局是一个需要综合考虑多方面因素的复杂过程。在实际设计中,工程师需要充分了解晶振的特性和工作原理,结合电路的具体要求,合理规划晶振的位置和布线,以确保数字电路的稳定性和可靠性。