步骤 1 – 栅极驱动器选择

驱动 GaN 增强型高电子迁移率晶体管 (E-HEMT) 的栅极与驱动硅 (Si) MOSFET 的栅极有相似之处,但也有一些有益的区别。

驱动 GaN E-HEMT 并不会消除任何流行的硅栅极驱动器;它们只是让 GaN 的使用变得更容易、更有效。这意味着高压 (>600V) 准谐振和固定频率反激式适配器、充电器和其他低功耗 AC/DC 控制器可用于 GaN 设计中的不同 LLC 和功率因数校正 (PFC) 配置。

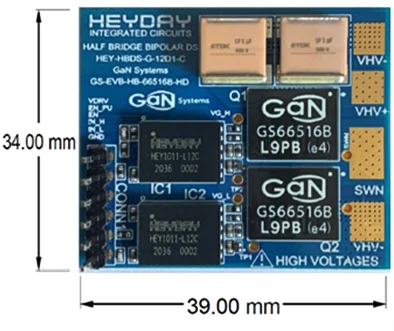

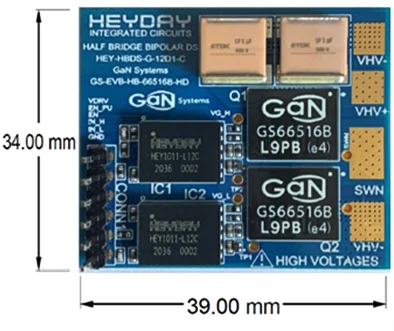

简单的电路提供了将 Si 控制器用于 GaN 器件的转换能力。对于单个 GaN 器件,隔离式负 V GS(OFF) EZDrive 电路是一种低成本、简单的方法,可使用 12V 驱动器驱动 6V GaN 晶体管,可与具有单、双或高电压的任何控制器或驱动器一起使用。 -侧/低侧驱动器。新的驱动器 Heyday HEY1011 可显着减小 GaN 设计的尺寸并节省电路板空间。由于能够消除自举和隔离电源,它也是市场上的隔离栅极驱动解决方案。图 1 显示了使用带有集成电源轨的 HEY1011 的评估板。

图 1. GS EVB HB 66516B HD 是一款 650 V GaN E 模式半桥评估板,采用 HEY1011 L12C 栅极驱动解决方案。图片由Bodo's Power Systems提供

第 2 步 – 拓扑和原理图审查

设计人员需要不断寻找产品,因为使用可用的兼容控制器可以简化 GaN 设计人员的任务。根据所需的拓扑结构,例如临界导通模式 (CrM) 或连续导通模式 (CCM),适当的控制器可能已经存在并且是评估工具的一部分。例如,图 2 所示的 300W GaN 评估演示板中使用的 onsemi NCP1680 CrM 模拟无桥图腾柱 (BTP) PFC 控制器可实现高效率。如图所示,在 (265V) 电压下满负载时实现了 99% 的效率(此外,控制器的设计包括在轻负载下更高效运行的功能。)

步骤 3 – 功率损耗计算 应用简单的计算可以使新手或经验丰富的 GaN 设计人员更轻松地使用新技术。例如,在应用笔记“使用 LTSpice 进行 GaN 开关损耗仿真”(GN008) 中,使用 LTSpice 中的半桥双脉冲测试电路作为测试台来评估不同电参数下的开关性能。在本文中,将模拟的开关损耗与实验室测量结果进行比较,以验证该过程的准确性和适用性。此外,“GaNPX 封装的热行为建模”(GN007) 解释了如何使用 GaN 产品页面上的 RC 热模型通过 SPICE 执行详细的热模拟。应用笔记描述了如何在 SPICE 仿真中使用四层 GaNPX 封装的 RC 模型。使用简单的升压转换器电路来验证 RC 热模型的功能。

第 4 步 – 布局注意事项 由于 GaN E-HEMT 的开关速度比 Si MOSFET 快得多,因此印刷电路板 (PCB) 布局设计需要适当的工程考虑,以尽量减少寄生电感问题。具体来说,寄生电感会导致更高的过冲电压、振铃/振荡和电磁兼容性 (EMC) 问题,从而导致 E-HEMT 承受过大的压力。

应用笔记“GaN EHEMT 的 PCB 布局注意事项”(GN009) 概述了使用嵌入式 GaNPX 封装 E-HEMT 设计的 PCB 布局的工程实践。介绍了以下四种电路配置的布局指南:

用于单 GaN E-HEMT 的隔离栅极驱动器电路

用于并联 GaN E-HEMT 的隔离栅极驱动器电路

半桥自举栅极驱动电路

EZ驱动电路

的电路板布局与低封装电感相结合,使 GaN E-HEMT 能够展现的开关性能。

第 5 步 – 电路测试验证 GaN E-HEMT 具有非常低的寄生参数。然而,如果没有适当的护理,测试设备和测量技术引入的寄生元件(尤其是在较高频率下运行)可能会掩盖 GaN 器件参数并导致错误的测量结果。

应用指南“高速 GaN E-HEMT 测量技术”(GN003) 解释了测量技术的重要性,并提供了多个领域的示例。此外,它还讨论了用于表征硬开关开通和关断的双脉冲开关测试,包括开关测试设置和测试结果示例。 GaN Systems 对我们所做的每项设计以及我们支持的每一位客户定期进行双脉冲测试。没有更好的方法来验证良好的布局。

对于开关能量,描述了可提高 VGS、VDS 和 IDS 测量精度的 Eon/Eoff 测量探测技术,包括 GaN E-HEMT 的开关损耗分布和 Eqoss 测量示例。

步骤 6 – 热设计优化 良好的热设计对于 GaN 晶体管等功率处理器件至关重要。使用绝缘金属基板 (IMS) 代替 FR4 PCB 可以提高热性能。与 FR4 PCB 传热相比,IMS 设计减少了高功率应用的散热器体积。图 3 来自 GN002《封装 GaNPX 器件的热设计》,描述了不同的(越来越好的)冷却技术,包括顶部冷却。如图所示,当使用高性能 GaN 器件(较低的 RθJA 和较低的导通电阻以及并联器件)时,可以实现更低的功率损耗和更高的功率运行。此外,SPICE (LTSPICE/PSPICE) 和 PLECS 模型可以帮助系统设计人员优化热性能和电气性能。

新的 IEC 62368-1 基于危险的产品安全标准(取代 IEC 60950)降低了触摸温度要求,增加了传统热设计的挑战。虽然水平散热器可改善传热,但垂直热传导已变得至关重要。优化的热堆栈可包括先进的 0.2 毫米热界面材料 (TIM)、3 毫米铜屏蔽和 5 毫米铜块,以实现的 RθJA。

步骤 7 – 避免电磁干扰 (EMI) 如果设计中没有妥善处理,长期存在的电力电子问题就是 EMI 和 EMC。一般来说,GaN 技术通过零反向恢复有助于降低 EMI,但控制驱动参数对于控制 EMI 至关重要。此外,建议使用铜屏蔽以符合 EMI 要求。然而,布局是化 EMI 的重要方法,一步重申了步骤 4 中的注意事项。

两种参考设计提出了重要的电路方面,以避免 EMI 问题。其中一款是 65W Type-C USB 供电 (PD) 准谐振 (QR) 充电器,可解决 EMI 问题,符合 CISPR22 传导和辐射 B 类标准。第二个参考设计是一款 100W PFC QR USB PD 充电器,具有两个 C 型端口,具有 EMI 功能,可通过 EN55032 B 类,且余量 >6dB。