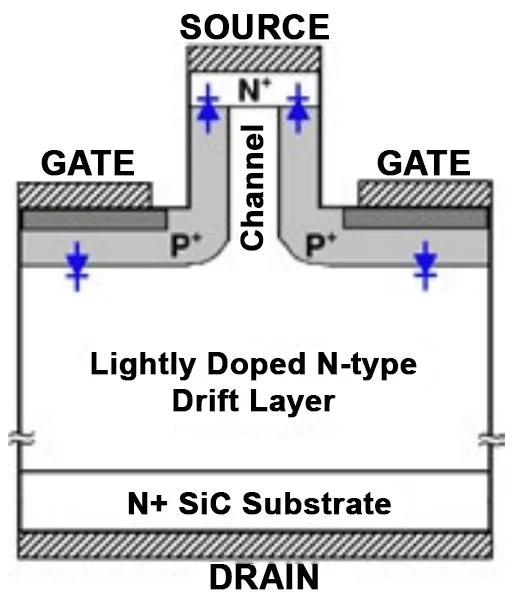

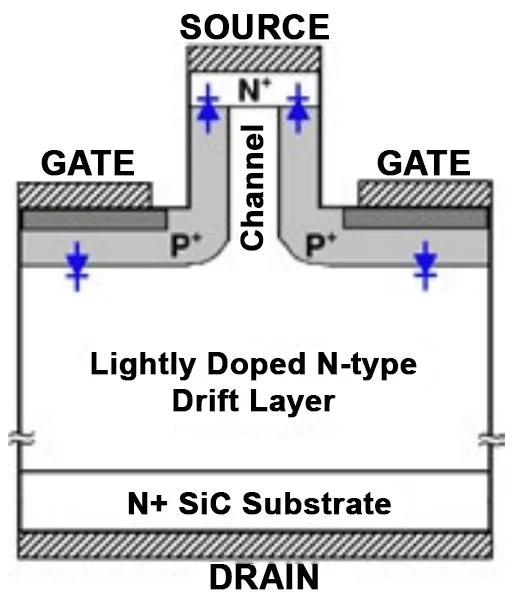

沟槽 JFET 结构

图 1 显示了沟槽 JFET 的单元结构示意图。低导通电阻源自以高单元密度重复的垂直沟道,从而通过沟道和漂移区域在源极和漏极接触之间创建了一条短路径。漂移区掺杂和厚度由所需的额定电压决定。沟槽 JFET 不包含内置体

二极管或任何寄生 NPN

晶体管。其控制沟道由pn结形成,并且是纯垂直的,没有关键的栅极氧化物或任何表面传导路径。如图 1 所示,pn 结二极管形成在栅源区和栅漏区之间。通过控制垂直沟道的开口宽度,可以实现常开型JFET。常通 JFET 的阈值电压 (VTHJ) 通常为 -6V。为了达到额定阻断能力,通常在栅极和源极接触之间施加-15V至-20V的反向偏压[1],这足以耗尽沟道区并在漏极和源极之间形成势垒。如果现在施加漏极电压,JFET 将通过耗尽漂移区来阻止该电压。

SiC沟槽JFET的单元结构

图 1:SiC 沟槽 JFET 的单元结构

在导通状态下,如果栅源电压为0V,则沟道区没有耗尽。从源极到漏极直接存在低电阻电流路径。随着电流增加,沟道漏极侧的电势增加。当漏极和栅极之间的电位差达到 6V 阈值时,沟道夹断并且电流饱和。

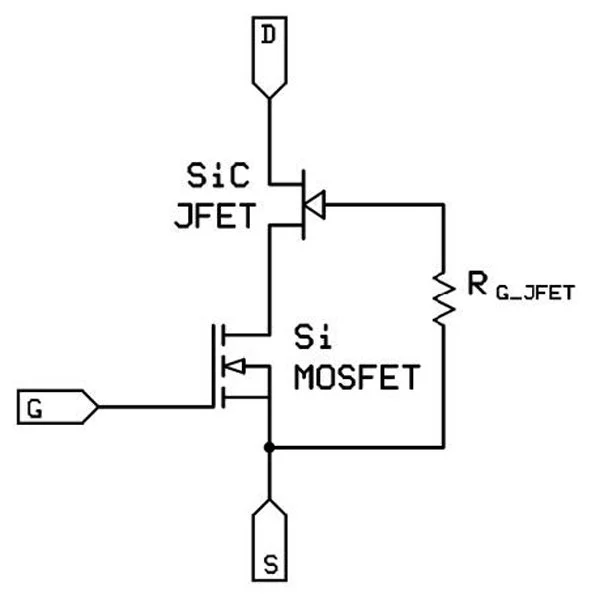

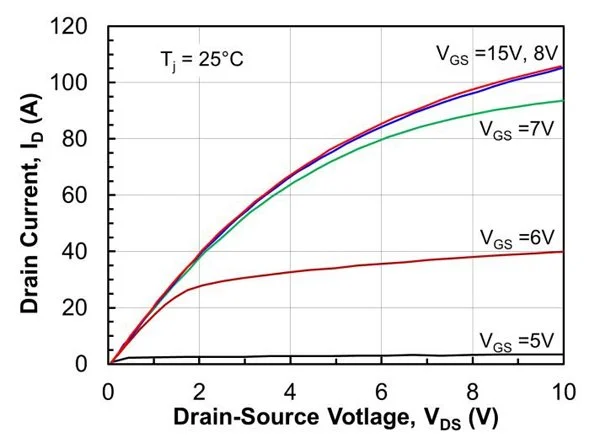

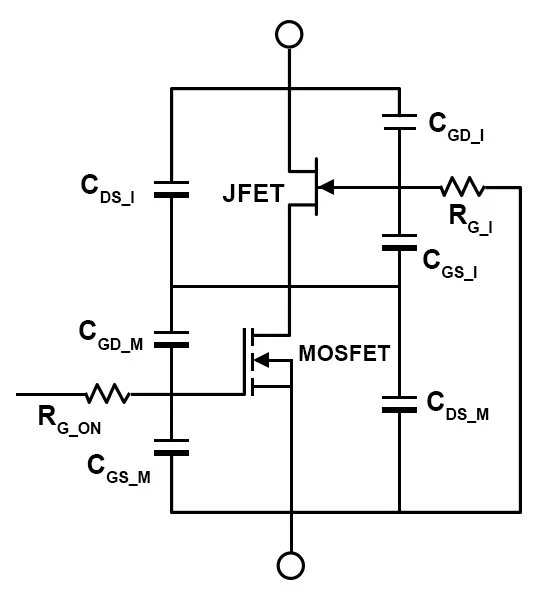

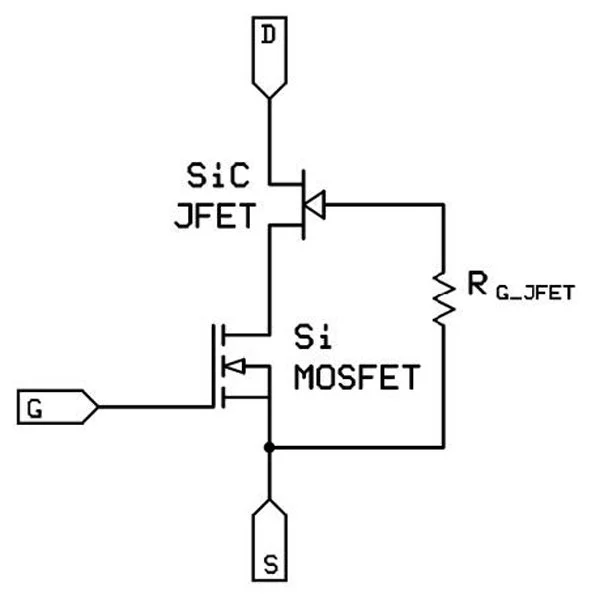

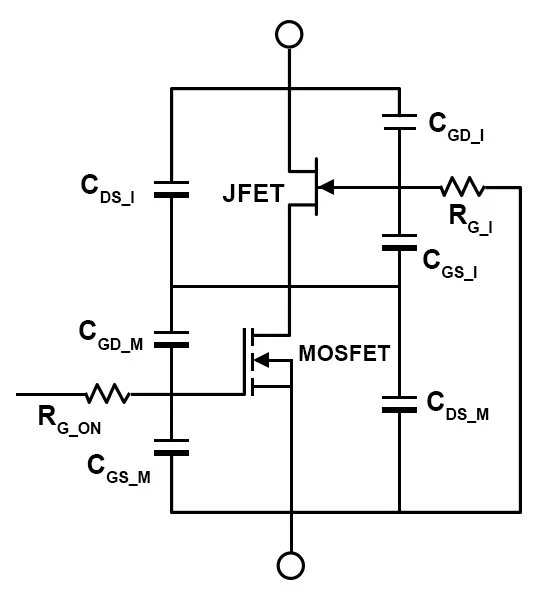

共封装 SiC 共源共栅结构

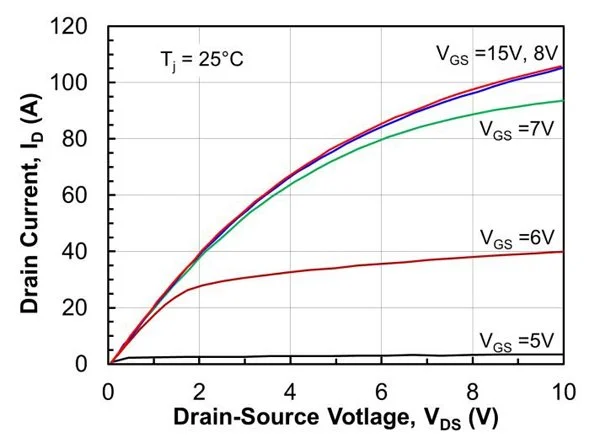

图 2a 显示了共同封装的 SiC 共源共栅结构,其中定制的低压硅 MOSFET 与 SiC 常开 JFET 串联,以实现常关器件 [2, 3]。共源共栅的等效电路如图 2b 所示。图 3 显示了 1200V-60mΩ SiC 共封装共源共栅的典型通态特性。该共源共栅器件的阈值电压 (VTH) 为 4.5V,并且针对高于 10V 的栅极电压 (VGS) 值进行了全面增强。

采用 TO-247 封装的共封装 SiC 共源共栅 (a) 和等效电路 (b)(下)

图 2:TO-247 封装中的共同封装 SiC 共源共栅 (a) 和等效电路 (b)

1200V-60mΩ 共封装 SiC 共源共栅在 25°C (a) 和 150°C (b) 结温下的典型通态特性。 (顶部)

图 3:1200V-60mΩ 共封装 SiC 共源共栅在 25°C (a) 和 150°C (b) 结温下的典型通态特性。

通过打开低压 MOSFET 来打开共源共栅。由于MOSFET漏源压降(VDS)很小(ID*RDS(ON)),因此JFET栅源电压(VGS)在导通状态下接近0V,沟道可以导通。当低压MOSFET关断时,漏极电位上升。 MOSFET VDS 在 SiC JFET 上显示为负 VGS,将其关闭。

电感

开关行为

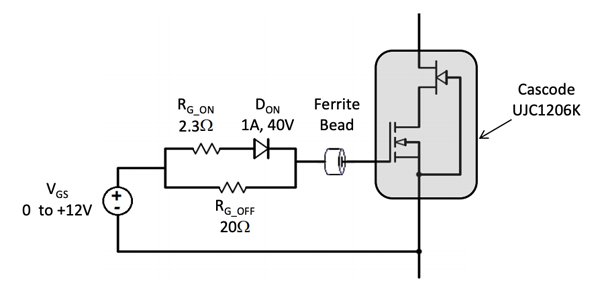

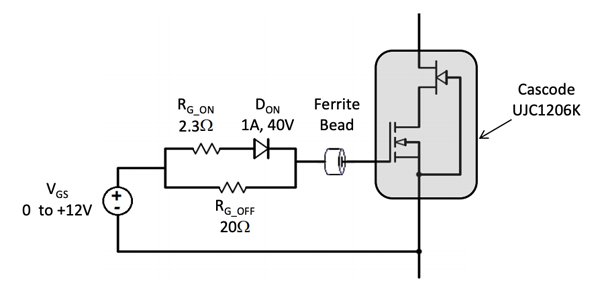

对于共源共栅器件,开通往往比关断慢得多,因此通常推荐的栅极驱动电路使用低栅极电阻进行开通(RG_ON:0-4.7Ω),并使用大栅极电阻用于关断(RG_OFF:10-50Ω),如图 4 所示。可以在栅极引线处使用铁氧体

磁珠以减少振铃。由于 SiC 共源共栅在关断期间可能会出现较高的 dv/dt 和 di/dt,因此需要采用 PCB 布局技术来限度地减少杂散电容造成的栅漏耦合。

为了帮助下面的讨论,为 JFET 定义了称为平台电压的术语 VGPJ:

V GPJ =V THJ +I D /g· mJ (1)

该术语对应于负载电流为 ID 时在栅极充电曲线中看到的电压。其中,gmJ 是 JFET 跨导,V THJ是 JFET 阈值电压。

推荐的 SiC 共源共栅栅极驱动器

图 4:推荐的 SiC 共源共栅栅极驱动

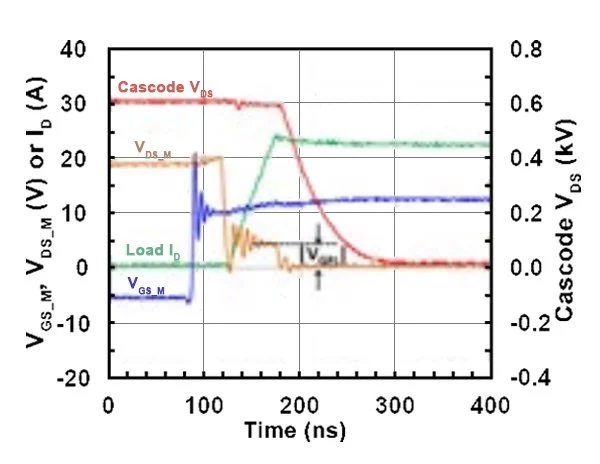

开启:图 5a 显示了 SiC 共源共栅的典型开启波形。导通过程是通过升高 MOSFET 的栅源电压 (VGS_M) 来启动的,然后 MOSFET 的漏源电压 (VDS_M) 下降,JFET 的栅源电压 (VGS_J) 增加,因为 VDS_M等于-VGS_J。 VDS_M 保持在接近 -VGPJ 的值,这意味着 JFET 的 VGS_J 保持在平台电压 VGPJ,该电压刚好足以让 JFET 处理负载电流。 JFET 和 MOSFET 中的电流同时上升。 MOSFET VGS_M 在此阶段仍处于稳定电压。一旦电流达到负载电流(加上恢复续流二极管的任何额外电流),MOSFET VDS_M 就会下降到 ID*RDS(ON),,共源共栅 VDS 下降。

感性负载条件下测得的 1200V SiC 共源共栅开启波形 (a) 和共源共栅等效电路 (b)(下)

图 5:在感性负载条件下测量的 1200V SiC 共源共栅的开启波形 (a) 和共源共栅的等效电路 (b)

导通 di/dt 受到 MOSFET 源极处以及 MOSFET 漏极与 JFET 源极之间的杂散电感的限制。它可以通过与 MOSFET 栅极串联的

电阻器 (RG_ON) 进行良好控制。使用图 5b 所示的等效电路可以更好地理解导通 dv/dt,为清楚起见,其中未包括杂散电感。如果 RG_ON 较小,则 MOSFET 导通速度较快。共源共栅的漏源电压的放电速率主要由JFET的栅漏电容(CGD_J)的放电速率决定,因为JFET具有接近于零的漏源电容(CDS_J << CGD_J)。当电压下降时,负载电流流过 JFET 的导电沟道。通过 JFET 内部栅极电阻器 (RG_J) 的位移电流对 CGD_J 进行放电,并将 JFET 栅极驱动至更负的电位。由于在不阻断沟道负载电流的情况下,JFET 栅极无法被驱动至负值太远,因此 JFET VGS_J 将保持在 VGPJ。因此,通过 RG_J 的电流将根据以下等式设置导通 dv/dt 的值:

(V GPJ - I D *R DS(ON) )/R G_J = C GD_J *dv/dt (2)

这样,可以利用JFET的栅极电阻RG_J来减缓导通dv/dt。另一方面,较低的 RG_J 和较高的 |VGPJ|值(JFET 的负 VTHJ 更大)可用于获得更快的开启速度。

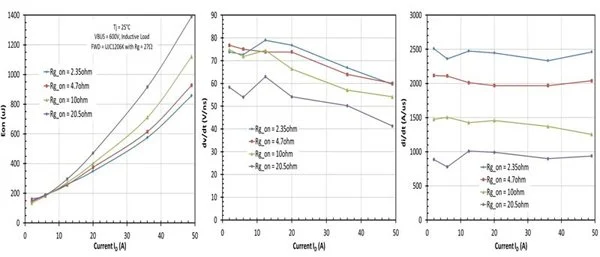

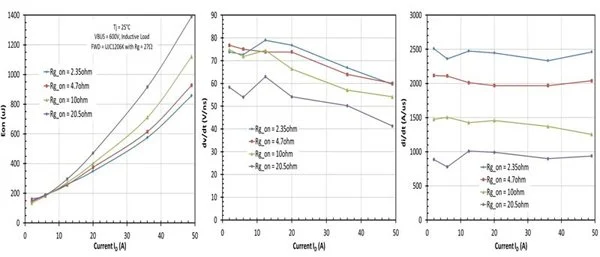

使用与续流二极管相同的器件在 600V 总线感性负载条件下测量 1200V-60mΩ SiC 共源共栅 (UJC1206K) 的开启能量损耗 (a)、dv/dt 率 (b) 和 di/dt 率。

图 6 显示了导通栅极电阻 RG_ON 在导通瞬态期间对 USCi 的 SiC 共源共栅 (UJC1206K) 的能量损耗、dv/dt 率和 di/dt 率的影响。对于较低的 RG_ON 值,dv/dt 由公式 (2) 控制。对于较大的 RG_ON 值,可以通过减慢 MOSFET 漏源电压 (VDS_M) 的转变来控制 dv/dt,这相当于减慢 JFET 的栅极导通电压。

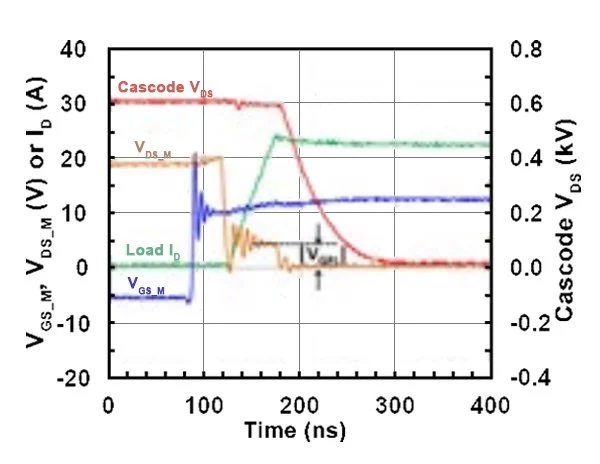

关断:图 7 显示了 SiC 共源共栅的典型关断波形。关断瞬变是通过关断 MOSFET 栅极来启动的。经过一段延迟(由 RG_OFF*CISS_MOSFET 决定)后,MOSFET 的漏源电压(VDS_M)上升。 VDS_M 被钳位到 MOSFET 的雪崩击穿电压,并且在共源共栅的漏极-源极电压上升期间保持在该电压。这会在 JFET 的栅极和源极之间产生负电压以关闭 JFET。由于 JFET 在电压上升期间仍然传导负载电流,因此 JFET 的栅源电压 VGS_J 必须保持在平台电压 VGPJ 以维持该电流。 JFET 的漏源电容 CDS_J 几乎为零,因此流经该路径到达 MOSFET 栅极的电流非常少,这意味着共源共栅的米勒电流非常小。随着共源共栅的漏源电压上升,其斜率 (dv/dt) 再次由通过 JFET 内部栅极电阻 RG_J 的 CGD_J 充电速率决定。可以通过 RG_J 的电流由下式给出:

I G (R G_J ) = {BV (MOSFET) -V GPJ } / R G_J = C GD_J *dv/dt (3)

同样, dv/dt 可以通过控制 RG_J 来限制。通过使用具有较低雪崩击穿电压的MOSFET和具有较大平台电压VGPJ(更负阈值)的JFET,也可以降低关断dv/dt。

一旦共源共栅的漏极-源极电压达到总线电压,电流就会随着 JFET 栅极放电而迅速衰减。放电时间常数取决于 RG_J*CGS_J,并且还会因 JFET 栅极环路中的共源极寄生电感而减慢。图 7 中电流下降期间 MOSFET 的漏极-源极电压由其断态值加上 MOSFET 漏极和源极端子之间的寄生电感引起的电压尖峰来设置。电流斜坡完成后,MOSFET VDS_M 会快速稳定在保持 JFET 关闭所需的电压。

对于较低的 RG_OFF 值,dv/dt 由公式 (3) 控制。对于较大的RG_OFF值,可以通过减慢MOSFET漏源电压VDS_M的转变来控制dv/dt和di/dt,这相当于减慢JFET的关断栅极电压。然而,这是以与 RG_OFF*Ciss_MOSFET 成比例的较长延迟时间为代价的。

用于 USCi 的 SiC 共源共栅的低压 MOSFET 经过定制设计,具有内置电压钳位,以使其在雪崩模式下安全运行。

在器件开发过程中,会进行压力测试,以确保所有采样器件都通过 106 个未钳位电感开关 (UIS) 周期。此外,该 MOSFET 通过了在 150°C 结温下雪崩偏置 1000 小时的老化测试。如图 10 所示,老化测试后观察到的参数变化可以忽略不计。独立 MOSFET 还经过测试,以确保所有采样器件均通过 106 个 UIS 周期。通过这些预防措施,共源共栅可以与低压 MOSFET 一起用作电压钳位,以限制其关断速度。

ZVS 开启行为:USCi 共源共栅的 ZVS 开启行为也不同于其他共源共栅器件,因为沟槽 JFET 的漏源电容 CDS_J 几乎为零。考虑共源共栅电压快速降至零而 MOSFET 仍处于关闭状态的情况。由于 CDS_J 几乎为零,因此所有位移电流都必须流入 CGD_J 路径。 CDS_J 和与 MOSFET 漏极相连的电容 (CGD_M + CDS_M + CGS_J) 之间不存在电压平衡问题,因为后者电容要大得多。这意味着可以避免因高 dv/dt [4, 5] 导致的 JFET 意外导通,从而使 USCi 的 SiC 共源共栅非常适合 ZVS 导通和硬关断应用。

在 150°C 雪崩模式预烧 1000 小时之前和之后测量低压硅 MOSFET 在 25V 时的漏电流 (a)、阈值电压 (b) 和 250μA 时的击穿电压 (c)。