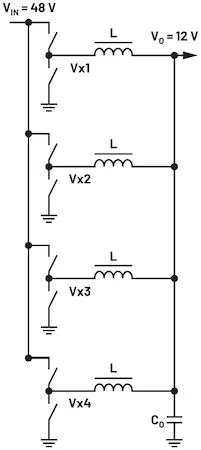

基本 48 V 至 12 V ~1 kW 降压转换器具有四相,具有 6.8 μH 分立电感器和 200 kHz 开关频率。这四个电感器是和的组件,占解决方案体积的大部分。

dILDL=VIN?VOL×DFS×1FOM(D,Nph,ρ,k)(2)

FOM=(1+ρρ+1×1Nph?1)1[(Nph?2×j?2)+j×(j+1)Nph×D?Nph×D×(Nph?2\次j?1)+j×(j+1)Nph×(1?D)]×ρρ+1Nph?1(3)

j=下限(D×Nph)(5)

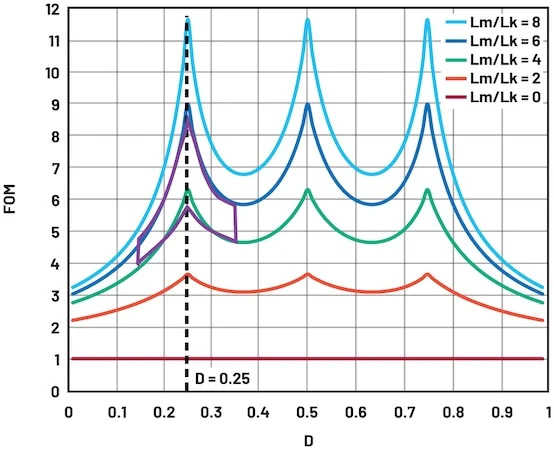

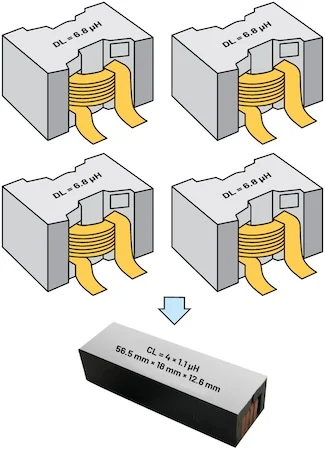

改进的步是针对几个实际合理的耦合系数 L m /L k值绘制 N ph = 4 的 FOM (图 2)。红色曲线 L m /L k = 0 表示分立电感器的 FOM = 1 基线。结果表明,具有非常低泄漏的切口 CL (NCL) 结构通常可以实现非常高的 L m /L k,因此可以获得高的 FOM 值。8,9然而,虽然目标占空比理想地位于个档位 D = 12 V/48 V=0.25,但有必要考虑 V IN和 V O的某个范围。有时,标称 V IN可以是 48 V 或 54 V 加上一些容差,V O可以调整为远离 12 V 等。如果占空比在某个范围内 D = 0.25 左右变化,则为了保持电流纹波,a选择具有显着泄漏的典型 CL 设计而不是 NCL,但仍具有显着的 FOM 值。假设 L m /L k > 4,与 DL 基线相比,图 2 中的 FOM 可以考虑约 6× 的好处,以降低 CL 中的电感值。减少能量存储会直接影响所需的磁性元件的体积。因此,将 DL = 6.8 μH 值降低至 CL = 1.1 μH 应有利于尺寸减小。

图 3 绘制了相应的电流纹波,比较了V IN = 48 V 和 F s = 200 kHz 条件下的基线设计 DL = 6.8 μH 与建议的 4 相 CL = 4 × 1.1 μH (L m = 4.9 μH)。在感兴趣的区域中,CL 的电流纹波与 DL 的电流纹波相似或更小。这意味着所有电路波形的均方根相似,传导损耗也相似。相同 F s下的相同纹波还意味着相同的开关损耗、栅极驱动损耗等,这意味着两种解决方案之间的效率应该非常相似(假设 DL 和 CL 电感器损耗的贡献相似,因为的影响因素是不同之处)。

图 3. DL = 6.8H 和 CL = 4 × 1.1H(V IN = 48 V 且 F s = 200 kHz)时的电流纹波与 V O的函数关系。感兴趣的区域被突出显示。

5 每个 DL 的尺寸为 28 mm × 28 mm × 16 mm,假设它们间隔 0.5 mm:4 相 CL 为 56.5 mm × 18 mm × 12.6 mm 尺寸实现磁性元件体积减小 4 倍。

图 5 显示了完整的 1.2 kW 48 V 至 12 V 稳压解决方案。CL 尺寸和占地面积经过专门设计,可将两个 CL 部件安装在行业标准四分之一砖尺寸内。将所有 ~1 mm 组件(FET、控制器 IC、陶瓷电容器等)放置在 PCB 的底部,可实现 1.2 kW 解决方案的 1/8 砖尺寸。

当 DL = 6.8 μH 电感器更改为 CL = 4 × 1.1 μH 时,电感器中的电流转换速率限制也提高了 6 倍,这始终有助于瞬态改善。除此之外,尽管总磁性元件体积减少了 4 倍,但在 100°C 时,电感器饱和额定值提高了约 2 倍。

图 6 显示了所建议的 V IN = 48 V 解决方案(输出 V O = 12 V)的瞬态性能。正如预期的那样,反馈将输出电压调节至负载电流变化的预设值,从而补偿负载电流的任何变化。输入电压。

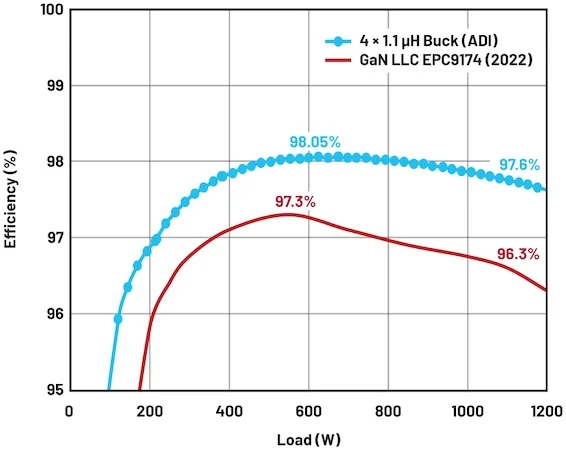

也许重要的性能参数(实现的效率)如图 7 所示。它与的行业解决方案进行了比较:具有矩阵变压器和 GaN 的 48 V 至 12 V(固定 4:1 降压)LLC初级侧和次级侧都有 FET。比较所实现的 97.6% 满载效率和 96.3% 的基准效率。这意味着全功率下的损耗减少了 16.6 W,达到了所提出解决方案的 1.6 倍改进。当效率已经很高时,这种损耗降低通常很难实现。

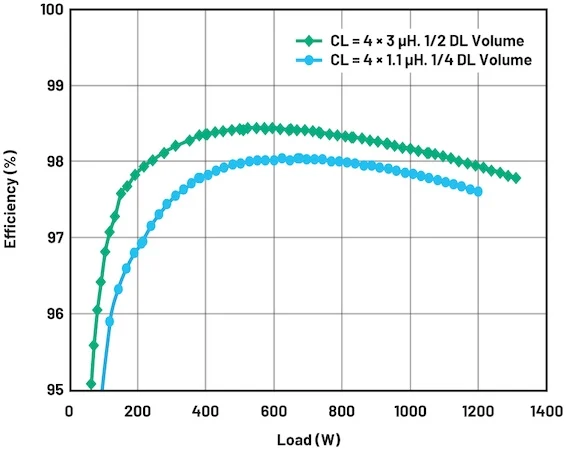

规模和效率之间的权衡当然是可能的。图 8 比较了 CL = 4 × 1.1 μH(与 DL 相比,磁性元件尺寸减小了 4 倍)和更大的 CL = 4 × 3 μH 的效率,而电感器体积仅减小了 2 倍。物理尺寸较大的 CL = 4 × 3 μH 具有较高的泄漏 L k = 3 μH 值和较大的互感 L m = 10 μH。这使得 Fs 可以舒适地降低至 110 kHz,从而在整个负载范围内显着提高效率。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。