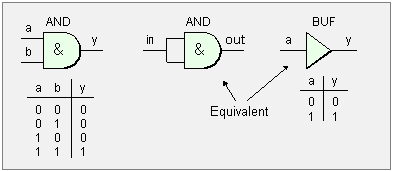

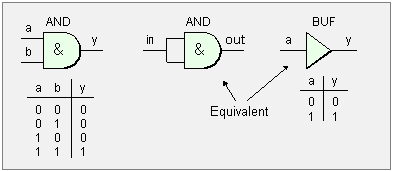

我们可以通过采用 2 输入 AND 门并将其两个输入捆绑在一起来形成一个简单的非反相缓冲门,如图1所示 (我们可以使用 2 输入与门实现完全相同的效果)输入或门)。

1. 使用 2 输入与门实现缓冲门。

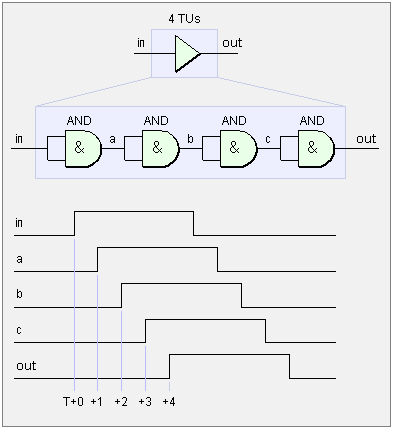

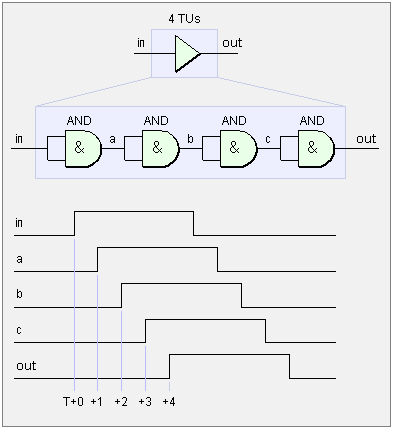

接下来,我们假设每个 NOT、AND 和 OR 门都有 1 个时间单位 (TU) 的输入到输出延迟。出于这些讨论的目的,我们并不特别关心这个时间单位的持续时间是多少——只要一切都是相对的(即使是我的芭芭拉阿姨也是相对的)。因此,如果我们希望在信号中引入四个时间单位的延迟,我们可以使用串联的四个与门链来实现,如图2所示

2. 使用四个串联的与门实现四个时间单位的延迟。

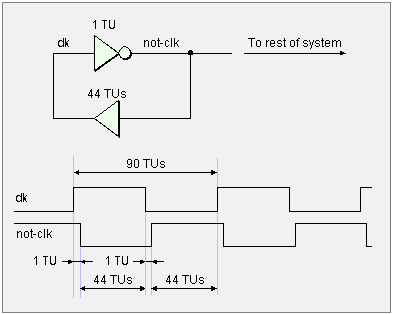

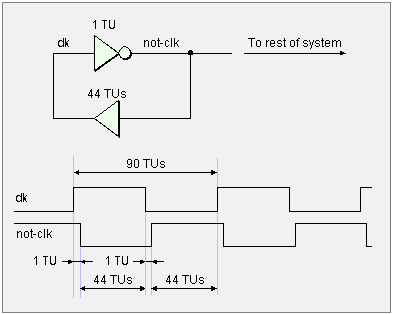

当然,与绘制所有四个与门相比,我们更容易绘制一个带有所需延迟注释的简单缓冲区符号(本例中为“4 TU”)。好的,现在假设我们使用一个非门和一堆与门来构建周期为 90 TU 的简单的时钟发生器(基本振荡器)(图 3 ) 。

3. 创建一个简单的时钟发生器。

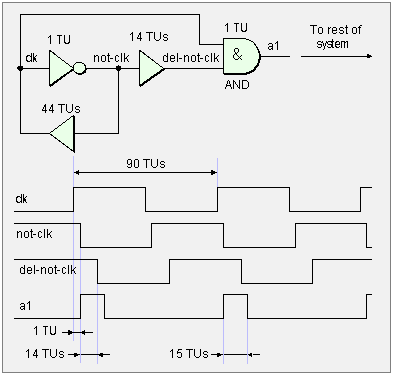

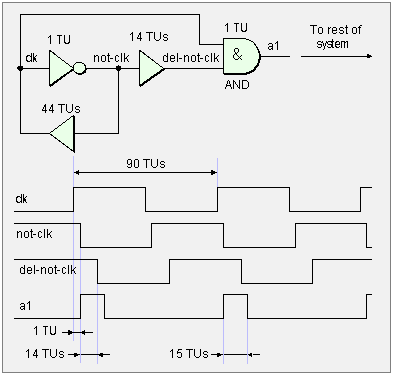

现在假设我们使用 14 个 TU 的延迟元件来增强我们的简单时钟发生器,后接一个与门,连接如图4所示。正如我们所看到的,结果是主时钟发生器的每个周期都会出现一个持续时间为 15 TU 的正向脉冲。

4. 产生脉冲。

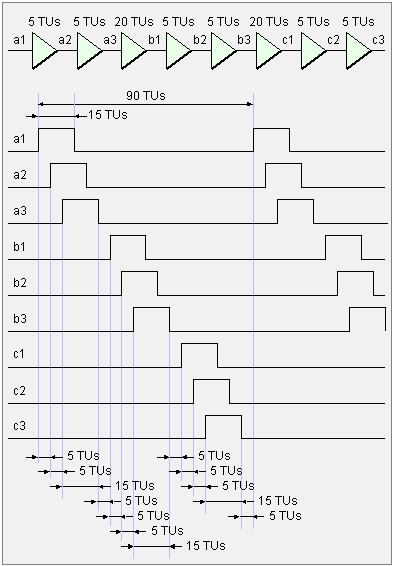

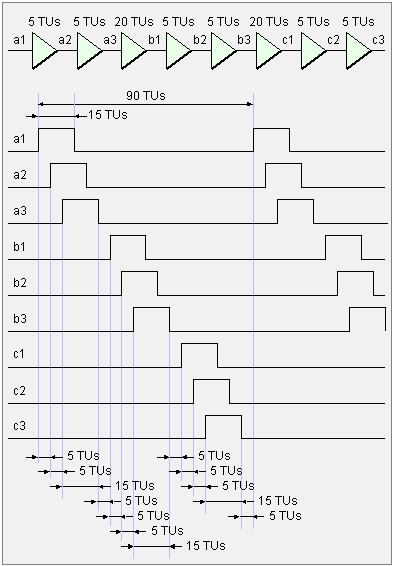

接下来,考虑如果我们将该脉冲输入延迟门链,如图5所示,会发生什么。不要恐慌!这确实不是很复杂。如果您查看与门相关的延迟并将其与这些波形进行比较

5. 将脉冲馈入延迟链。

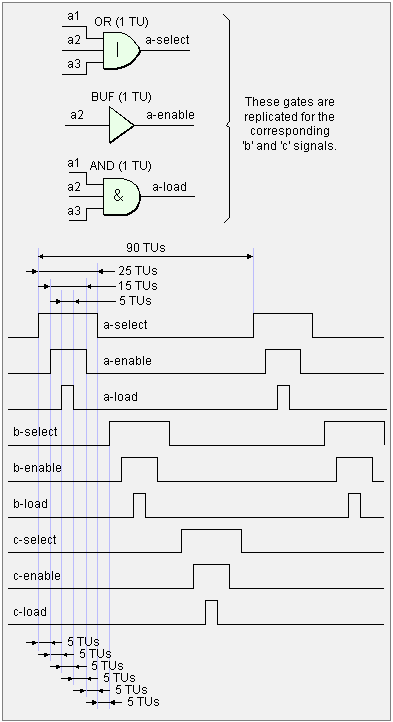

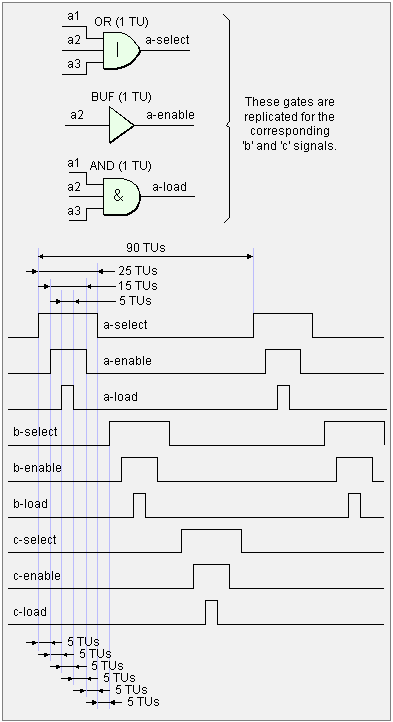

现在让我们开始变得聪明一点。我们将对a1、a2和a3信号进行或运算 以创建一个名为a-select 的信号;我们将简单地缓冲a2 以生成一个名为a-enable 的信号;我们将对a1、a2和a3进行 AND 操作来创建一个名为a-load 的 信号。此外,我们将对b 和c信号执行相同的操作,如图 6 所示。

6. 产生三组控制信号。

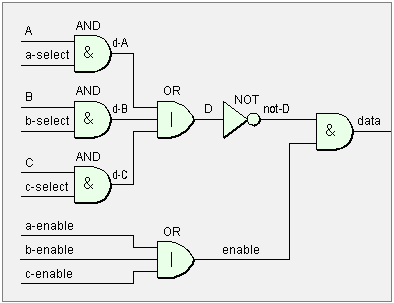

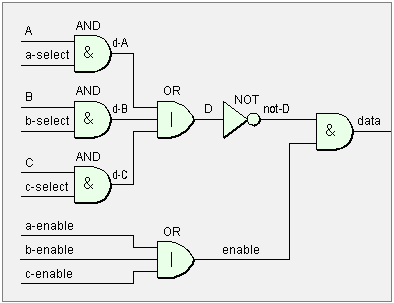

好悲伤!现在我们真的是在热炉子上做饭,请记住——到目前为止,我们只使用了一个非门。但这种情况即将改变,因为我们将创建一个反相多路复用器,如图 7所示。

7. 创建反相多路复用器。

现在,其工作方式很容易理解。从前面的插图中我们知道我们生成了三个不重叠的选择信号,称为a-select、b-select和c-select。我们使用它们分别选择A、B和C输入信号。 (请记住,当我们的选择信号之一为 0 时,与门的输出将为 0;只有当选择信号为 1 时,与门的输出才会反映其相应输入信号的值)。

然后,我们对三个与门的输出进行或运算,生成一个名为D 的单个数据信号,并使用第二个非门反转该信号,形成一个名为not-D 的信号。因此,所有这一切的终结果是我们知道我们的非 D信号将在不同时间携带输入A、B和C 的否定版本 。

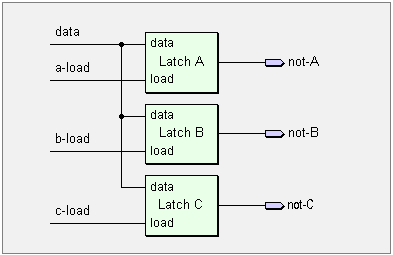

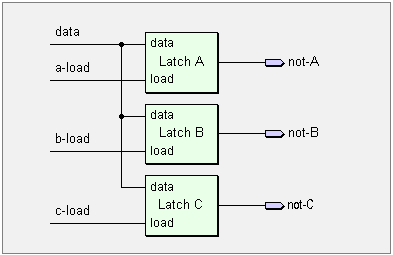

现在,我不知道这是否有必要,但您还会注意到我们使用或门将三个使能信号组合成一个使能 信号,然后我们将该信号与非 D 信号相与。这里的想法是通过将终输出信号(称为数据)强制为逻辑 0 值(除了我们希望实际使用它的时间之外)来防止在称为数据的终输出信号上发生“故障” ,如下所述。 (如果我们终决定希望该信号在我们希望使用它的时候之外被强制为逻辑 1,我们可以通过重新定位终的 AND 门来实现这一点,使其出现在 NOT 门之前;也就是说,使用与门组合我们的D 和使能 信号,然后将与的输出馈入非门。)但并非不重要的一点是,我们获取终的数据 信号并用它来驱动三个锁存器(存储器)的数据输入。元素)。每个锁存器都有自己的“加载”信号,如图 8所示(这些是我们在图 6 中生成的加载信号)。

8. 锁存输入信号的反相版本。

遗憾的是,这就是我的创造力枯竭的时刻。我们需要的是一种构建锁存器的方法,其输入“数据”值将由其“加载”输入上的正向脉冲加载,并且我们需要仅使用“与”和“或”门来完成此操作。你有什么想法吗? (并且您不能使用以下主题中介绍的任何 NOT 门。)

使用四个与门构建一个非门

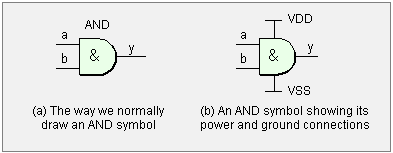

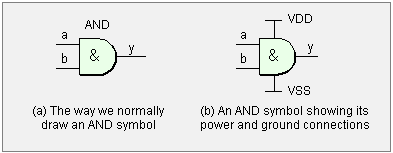

现在,下一个主题真的让我感到惊讶,因为我自己在一千年之内都不会想出这个。一位读者(要求匿名)提出了一种从四个 2 输入与门创建非门的方法。在我们投入争论之前,值得提醒自己的是,虽然我们通常将与门符号显示为仅具有输入和输出数据信号,如图 9a所示,但实际上它还具有电源信号 VDD 和 VSS,如图9b所示 (出于这些讨论的目的,我们假设 VDD = +3.0V 且 VSS = 0V)。

9. 将电源和接地连接添加到 AND 符号。

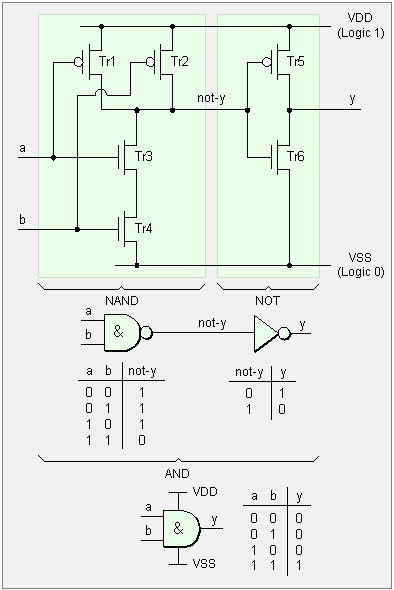

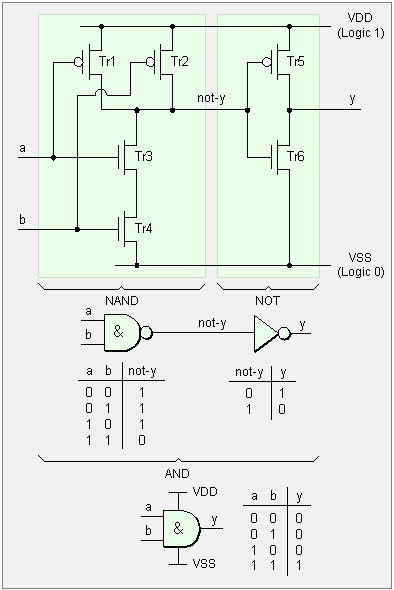

现在你真的不需要知道我们的与门内部发生了什么,但如果你感兴趣的话,它的内部机制如图10所示。对于外行来说,与门实际上是由 NAND 函数和反相 NOT 函数组成的,这对于外行来说可能很奇怪。

10. 与门的内部机制。

晶体管 Tr1、Tr2 和 Tr5 是 PMOS 晶体管(如其控制输入上的小圆圈或“气泡”所示)。这意味着控制输入上的逻辑 0 将打开它们(允许它们通过电流),而控制输入上的逻辑 1 将关闭它们。相比之下,晶体管 Tr3、Tr4 和 Tr6 是 NMOS 晶体管(如其控制输入上没有“bobble”所示)。这意味着控制输入上的逻辑 0 会将其关闭,而控制输入上的逻辑 1 会将其打开。

首先让我们考虑该门的 NAND 部分。当a 和b 输入都为1时,晶体管Tr1和Tr2截止,晶体管Tr3和Tr4导通,因此内部信号not-y 通过晶体管Tr3或Tr4连接到0。输入的任何其他组合导致晶体管Tr3和Tr4之一或两者截止,晶体管Tr1和Tr2之一或两者导通,并且内部信号not-y 经由晶体管Tr1和/或Tr2连接到1。

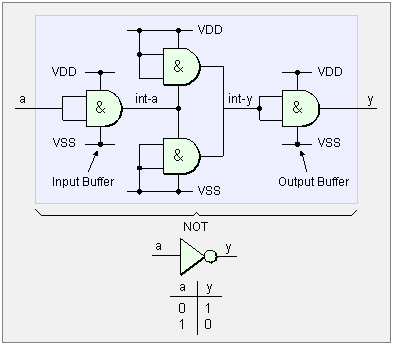

对于该门的NOT部分,当not-y 信号为0时,晶体管Tr5导通,晶体管Tr6截止,并且输出y 经由晶体管Tr5连接至1。类似地,当not-y 信号为1时,晶体管Tr5截止,晶体管Tr6导通,并且输出y 经由晶体管Tr6连接到0。唷!但正如我们所指出的,您实际上不需要理解上述内容即可了解接下来会发生什么。诀窍是采用四个 2 输入与门并将它们连接在一起,如图11所示。

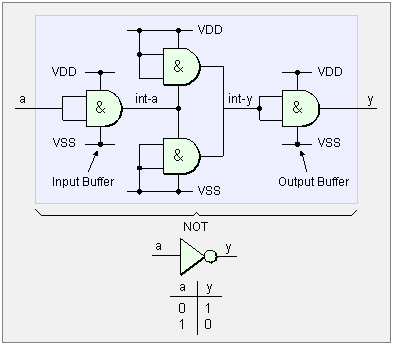

11. 由四个 2 输入与门组成一个非门。

好的,我们假设输入a 呈现逻辑 0。左侧 AND 门充当简单缓冲区,因此其输出int-a 也将为 0。这意味着两个中央 AND 门中的上部已上电,而这两个栅极中较低的一个栅极未通电(其 VDD 和 VSS 电源信号均呈现 0 伏)。

此外,当这些中央 AND 门的上部通电时,其两个输入都连接到 VDD(逻辑 1),因此其输出将 1 驱动到信号int-y上。但并非不重要的一点是,右边的 AND 门也充当一个简单的缓冲器,因此它的 输出y 将驱动 1。

类似地,如果输入a 呈现为逻辑 1,则内部信号int-a 也将为 1。在这种情况下,两个中央与门中的上部没有电源(其 VDD 和 VSS 电源信号均呈现为 1)。 VDD 伏),而这两个栅极中较低的一个现在已通电。当然,当这些中央与门中较低的一个上电时,其两个输入都连接到 VSS(逻辑 0),因此其输出将 0 驱动到信号int-y上。,右边的与门继续充当简单的缓冲器,因此它的 输出y 现在将驱动 0。

但这真的有效吗?好吧,我想确定一下,所以我联系了我在 Xoomsys 的朋友 Simon Young(a href=”https://www.xoomsys.com” target=”_new”>www.xoomsys.com)。 Xoomsys 专门从事令人难以置信的大型模拟仿真,因此这对他们来说是一项微不足道的任务,西蒙很快验证了该电路确实可以工作(它会泄漏筛子,但它确实充当

逆变器)。为了证明这一点,西蒙给我发了一张模拟波形的屏幕截图。在该图像中,从下到上捕获的信号如下:

a (主要输入)。

int-a (控制中间与门电源的输入缓冲器的输出)。

int-y (中间与门的并行输出)。

y (主要输出)。

此外,为了让您高兴和高兴,如果您碰巧可以使用模拟模拟器,Simon 还提供了该电路的SPICE 网表。如果您确实想使用此网表,则必须进行以下几项更改:

更改库定义(或添加包含项,或用于访问特定 MO??S 模型的任何内容)。

更改标称 VDD 电压的 SUPPLY 参数。

您可能还需要对模拟器控件进行一些微小的更改,具体取决于您的 SPICE 风格(我们的版本在 HSPICE 上运行)。